- •Введение

- •Раздел 1 Технологии тестирования и верификации цифровых систем на кристаллах

- •1.1. Современные проблемы верификации систем-на-кристаллах

- •1.2. Моделирование на уровне транзакций

- •1.3. Верификация на основе ассерций

- •1.4. Синтез ассерций

- •1.5. Средства верификации цифровых систем с использованием ассерций

- •1.6. Постановка цели и задач диссертационного исследования

- •Раздел 2 модели диагностирования функциональных нарушений hdl-кода цифровых систем на кристаллах

- •2.1. Введение в тему исследования

- •2.2. Модель процессов тестирования и верификации

- •2.3. Модель поиска функциональных нарушений в программе

- •2.4. Дискретная производная как бинарное xor-отношение

- •2.5. Выводы и рекомендации

- •Раздел 3 методы диагностирования функциональных нарушений

- •3.1. Форма представления модели

- •3.2. Метод векторно-логического анализа столбцов

- •3.3. Метод векторно-логического анализа строк

- •3.4. Матричный метод поиска функциональных нарушений в программных блоках

- •3.5. Выводы и рекомендации

- •Раздел 4 инфраструктура встроенного тестирования функциональных нарушений hdl-кода

- •4.1 Мультипроцессорные решения задач сервисного обслуживания

- •4.2. Мультиматричный процессор анализа бинарных операций

- •4.3. Аппаратная реализация мультиматричного процессора

- •4.4. Аппаратная имплементация инфраструктуры тестирования

- •4.5. Система тестирования и верификации hdl-кода

- •4.6. Выводы и рекомендации

- •Заключение

- •Приложение б. Подробный отчёт синтеза

- •Приложение в. Аппаратная имплементация инфраструктуры тестированиия

- •Приложение г. Документы, подтверждающие внедрение

- •Список использованных источников

1.6. Постановка цели и задач диссертационного исследования

Анализ современных технологий тестирования и верификации цифровых систем на кристаллах, выполненный в данном разделе, дает основания сформулировать наиболее актуальные на рынке электронных технологий проблемы научных исследований, одна из которых может быть сформулирована в виде цели и задач диссертационного исследования.

Цель диссертационного исследования – уменьшение времени верификации и повышение качества ESL-моделей цифровых систем на кристаллах путем введения программно-аппаратной избыточности, реализующей ассерционный граф транзакций, в технологию проектирования, обеспечивающей заданную глубину диагностирования HDL-кода.

Задачи исследования:

1. Разработать ESL-модели встроенного тестирования цифровых систем на кристаллах на основе использования транзакционного графа и механизма ассерций.

2. Разработать векторно-логические методы верификации и диагностирования цифровых систем на кристаллах с применением механизма ассерций.

3. Разработать архитектуру логического ассоциативного мультиматричного процессора для сервисного обслуживания функциональностей цифровых систем на кристаллах.

4. Выполнить имплементацию и верификацию моделей методов и архитектуры процессора, интегрированных в инфраструктуру встроенного тестирования цифровых систем на кристаллах.

Сущность научного исследования заключается в разработке новых моделей и методов тестирования и диагностирования, имплементированных в инфраструктуру встроенного тестирования, интегрированную с промышленной системой Riviera для уменьшения времени верификации моделей цифровых систем на кристаллах при поддержке аппаратных ускорителей на стадиях системного проектирования, что существенно (20%) уменьшает время выхода годной продукции на рынок.

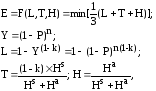

Функция цели представлена повышением эффективности верификации на основе специальных технологических решений, которая определяется минимальным значением уровня ошибок проекта L, времени верификации T и программно-аппаратной избыточности H:

где L – дополнение выхода годной продукции Y, которое зависит от тестопригодности проекта k, вероятности Р существования неисправных блоков и числа необнаруженных ошибок n. Время тестирования и верификации зависит от тестопригодности программного кода k, умноженной на число строк, отнесенного к общему количеству строк проекта. Избыточность находится в зависимости от структурной сложности ассерционного кода, деленного на число строк проекта. Ассерционная избыточность обеспечивет заданную глубину диагностирования ошибок кода функциональности за время time-to-market, определенное заказчиком.

Раздел 2 модели диагностирования функциональных нарушений hdl-кода цифровых систем на кристаллах

Предлагается xor-метрика отношений объектов в векторном логическом пространстве и основанная на ней структурно-аналитическая модель тестирования цифровых систем на кристаллах. Представлены ассерционно-ориентированные модели верификации и диагностирования функциональных нарушений HDL-кода, которые дают возможность существенно уменьшить время проектирования программных и аппаратных продуктов. Показана архитектурная модель мультиматричного процессора с ограниченной системой логических команд для решения задач встроенного диагностирования. Предложены модели диагностирования функциональных блоков HDL-кода SoC, которые отличаются минимальным набором процессов встроенного диагностирования в реальном масштабе моделируемого времени и использованием ассерционного графа транзакций. Модели дают возможность осуществлять сервисы: тестирование функциональных блоков HDL-кода SoC, оценку качества тестов, построение таблицы функциональных нарушений (ФН); диагностирование с заданной глубиной поиска ФН в HDL-коде SoC; восстановление работоспособности кода на основе использования альтернативных решений. Представлены оценки качества HDL-кода SoC для диагностирования функциональных нарушений и восстановления работоспособности программных модулей SoC в реальном масштабе времени.