1.Классификация систем счисления. С/с используемые на ПК.

Ответ:

Система счисления – это совокупность приемов и правил для представления чисел с помощью символов (цифр), имеющих определенное количественное значение.

|

Позиционная система счисления – с.с. в которой количественное значение каждой цифры завит от позиции в числе. (арабская) |

Непозиционная система счисления – это с.с. в которой количественное значение каждой цифры не зависит от ее позиции в числе (римская). |

Системы счисления использующиеся на ПК:

-

Двоичная с.с. – основная, в ней осуществляются арифметические и логические основания информации в устройствах ЭВМ:

d (основание с.с.) = 2; а = 0,1;

-

Восьмеричная:

d = 8; a = 0,1,2,3,4,5,6,7;

-

Шестнадцатеричная:

d = 16; a = 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

8- и 16-ая с.с. – вспомогательные с.с. и используются для предоставления служебной информации.

2.Представление чисел в любой с/с. Перевод чисел из одних систем счисления в любые другие

Ответ:

Представление чисел в любой с/с:

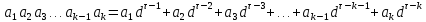

В любой позиционный с.с. любое число имеет изображение:

может быть представлена в виде суммы:

Основание с.с. – это кол-во чисел, используемых в с.с. для изображения числа.

где: k – общее кол-во разрядов в изображении числа;

аi – цифра итого разряда, i – намер разряда;

dƬ-i – вес числа (вес итого разряда);

d – основание с.с.

Ƭ – положение запятой

Перевод чисел из одной с.с. в другую:

-

Перевод целого числа: необходимо последовательно делить число на d2 и получить частные до тех пор пока не получится частное меньше d2.

Последнее частное – старшая цифра в новой с.с., а следующие цифры записываются в обратном порядке получения их.

-

Перевод дробного числа: необходимо последовательно умножать исходную дробь и дробные части, получающихся произведений на основание d2.

Правильная дробь числа в новой с.с. формируется в виде целых частей в порядке их получения.

3.Выполнение основных арифметических операций над числами в различных с./с в прямом, обратном и дополнительных кодах.

Ответ:

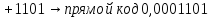

Прямой – для представления отрицательных чисел, а так же для умножения и деления.

Обратный и дополнительный – для замены операции вычитания сложением.

Значения знакового разряда :

0 – для положительных чисел

1 – для отрицательных чисел.

Прямой код двоичного числа совпадает по изображению с записью самого числа.

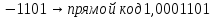

Обратный код положительного числа совпадает с прямым кодом.

Для отрицательного числа все цифры числа заменяются на противоположные.

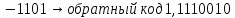

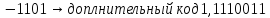

Дополнительный

код для положительного числа

совпадает с прямым.

Дополнительный

код для положительного числа

совпадает с прямым.

Для отрицательного числа образуется путем получения обратного кода и добавлением к младшему разряду 1.

Особенности сложения:

-

В доп. коде возникающая 1-ца в знаковом разряде отбрасывается.

-

В обрат. коде возникающая 1-ца в знаковом разряде прибавляется к младшему разряду.

-

Если результат сложения отрицательное число, то необходимо преобразовать его в прямой код.

4.Способы представления чисел с фиксированной и плавающей точкой. Способы представления символов алфавита и специальных символов.

Ответ:

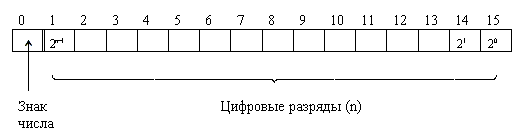

Способы представления чисел с фиксированной:

|

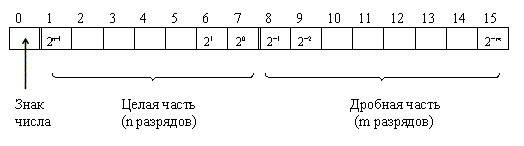

Ячейка с целой и дробной частью:

|

Ячейка с записью целого числа:

|

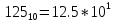

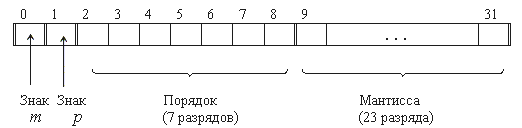

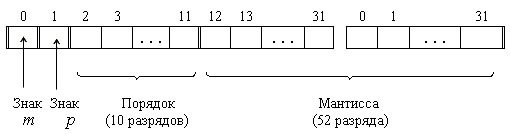

Способы представления чисел с плавающей точкой:

где: q – основание с.с.

p – порядок числа

m – мантисса числа

Для представления числа с плавающей запятой используется полулогарифмическая форма записи числа:

порядок числа - p

Положение точки определяется порядком p.

С изменением порядка точка плавает вправо или влево.

основание с.с. - q

мантисса - m

Представление в машинном слове:

|

Форма полуслово:

|

Форма слова:

|

|

Форма двойного слова:

|

|

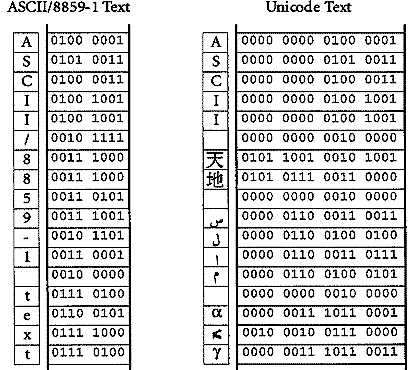

Способы представления символов

алфавита и специальных символов.

Символы храниться в виде последовательностей бит. Для представления символов используются таблицы кодировок.

Кодировка стандарта: ASCII, UNICOD.

5.Базовые логические операции и схемы. Таблицы истинности.

Ответ:

Логический элемент компьютера – это часть электронной схемы, которая реализует элементарную логическую функцию.

Логическими элементами являются: И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и другие, обычно их называют вентилями, а также триггеры.

Логические операции.

Союз: «И» (AND).

Обозначение: «», «&», «».

Таблица истинности:

Союз: «ИЛИ» (OR).

Обозначение: «», «|», «+».

Таблица истинности:

Союз: «НЕ» (NOT).

Обозначение:

Таблица истинности:

|

|

||||||||||||||||||||||||||||||||||||

|

& x xy

y x1 x2 f=x1

x2 |

|||||||||||||||||||||||||||||||||||||

|

1 x xy

y x1 x2 f=x1

x2 |

|||||||||||||||||||||||||||||||||||||

|

x

x f= |

6.Схемные логические элементы ЭВМ: регистры, вентили, триггеры, полусумматоры и сумматоры. Таблицы истинности RS-, JK- и T-триггера.

Ответ:

Вентили – комбинированные связи. И-НЕ, ИЛИ-НЕ.

Триггер – электронная схема, широко применяемая в регистрах компьютера для запоминания одного разряда двоичного кода. Триггер имеет два устойчивых состояния: «1» и «0».

|

RS-триггер:

|

JK-триггеры:

|

Т-триггеры:

|

|||||||||||||||||||||||||||||||||||||||||||||||||

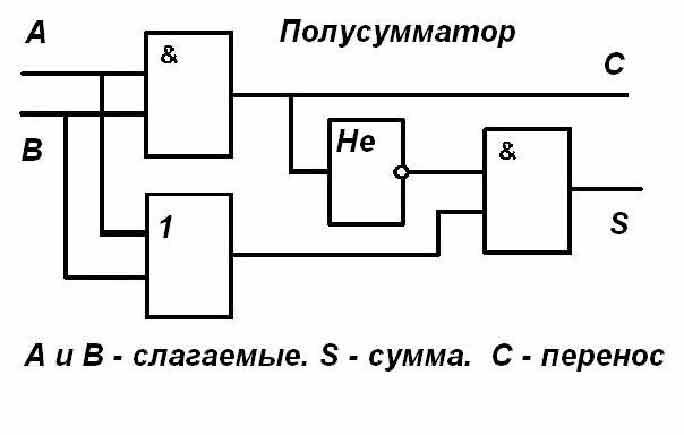

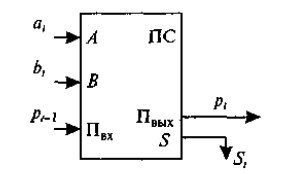

Полусумматор:

При сложении двоичных чисел образуется сумма в данном разряде, при этом возможен перенос в старший разряд.

Сумматор:

Сумматор должен иметь три входа, аi Ьi — слагаемые и рi-1 перенос из предыдущего разряда и два выхода, сумма с, и перенос рi.

7.Логические узлы ЭВМ и их классификация. Сумматоры, дешифраторы, программируемые логические матрицы, их назначение и применение.

Ответ:

Узлы ЭВМ – стандартные наборы логических элементов, из которых набираются схемы, входящие в состав микропроцессоров, блоков питания, контроллеров внешних устройств и пр.

Узлы ЭВМ разделяются на:

-

комбинированные (автоматы без памяти)– узлы, выходные сигналы которых определяются только сигналом на входе, действующим в настоящий момент времени (например: дешифратор).

-

последовательные – узлы, выходные сигналы которых зависят от комбинации входных данных, действующих в настоящий момент времени, и предыдущего состояния узла (счетчик).

-

программируемые – узлы, которые функционируют в зависимости от того какая программа в них записана.

Сумматоры.

Многоразрядный сумматор состоит из полных одноразрядных сумматоров.

Сумматор может быть построен в двух вариантах:

-

последовательный сумматор – комбинированная схема;

-

накапливающий сумматор – последовательная схема.

Последовательный сумматор. Осуществляет суммирование слагаемых и цифр переноса поразрядно, начиная с младшего разряда

Параллельный сумматор. Все разряды операндов суммируются одновременно, но быстродействие снижается за счет времени передачи цифры переноса из младшего разряда. Накапливающий сумматор. Является автоматом с памятью , т.е. слагаемые могут приходить поочередно в произвольные моменты времени и запоминаются в линиях задержки или триггерах.

Дешифраторы.

Схемы предназначаются для преобразования двоичного кода на входе в управляющий сигнал на одном из выходов.

Дешифраторы бывают:

-

Линейные

Все переменные подаются одновременно.

Они обладают высоким быстродействием, но более 3-х переменных падать нельзя.

-

Многокаскадные

Здесь количество элементов в каждом следующем разряде больше, чем в предыдущем. На вход первого каскада подается один слог, на вход следующего каскада — второй слог и результаты конъюнкций, произведенных в первом каскаде

Программируемая логическая матрица (ПЛМ) – это универсальная структура, позволяющая запрограммировать систему булевых функций путем организации связи между вертикальными и горизонтальными шинами. Набор этой связи программируется, в результате программирования логической матрицы (ПМЛ) может реализовать заданную систему выражений. Такая матрица может быть настроена на выполнение любой логической функции определенной сложности.

8.Понятие архитектуры и структуры компьютера. Принципы (архитектура) фон Неймана.

Ответ:

Архитектура компьютера – представление компьютера на общем уровне, включающее описание пользовательских возможностей программирование, система команд, система адресации, организации памяти и т.д.

Структура компьютера – это совокупность его функциональных элементов и связей между ними.

Принципы Фон Неймана.

-

Принцип программного управления.

Программа состоит из набора команд, которые выполняются процессором автоматически друг за другом.

Выборка программы из памяти осуществляется с помощью счетчика команд → Он последовательно увеличивает хранимый в нем адрес команды на длину этой команды. Т.к. команды программы расположены в памяти друг за другом, то тем самым организуется выборка цепочки команд из последовательно расположенных ячеек памяти.

Если нужно перейти не к следующей команде, а к какой-нибудь другой, то используются команды условного или безусловного перехода (ветвления), которые заносят в счетчик команду и адрес памяти, содержащей следующую команду.

-

Принцип однородности памяти.

Программы и данных хранятся в одной и той же памяти, т.е. компьютер не различает что хранится в ячейке памяти.

Над командами можно выполнять те же действия, что и над данными.

-

Принцип адресности.

Основная память состоит пронумерованных ячеек памяти; процессору в произвольный момент времени доступна любая ячейка.

Таким образом ячейкам памяти можно присваивать имена, так что к хранимым в них данных можно обращаться и менять в процессе выполнения программы.

9.Основные компоненты ЭВМ. Основные типы архитектур ЭВМ.

Ответ:

Основные компоненты ЭВМ

I. Центральное устройство.

ЦУ – основная компонента ЭВМ.

ЦУ включает: ЦП – центральный процессор и ОП – оперативная память (главная).

Процессор реализует операции обработки информации и управления вычислительным процессом, осуществляя выборку команд и данных из ОП и запись в ОП, включение и отключение ВУ.

Оперативная память предназначена для временного хранения данных программ в процессе выполнения вычислительных и логических операций.

II.Внешние устройства.

ВУ обеспечивает эффективное взаимодействие компьютера с окружающей средой (пользователи или другие компьютеры).

III.Каналы связи (внутримашинный интерфейс).

Каналы связи служат для сопряжения центральных узлов машины с ее внешними узлами.

Основные типы архитектур ЭВМ:

-

Архитектура «Звезда».

ЦУ соединено непосредственно с ВУ и управляет их работой.

-

Иерархическая архитектура.

ЦУ соединено с периферийными процессорами управляющими в свою очередь контроллерами, к которым подключены группы ВУ.

-

Магистральная структура.

ЦП и блоки ОП взаимодействуют между собой и с ВУ через внутренний канал, общий для всех устройств.

К магистральной структуры относятся архитектура персонального компьютера: функциональные блоки здесь связаны между собой общей шиной (системной шиной).

Магистраль – многопроводная линия с гнездами для подключения электронных схем.

Совокупность проводов магистрали разделены на отдельные группы:

-

Шину адреса,

-

Шину данных,

-

Шину управления.

Периферийные устройства – подключаются к аппаратуре компьютера через специальные контроллеры – устройства управления периферийными устройствами.

Контроллер – устройство, которое связывает периферийное оборудование или каналы связи с ЦП, освобождая процессор от непосредственного управления функционированием данного оборудования.

10.Реализация принципов фон Неймана в ЭВМ.

Ответ:

-

ОП организована как совокупность машинных слов (МС) фиксированной длины или разрядности.

-

ОП образует единое адресное пространство, адреса МС возрастают от младших к старшим;

-

В ОП размещаются как данные, так и программы

-

Команды выполняются в естественной последовательности, пока не встретится команда управления (условного/безусловного перехода, или ветвления — branch), в результате которой естественная последовательность нарушится;

-

ЦП может произвольно обращаться к любым адресам в ОП для выборки и/или записи в МС чисел или команд.

11.Структура процессора. Устройство управления: назначение и упрощенная функциональная схема. Регистры процессора: сущность, назначение, типы.

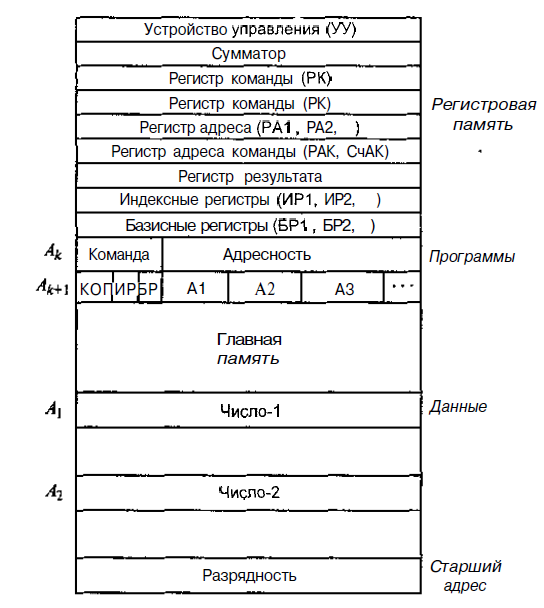

Ответ:

Регистр – устройство, предназначенное для временного хранения данных ограниченного размера.

Сумматор – регистр, осуществляющий операции сложения.

Регистр команды (РК) – размещает текущую команду.

Регистр адреса (РА) – содержит адрес одного из операндов команды.

Регистр адреса команды (РАК, СчАК) – содержит адрес текущей команды.

Регистр результата – содержит результат выполненной команды.

12.Структура команды процессора. Цикл выполнения команды. Понятие рабочего цикла, рабочего такта.

Ответ:

Команда – описание операции, которую нужно выполнить.

Каждая команда начинается с кода операции и содержит необходимые адреса.

Команды бывают: арифметическими, логические, ввод/вывод, передачи данных.

Каждая команда выполняется за один такт.

Цикл процессора – период времени, за который осуществляется выполнение команды.

Рабочий такт – промежуток времени между соседними импульсами тактового генератора.

Цикл выполнения команды:

-

В соответствии со содержимым регистра адреса команд УУ извлекает из ОП очередную команду и помещает ее в регистр команды (РА).

-

Осуществляется расшифровка команды.

-

Адреса помещаются в регистры адреса.

-

Выбираются числа или команды, смещенные в ту или иную сторону по отношению к адресу, указанному в команде.

-

По значения регистра адреса (РА) осуществляется чтение чисел и помещение их в регистр числа (РЧ).

-

Выполнение операции и помещение результата в регистр результата (РР).

-

Запись результата по одному из адресов.

-

Переход к следующей команде.

13.Основные команды процессора: арифметические и логические команды, команды перемещения, сдвига, сравнения, команды условных и безусловных переходов, команды ввода-вывода.

Ответ:

Арифметические: +, -, /, *

Логические: и, или, не

Сдвига: циклические сдвига – то что выходит за границу разрядности, помещается на другой конец в освободившеюся позицию операнда.

Арифметические сдвиги – результат эквивалентен умножению (влево) или делению (вправо) операнда на основание системы счисления.

Логические – при выполнении лог. сдвига биты «выдвигаемые» (вправо) из разрядной сетки теряются, а в противоположную сторону – записываются нулями.

Сравнения: >, <, =, <>, <=, >=

Условного: if …then…else

Безусловного: goto …

Ввода – вывода – команды обмена с периферийными устройствами.

Перемещения – передают слова/байт данных из одной части ЭВМ в другую без изменения.

14.Арифметико-логическое устройство (АЛУ): назначение и классификация. Структура и функционирование АЛУ.

Ответ:

АЛУ – это компонента процессора, выполняющая арифметические и логические операции над данными.

Классификация:

-

По способу действия над операндами:

-

АЛУ последовательного действия – действия производятся друг за другом.

-

Параллельного действия – все разряды операндов обрабатываются одно вменно.

-

По виду обрабатываемых чисел:

-

АЛУ производящие операции над числами с фиксированной и плавающей запятой;

-

Над двоично-десятичными (каждая десятичная цифра в числе записывается четырьмя разрядами двоичного когда).

-

По организации действий над операндами:

-

Блочные – отдельные блоки предназначены для двоично-десятичных чисел, отдельно с плавающей запятой, отдельно с фиксированной запятой.

-

Многофункциональные – одни и те же блоки обрабатывают двоично-десятичные числа, числа с плавающей и фиксированной запятой.

-

По структуре:

-

С непосредственными связями – вход регистра приемника связан с выходом регистра источника операндов и регистра, в котором происходит обработка.

-

Многосвязные – входы и выходы регистров приемников и источников информации подсоединены к одной шине.

АЛУ состоит из регистров, сумматора с соответствующими логическими схемами и блока управления выполняемым процессом.

Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

15.Принципы распараллеливания операций и построения конвейерных структур.

Ответ:

Распараллеливание программ — процесс адаптации алгоритмов, записанных в виде программ, для их эффективного исполнения на вычислительной системе параллельной архитектуры (в последнее время, как правило, на многопроцессорной вычислительной системе).

Заключается либо в переписывании программ на специальный язык, описывающий параллелизм и понятный трансляторам целевой вычислительной системы, либо к вставке специальной разметки.

Для конвейерной обработки данных характерным является:

1)работа с потоками данных (векторами);

2)разбиение операций на подоперации так, чтобы выполнение каждой операции было составлено из последовательности более мелких операций;

3)связь между подоперациями осуществляется только при помощи входных и выходных данных;

4)каждая подоперация реализуется аппаратно, т.е. осуществляется принцип минимизации времени для каждой операции;

5)временные интервалы для выполнения каждой подоперации должны быть примерно равны.

16.Классификация команд. Системы команд и классы процессоров: СISC, RISC, MISC, VLIW.

Ответ:

-

CISC – традиционная архитектура, в которой ЦП использует микрокоманды. Они могут иметь различную длину, метод адресации и требует сложных электронных цепей.

-

RISC – процессор функционирующий с сокращенным набором команд.

Процессоры RISC не патентуются, это способствует их быстрой разработке и широкому производству.

В него вошли только часто используемые команды.

-

MISC – процессор, работающий с малым набором длинных команд.

Увеличение разрядности процессоров привело к идее укладки нескольких команд в одно слово. Процессор получил возможность обрабатывать сразу несколько команд.

Процессор MISC характеризуется большим набором часто встречающихся команд.

-

VLIW – процессор, работающий с системой команд сверхбольшой размерности.

Идея этого процессора:

Создается спец. компилятор планирования, который перед выполнением прикладной программы проводит ее анализ, и по множеству ветвей последовательности операций определяет группу команд, которые могут выполняться параллельно. Каждая такая группа образует одну сверхдлинную команду.

17.Иерархическая структура памяти. Основная память ЭВМ. Оперативное и постоянное запоминающие устройства: назначение и основные характеристики.

Ответ:

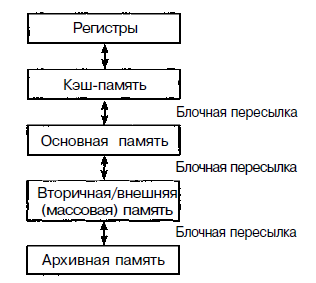

Иерархическая структура памяти

Иерархическая память – это система памяти, состоящая (как минимум) из 2-х устройств.

1-ое располагается рядом с ЦП имеет малое время доступа и высокую стоимость на бит.

2-е уже имеет более низкое время доступа, но большую емкость и малую стоимость.

Основная память - это устройство для хранения информации. Она состоит из оперативного запоминающего устройства (ОЗУ) и постоянного запоминающего устройства (ПЗУ).

ОЗУ- память, в которой хранятся исполняемая в данный момент программа и данные, с которыми она непосредственно работает. Это значит, что когда вы запускаете какую-либо компьютерную программу, находящуюся на диске, она копируется в оперативную память, после чего процессор начинает выполнять команды, изложенные в этой программе. При отключении питания содержимое ОЗУ стирается.

ПЗУ - это память, предназначенная только для чтения. Информация заносится в нее один раз (обычно в заводских условиях) и сохраняется постоянно (при включенном и выключенном компьютере). В ПЗУ хранится информация, присутствие которой постоянно необходимо в компьютере.

18.Организация оперативной памяти. Адресное и ассоциативное ОЗУ: принцип работы и сравнительная характеристика. Виды адресации. Линейная, страничная, сегментная память. Стек. Плоская и многосегментная модель памяти.

Ответ:

Организация оперативной памяти. Адресное и ассоциативное ОЗУ: принцип работы и сравнительная характеристика

ЗУ – устройства, предназначенные для хранения данных.

ЗУ делятся на электронные и электронно-механические.

Электронные характеризуются высокой стоимостью, обладают большим быстродействием, надежностью в работе.

Электронно-механические устройства более экономичны и имеют большую емкость памяти.

В этой связи в каждой системе создается и используется иерархия ЗУ.

Электронно-механические делятся на ОЗУ и ПЗУ.

-

Адресные ОЗУ – каждый элемент памяти имеет адрес, т.е. поиск данных происходит по адресу элемента.

-

Ассоциативное ОЗУ – поиск данных происходит по конкретному содержимому.

Виды адресации

-

Прямая адресация. Физический адрес операнда совпадает с кодом в адресной части команды, т.е. если в инструкции прямо указывается имя регистра, где находится операнд.

-

Непосредственная адресация. В команде содержится не адрес операнда, а непосредственно сам операнд.

-

Косвенная адресация. Адресная часть команды указывает адрес ячейки памяти или номер регистра, в которых содержится адрес операнда, т.е. при косвенной адресации на операнд, находящийся в памяти, указывает содержимое регистра (или регистров).

Плоская и многосегментная модель памяти.

В плоской модели все сегменты памяти отображаются в единое физическое адресное пространство.

Смещение сегмента может относиться либо к области кода, либо к области данных. Данная модель в наивысшей степени исключает механизм сегментации из архитектуры, видимой как разработчику системы, так и прикладному программисту. Такая модель выбирается для программной среды типа UNIX, которая поддерживает подкачку страниц, но не поддерживает сегментацию.

Сегмент определяется дескриптором сегмента. Для плоской модели должно создаваться минимум два дескриптора, один для ссылок к коду, а другой для ссылок к данным. Оба дескриптора имеют одинаковое значение базового адреса. Всякий раз при доступе к памяти содержимое одного из сегментных регистров используется для выбора дескриптора сегмента. Дескриптор сегмента содержит базовый адрес сегмента и его границу, а также информацию, управляющую доступом.

В многосегментной модели каждой программе дается собственная таблица дескрипторов сегментов и свои собственные сегменты.

Эти сегменты могут либо поступать в исключительное распоряжение программы, либо могут разделяться другими конкретными программами. Доступ между программами и конкретными сегментами может управляться индивидуально.

(продолжение вопроса 18)

Каждый сегмент представляет собой отдельное адресное пространство. Хотя они и могут располагаться в смежных блоках физической памяти, механизм сегментации предотвращает доступ к содержимому одного сегментом посредством выхода за границу другого сегмента при чтении. Попытка адресации памяти за концом сегмента ведет к генерации исключения общей защиты.

Стек:

Доступ к стековой памяти осуществляется не по адресу, а через вершину стека (ячейка памяти, доступная в данный момент времени)

Запись: новые данные записываются на вершину стека, а прежние данные как бы «проталкиваются» в глубь стека.

При этом можно прочитать только слово находящееся на вершине стека и только один раз. После прочтения слово оно «выталкивается» из стека и на его место «становится» слово, которое было «протолкнуто».

Способ – «последним пришел, первым вышил».

Метод адресации – косвенная адресация с автоувеличением.

Чтение: при чтение числа, на самом деле, оно никуда не девается, а просто коррекция указателя регистра делает его недоступным.

При новой записи в стек оно будет записываться по адресу «вытолкнутого» числа.

Метод адресации – косвенная адресация с автоуменьшением.

19.Кэш-память: назначение, структура, основные характеристики.

Ответ:

Кэш-память – буферное ЗУ.

Кэш-память разделяется на внутреннюю (L1) и внешнюю (L2).

Встроенная имеет высокое быстродействие и высокую цену, поэтому она меньше по емкости.

В кэш-память записывается часть команд и данных, содержащихся в ОП.

При этом нередко используется две кэш-памяти, одна (L1) хранит команды, другая (L2) – данные.

Характеристики:

-

Размер блока (строки) в байтах.

-

Время попадания. Попадание – это успешное обращение к более высокому уровню.

-

Потери при промахах. Промах – неуспешное попадание к более высокому уровню.

-

Время доступа – это время обращения к первому слову блока при промахе.

-

Время пересылки – доп. время для пересылки оставшихся слов блока.

-

Доля промахов – это доля обращения к данным, которые не найдены на более высоком уровне.

-

Размер кэш-память в Кб или Мб.

20.Организация кэш-памяти: с прямым отображением, частично-ассоциативная и полностью ассоциативная кэш-память.

Ответ:

Кэш-памяти с прямым отображением – каждый блок основной памяти имеет только одно фиксированное место, на котором может появится в кэш-памяти.

Организация заключается в том, что на попадание проверяется только один блок и только этот блок может быть замещен.

Кэш-память полная ассоциативная – некоторый блок основной памяти может располагаться на любом месте кэш-памяти.

Кэш-память частичной ассоциативная – некоторый блок основной памяти может располагаться на ограниченном множестве мест.

При полностью ассоциативной или частично-ассоциативной организации кэш-памяти имеются несколько блоков, из которых надо выбрать кандидата в случае промаха.

21.Динамическая память. Принцип работы. Обобщенная структурная схема памяти. Режимы работы: запись, хранение, считывание, режим регенерации. Модификации динамической оперативной памяти. Основные модули памяти. Наращивание емкости памяти.

(есть).

22.Статическая память. Применение и принцип работы. Основные особенности. Разновидности статической памяти.

(есть).

23.Устройства специальной памяти: постоянная память (ПЗУ), перепрограммируемая постоянная память (флэш-память), видеопамять. Назначение, особенности, применение.

Ответ:

Постоянная память – энергозависимая память, используемая для хранения данных, которые никогда не потребуют изменения (только для чтения).

Содержание памяти специальным образом ≪зашивается≫ в устройстве при его изготовлении для постоянного хранения. Из ПЗУ можно только читать.

В ПЗУ записывают программу управления самого процессора. Тут находятся программы управления дисплеем, клавиатуры, принтером, внешней памятью, программа запуска и остановки компьютера, тестирование устройств.

Перепрограммируемая постоянная память – энергозависимая память, допускающая многократную перезапись своего содержимого.

В постоянную память записывают программу управления самого процессора. Тут находятся программы управления дисплеем, клавиатуры, принтером, внешней памятью, программа запуска и остановки компьютера, тестирование устройств.

Важнейшая микросхема постоянной или Flash-памяти – модуль BIOS.

Видеопамять (VRAM) – разновидность оперативного ЗУ, в котором хранятся закодированные изображения.

Содержимое VRAM доступно процессору и дисплею, поэтому изображение на экране меняется одновременно с обновлением видеоданных в памяти.

24.Понятие интерфейса. Классификация интерфейсов.

Ответ:

Интерфейс – совокупность линий и шин, сигналов, электронных схем и алгоритмов (протоколов), осуществляющие обмен информацией между устройствами.

Выделяют следующие основные классификационные признаки:

|

Способ соединения компонентов

|

Способ передачи информации

|

Принцип обмена информации

|

Режим передачи информации

|

В соответствии с функциональным назначением интерфейсы можно поделить на следующие основные классы:

-

системные интерфейсы ЭВМ;

-

интерфейсы периферийного оборудования;

-

программно-управляемых модульных систем и приборов;

-

интерфейсы сетей передачи данных и др.

25.Системная плата: архитектура и основные разъемы.

Ответ:

Чипсет – обеспечивает совместное функционирование устройств на мат. плате.

Северный мост – выполняет функции контроля и направления 4 шин связи:

шина связи с ЦП;

шина связи с ОЗУ;

шина связи с графическим адаптером;

шина связи с Южным мостом.

Южный мост – отвечает за организацию более медленных устройств: периферийных, устройств ввода-вывода.

Тактовый генератор – вырабатывает сигналы для синхронизации работы всех элементов.

Сокет – основной разъем на мат. плате для установки ЦП. Каждый слот поддерживает определенный вид процессора.

Слоты ОП – служат для установки плат ОЗУ.

BIOS - тестирует устройство компьютера перед загрузкой ОС. Помогает настраивать мат. плату.

Слоты PCI – служат для подключения периферии к мат. плате.

Разъемы IDE – для подключения жестких дисков.

Разъем FDD – для подключения floppy-дисковода.

26.Системная шина и ее параметры (FSB, DMI, HyperTransport, QPI).

Ответ:

FSB – высокоскоростная параллельная 64-разрядная шина для связи северного моста с ЦП, ЦП с ОЗУ и с кэш-памятью 2 уровня (L2).

Использование технологии Quad Pumped Bus (четыре транзакции за цикл) позволяет при частоте шины 200 МГц поддерживать передачу данных с частотой 800 МГц. При этом, с учетом разрядности шины, обеспечивается поток данных 3.6 Гбайт/с.

Особенностью шины - реализация режима двухканального обмена с двумя модулями оперативной памяти одновременно.

При архитектуре DIB системная шина физически разделена на две:

-

первичная шина (FSB) – связывает ЦП с ОЗУ и ОЗУ с периферийными устройствами.

-

вторичная шина (BSB) – связывает ЦП с кэш-памятью 2-ого уровня.

DMI – последовательная шина для связи ЦП с северным мостом и северного моста с южным мостом.

Для связи ЦП с чипсетом используется 4 канальная DMI.

Часто в процессор использующий DMI встраивают на ряду контроллером ОЗУ, контроллер шины PCI Express, обеспечивающий взаимодействие с видеокартой.

Пропускная способность – 10 Гб/с (версия 1.0); 20 Гб/с (версия 2.0).

HT - универсальная высокоскоростная шина типа «точка-точка» с низкой латентностью, используемая для связи процессора с северным мостом.

Шина HyperTransport - двунаправленная, то есть для обмена в каждую сторону выделена своя линия связи. К тому же она работает по технологии DDR (Double Data Rate), передавая данные, как по фронту, так и по спаду тактового импульса.

Пропускной способностью - 12.8 ГБайт/с (версия 1.0); 22.4 ГБайт/с (версия 2.0); 51.6 Гбайт/с (версия 3.1).

Технология HyperTransport - очень гибкая, и позволяет варьировать, как частоты шины, так и ее разрядность. Это позволяет использовать ее не только для связи процессора с северным мостом и ОЗУ, но и в медленных устройствах. При этом возможность уменьшения разрядности и частоты ведет к экономии энергии.

QPI (QuickPath Interconnect) – последовательная шина типа «точка-точка», используемая для связи процессоров между собой и с чипсетом.

Шина QPI - двунаправленная, то есть для обмена в каждую сторону предусмотрен свой канал, каждый из которых состоит из 20 линий связи. Следовательно, каждый канал – 20-разрядный, из которых на полезную нагрузку приходится только 16 разрядов.

Пропускная способность - 19,2 Гб/с; 25,6 Гб/с.

27.Интерфейсы и назначение шин расширений (ISA, EISA, PCI, AGP, PCIExpress).

Ответ:

ISA – стандартные шины ХТ (8 бит) и АТ (16 бит).

|

Шина ХТ: Характеристики:

Поддерживает централизованный метод арбитража, имея для этого общие линии запроса и ответа. |

Шина АТ: Характеристики:

|

EISA – дальнейшее развитие ISA.

Совместима с ISA и соответственно имеет возможность использования многочисленных плат адаптеров, разработанных для ISA.

|

Основные характеристики:

|

Поддерживает Plug&Play, т.е. шина позволяет определять устройства, подключенные к каждому из разъемных соединителей расширения. Использует «графический» принцип адресации, т.е. магистральные линии системной шины дополнены индивидуальными линиями связи от каждого разъема. |

Шина поддерживает режим Burst Mode – скоростной режим пересылки пакетов данных.

PCI - шина для подключения плат расширения к материнской плате. Также долгое время использовалась для связи северного моста с южным.

Использует синхронный 32- или 64-разрядный объем данных. Использует мультиплексирование, т.е. адреса передаются по одному и тому же каналу.

Тактовая частота – 33-66МГц.

Полная поддержка многих активных устройств. Например: несколько контроллеров жестких дисков одновременно могут работать на шине.

AGP - 32-разрядная шина для работы с графическим адаптером.

Схема AGP взаимодействует с 4-мя источниками информации:

-

Процессор (кэш-память 2-ого уровня)

-

ОП

-

Графическая карта

-

Шина PCI.

(Продолжение 27 вопроса.)

PCI Express – гибкий, масштабируемый, высокоскоростной, последовательный интерфейс.

Главное отличие от PCI – поддержка связи «точка-точка» (двунаправленное последовательное соединение)

Пропускная способность – 16 Гб/с.

Преимущество PCI Express – «горячие подключение», т.е. возможность отключать/подключать устройства во время работы компьютера, т.е., без отключения питания).

Топология шины содержит главный мост и несколько оконечных пунктов (устройств ввода-вывода).

Многократное соединение «точка-точка» вводит новый элемент – переключатель топологии системы ввода-вывода.

28.Интерфейсы и назначение параллельных шин периферийных устройств: ATA, SATA и SCSI.

Ответ:

IDE-ATA-PATA – параллельный 16-разрядный интерфейс связи с жёстким диском.

Использование интерфейса IDE (PATA) подразумевает, что контроллер жесткого диска располагается не на материнской плате или в виде платы расширения, а встроен в сам жесткий диск. В южном мосте, располагается только контроллер канала IDE (PATA).

Специфика IDE определяет, что на мат. плате устанавливается контроллер IDE-интерфейса с двумя одинаковыми каналами, к каждому из которых можно подключить до 2 равноправных устройств, при этом нужно, чтобы одно было ведущем, а другое ведомым.

Для передачи данных используется 40-жильный IDE-кабель (шлейф) (PATA66 80-жильный).

Используется кабель с 40-контактными разъемами и длинной < 46 см. Практически всегда на нем используется 3 разъема – один для подключение к мат. плате, другие 2 для жестких дисков.

Мах. Пропускная способность – 133Мб/с.

IDE использует полудуплексную передачу данных.

SATA – последовательный интерфейс для связи южного моста с жестким диском.

При использование SATA каждый накопитель подключается своим кабелем. Отдельным кабелем на жесткий диск подается питание.

Используется 4-, 8- и 16-канальный разъем. Мах. Длина <1 метра.

SATA использует дуплексную передачу данных.

SCSI – универсальная шина для подключения высокоскоростных устройств.

Шина обладает высокой пропускной способностью, но сложно устроенная и дорогостоящая. Поэтому в основном применяется в серверах и промышленных вычислительных системах.

29.Последовательный и параллельный порты (RS-232-C, LPT)

Ответ:

RS-232-C – это стандарт для соединения ЭВМ с различными последовательными внешними устройствами.

Последовательная передача данных состоит в побитовой передаче каждого байта, в форме кадра данных, содержащего сигнал начала передачи (Start), сигнал окончания передачи (Stop) и информационные биты.

Основа последовательного порта – микросхема UART.

UART содержит регистры приемка и передатчика данных.

При передачи байта информации он вначале записывается в буферный регистр передатчика, затем в сдвиговый регистр, откуда выдвигается по битам для последовательной передачи по линии связи. Обратный процесс происходит при приеме данных.

Разъем для подключения последовательного порта может содержать 25 или 9 выводов:

-

2 провода – для приема и передачи данных;

-

остальные – для вспомогательных и управляющих сигналов.

RS-232-C определяет взаимодействие между устройствами двух типов:

-

DTE (Date terminal equipment – оконечное/терминальное устройство);

-

DCE (Data communication equipment – устройство связи).

DTE – компьютер, терминал;

DCE – модемы, принтеры, графопостроители.

Для связи DTE-DCE необходимо осуществлять соединение в разъёмах проводов по принципу «вход-вход» и «выход-выход».

Для связи DTE-DTE принцип соединения – «выход-вход» и «вход-выход».

LPT – параллельный порт.

Параллельным потому, что в подключаемом к нему кабеле данные передаются одновременно по нескольким проводникам.

Хотя параллельный порт большей частью используется для подключения принтеров, тем не менее, существовали и другие его применения. Во-первых, при помощи порта LPT можно напрямую соединить два компьютера – посредством специального кабеля Interlink.

Конструктивно он оформлен в виде 25-контактного разъема типа D (DB25).

Имеется 8 шин (линий) данных, 8 шин заземления (для каждой шины данных).

30.Последовательные шины: USB, FireWire.

Ответ:

USB - универсальный последовательный канал передачи данных для подключения к ЭВМ среднескоростных и низкоскоростных периферийных устройств.

Шина строго ориентирована и состоит из контроллера канала и подключаемых к нему нескольких оконечных устройств. Обычно контроллеры канала USB встроены в южный мост материнской платы. В современных материнских платах могут размещаться до 12 контроллеров канала USB с двумя портами каждый.

Интерфейс USB имеет встроенные линии питания, благодаря чему позволяет использовать устройства без собственного источника питания или одновременно с обменом данными подзаряжать аккумуляторы оконечных устройств, например телефонов.

USB поддерживает «горячее» подключение оконечных устройств. Это возможно, из-за более длинного заземляющего контакта.

FireWire (IEEE 1394) - стандарт последовательной высокоскоростной шины.

Эта шина предназначена для подключения высокоскоростных периферийных устройств, таких как внешние жесткие диски, цифровые видеокамеры, музыкальные синтезаторы и так далее.

Основные характеристики:

- мax.скорость передачи данных изменяется от 400 Мб/с до 3.2 Гбит/с

- максимальное количеств устройств, последовательно подключаемых к одному контроллеру – 64.

При этом все подключаемые устройства делят между собой пропускную способность шины.

- горячее подключение и отключение устройств;

- возможность использования устройств, питающихся от шины и не имеющих собственного источника питания.

30.Режимы работы процессора. Характеристика реального режима процессора 8086. Адресация памяти реального режима.

Ответ:

Режимы работы процессора:

-

Реальный режим

-

Защищенный режим

-

Виртуально реальный режим

Характеристика реального режима процессора 8086:

-

Процессор i8086 выполняет 16-разрядные команды, применяя 16-разрядные внутренние регистры, и адресовать только 1 Мбайт (220 байт) памяти, используя 20 разрядов для адреса.

-

Адресная шина i8086/i80286 имеет шину 16-бит.

-

Пространство ОЗУ, с которым может работать процессор – 64 Кб.

Адресация памяти реального режима:

Для адресации байта памяти используются

две 16-разрядные компоненты адреса

- сегмент и смещение.

Физический адрес , который попадает на шину адреса системной платы компьютера, складывается из сдвинутой влево на 4 бита и дополненной справа 4 нулевыми битами сегментной компоненты и компоненты смещения.

Перед сложением компонента смещения расширяется до 20 бит так, что в старшие четыре бита записываются нули.

Недостатки реального режима:

-

Нельзя использовать расширенную память, расположенную выше 1Мб.

-

Схема адресации не пригодна для работы с большими объемами памяти.

-

Программы, работающие в этом режиме, имеют доступ ко всей адресации памяти.

-

Недоступна виртуальная память, мультизадачность, уровни привилегий.

32.Основные понятия защищенного режима. Адресация в защищенном режиме. Дескрипторы и таблицы. Системы привилегий. Защита.

Ответ:

Основные понятия защищенного режима:

Адреса состоят из двух компонент – «спектры смещения».

Для вычисления физ. адреса используются 2 таблицы дескриптора:

-

Глобальная (CDT)

-

Локальная (LDT)

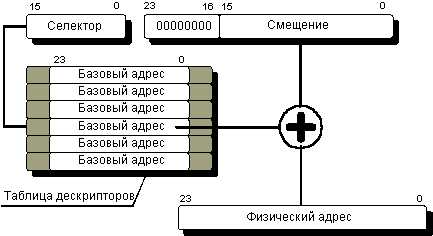

Селектор используется для адресации ячейки одной из таблиц дескрипторов, содержащей помимо прочей информации базовый 24-разрядный адрес сегментов.

Для получения физического адреса базовый адрес складывается со смещением, расширенным до 24 разрядов.

Селектор содержит номер ячейки таблицы дескрипторов, но не компоненту физического адреса.

![]()

Форма селектора: состоит из индекса, TI, RPL.

Поле TI используется для выбора таблицы дескрипторов. Если бит TI равен 0, для выборки базового адреса используется глобальная таблица дескрипторов GDT, если 1 - локальная LDT.

Поле RPL содержит уровень

привилегий, запрошенный программой при

обращении к сегменту. Программа может

обращаться только к таким сегментам,

которые имеют соответствующий уровень

привилегий.![]()

Формат дескриптора сегмента процессора 80286: Резерв, Доступ, Базовый адрес, Предел.

Поле предел – размер сегмента. При вычислении физического адреса процессор следит за тем, чтобы физический адрес не выходил за пределы, указанные в дескрипторе сегмента.

Поле доступа - содержит уровень привилегий сегмента и информацию о типе сегмента. Существуют сегменты:

-

кода,

-

сегменты данных

-

системные сегменты.

Для сегмента кода можно запретить операцию чтения.

Для сегмента данных - операцию записи.

Системы привилегий:

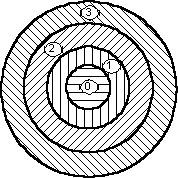

В процессорах 80ххх и Pentium существуют четыре уровня привилегий - от 0 до 3, причем 0 - наибольшая привилегия. Уровни привилегий часто называют также кольцами защиты.

В кольце 0 - ядро операционной системы.

Кольцо 1 - уровню привилегий драйверов

Кольцо 2 - системы, таким как системы управления базами данных.

Кольцо 3 - прикладные программы, запускаемые пользователем.

(продолжение вопроса 32).

Защита:

Управление задачами контролируется шлюзом. Он проверяет правило использование привилегий.

Пользовательская программа обращается к спец. дескриптору, определяющему точку входа в процедуру.

Спец. дескриптор – «шлюз вызова»

Его привилегия низкая для того, чтобы к нему можно было обратиться прикладным программам. Адрес шлюза вызова заранее определен.

Шлюза помимо байта доступа содержит счетчик слов, определяющий кол-во параметров передаваемых при вызовах, а также селектор и смещение назначения, точно указывающих виртуальный адрес точки вызова.

,

A.

,

A.