- •Введение

- •1 Техническое задание

- •2 Анализ схемы электрической принципиальной

- •3 Обоснование выбора микроконтроллера

- •4.2 Структура микроконтроллера pic16f876

- •4.3 Арифметико-логическое устройство (алу) Порты

- •4.4 Организация памяти микроконтроллера pic16f876. Регистры.

- •4.5 Описание связей микроконтроллера в устройстве

- •5 Разработка управляющей программы

- •Список используемых источников

4.4 Организация памяти микроконтроллера pic16f876. Регистры.

Организация памяти данных и программ. В микроконтроллерах PIC16F87X имеется три вида памяти. Память программ и память данных имеют раздельные шины данных и адреса, что позволяет выполнять параллельный доступ.

Микроконтроллеры

PIC16F87X

имеет тринадцати разрядный счетчик

команд, способность реализовать 8К![]() 14

слов памяти программ. Физически

реализовано FLASH

памяти программ 8К

14

слов памяти программ. Физически

реализовано FLASH

памяти программ 8К![]() 14.

Обращение к физически не реализованной

памяти программ приведет к адресации

реализованной памяти.

14.

Обращение к физически не реализованной

памяти программ приведет к адресации

реализованной памяти.

Память данных разделена на четыре банка, которые содержат регистры общего и специального (SFR) назначения. Биты RP1 (STATUS<6>) и RPO (STATUS<5>) предназначены для управления банками данных. В таблице 4 показано состояние управляющих битов при обращении к банкам памяти данных.

Объем банков памяти данных до 128 байт (7Fh).

В начале банка размещаются регистры специального назначения, затем регистры общего назначения выполненные как статическое ОЗУ. Все реализованные банки содержат регистры специального назначения. Некоторые, часто ис

пользуемые регистры специального назначения могут отображаться и в других банках памяти.

Таблица 4 – Значения битов управления доступом к банкам памяти данных

|

Rp1,Rp0 |

Банк |

|

00 |

0 |

|

01 |

1 |

|

10 |

2 |

|

11 |

3 |

Память данных в РПЗУ (EEPROM). Микроконтроллеры подгруппы PIC6F8X имеют энергонезависимую память данных 64х8 бит EEPROM, которая допускает запись и чтение во время нормальной работы. Эта память не принадлежит области регистровой памяти ОЗУ. Доступ к ней осуществляется посредством косвенной адресации через регистры специальных функций: EEDATA <08h>, который содержит 8-битовые данные для чтения/записи и EEADR <09h>, включающий адрес ячейки, к которой идет обращение. Для управления процессом чтения/записи используются два регистра: EECON1 <88h> и EECON2 <89h>.

При записи байта автоматически стирается предыдущее значение, и записываются новые данные (стирание перед записью). Все эти операции производит встроенный автомат записи EEPROM. Содержимое ячеек этой памяти при выключении питания сохраняется.

Вектор сброса

•

•

Вектор

прерываний

Страница 0

Страница 1

Страница 2

Страница 3

Внутренняя

память программ

Рисунок 14 – Организация памяти программ микроконтроллера PIC16F876

Регистры общего назначения. Обратиться к регистрам общего назначения можно прямой или косвенной адресацией, через регистр FSR.

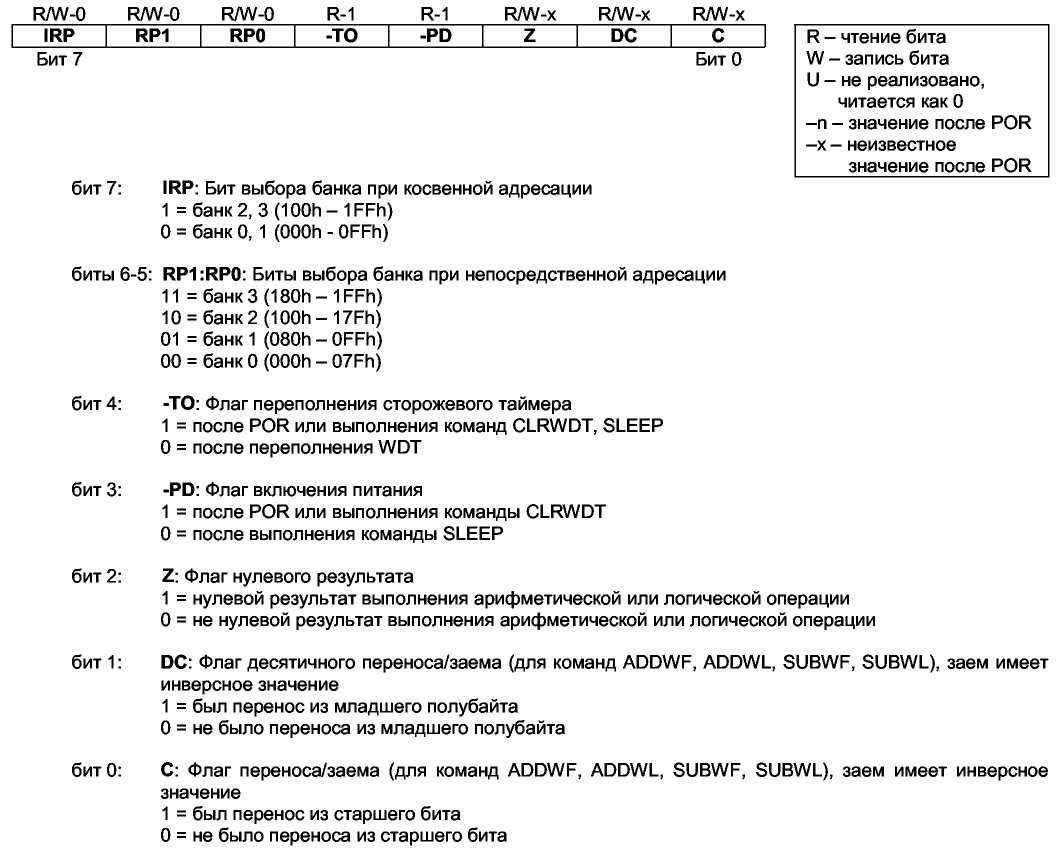

Регистр STATUS. В регистре STATUS содержатся флаги состояния АЛУ, флаги причины сброса микроконтроллера и биты управления банками памяти данных.

Регистр STATUS может быть адресован любой командой, как и любой другой регистр памяти данных. Если обращение к регистру STATUS выполняется командой, которая воздействует на флаги Z, DC и С, то изменение этих трех битов командой заблокирована. Эти биты сбрасываются или устанавливаются согласно логике ядра микроконтроллера. Команды изменения регистра STATUS также не воздействуют на биты ТО и PD.

Рисунок 11 - Карта памяти данных микроконтроллеров PIC16F877/876

Например, команда CLRF STATUS сбросит три старших бита и установит бит Z. Флаги С и DC используются как биты заёма и десятичного заёма соответственно, например, при выполнении команд вычитания SUBLW и SUBWF.

R-чтение бита; W – запись бита; U – не реализовано; n – значение после

POR; x – неизвестное значение после POR.

Рисунок 15 – Регистр STATUS

Таблица 5 - Назначение битов регистра STATUS

-

№

Обозначение

Назначение

Значения

0

C

Флаг перенос/заема

1- был перенос; 0- не было переноса из старшего бита;

1

DC

Флаг десятичного переноса/заема

1- был перенос; 0- не было переноса из младшего полубайта;

2

Z

Флаг нулевого результата

1 - нулевой результат; 0 - ненулевой результат;

3

-PD

Флаг включения питания

1 - после POR; 0 - после выполнения команды SLEEP;

4

-TO

Флаг переполнения сторожевого таймера

1 – после POR или CLRWDT; 0 – после переполненияWDT;

5,6

RP

Биты выбора банка

11 - банк 3; 10 - банк 2; 01 - банк 1; 00 - банк 0

7

IRP

Бит выбора банка при косвенной адресации

1 - банк 2, 3 (100h-1FFh);

0 - банк 0,1(000h-0FFh);

Регистр OPTION REG. Регистр OPTION доступен для чтения и записи, содержит биты управления:

- предварительным делителем TMR0/WDT;

- активным фронтом внешнего прерывания RB0/INT;

- подтягивающими резисторами на входах PORTB.

R – чтение бита; W – запись бита; U – не реализовано; n – значение по-

сле POR; x – неизвестное значение после POR.

Рисунок 16 – Регистр OPTION REG

Таблица 6 – Назначение битов регистра OPTION REG

|

№ |

Обозначение |

Назначение |

Значения |

|

0 |

PS0 |

Установка коэффициента деления предделителя |

000 – 1/2; 001 – 1/4; 010 – 1/8; 011 – 1/16; 100 – 1/32; 101 – 1/64; 110 – 1/128; 111 – 1/256; |

|

1 |

PS1 |

||

|

2 |

PS2 |

||

|

3 |

PSA |

Выбор включения предделителя |

1 – перед WDT; 0 – перед TMPR0; |

|

4 |

TOSE |

Выбор тактового сигнала для TMR0 |

1 – приращение по заднему фронту; 0 - приращение по переднему фронту; |

|

5 |

T0CS |

Выборка тактового сигнала для TMR0 |

1 – внешний тактовый сигнал с вывода RA4; 0 – внутренний тактовый сигнал CLKOUT; |

|

6 |

INTEDG |

Выборка активного фронта сигнала на входе внешнего прерывания |

1 – прерывание по переднему фронту сигнала;0 – прерывание по заднему фронту сигнала; |

|

7 |

-RBPU |

Включение подтягивающих резисторов на входах PORTB |

1 – подтягивание резисторов отключено;0 – подтягивание резисторов включено; |