курсовой проект / процессоры / рис3

.doc

Назначение выводов

Выводы Назначение READY Готовность TEST Проверка INTA

(QS1) Подтверждение

прерывания STB

(QS0) Строб адреса DE

(ST0) Разрешение передачи

данных OP/IP

(ST1) Выдача/прием данных M/I0

(ST2) Обращение к ЗУ/УВВ WR

(LOCK) Запись HLDA

(RQ/E0) Подтверждение

захвата HLD

(RA/E0) Захват RD Чтение MN/MX Управление режимом

min/max BHE/ST7 Разрешение передачи

по старшей половине канала адреса/данных

Ucc +5В

Назначение выводов

Выводы Назначение CSYNC Синхронизация PCLK Тактовый сигнал ТТЛ

– уровня AEN1 Адрес готовности 1 RDY1 Готовность 1 (вход) READY Готовность (выход) RDY2 Готовность 2 (вход) AEN2 Адрес готовности 2 CLK Тактовый сигнал МОП

– уровня GND Общий RESET Установка (выход) RES Установка (вход) OSC Выход мультивибратора F/C Выбор задающей

частоты EF1 Внешний генератор TANK вывод для подключения

LC – контура XTAL1

(2) выводы для подключения

кварцевого резонатора Ucc +5В

Подключение

генератора тактовых импульсов к

микропроцессору

АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ MAX1300

Структурная схема Расположение выводов

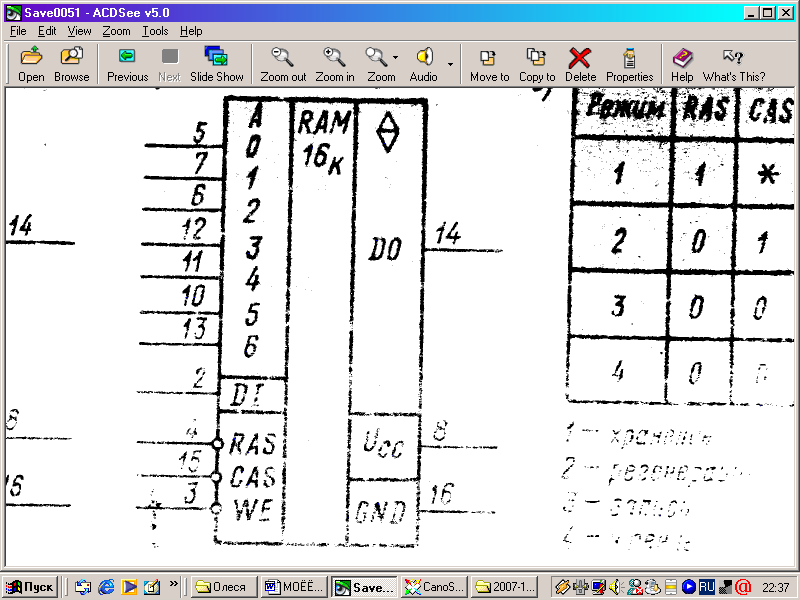

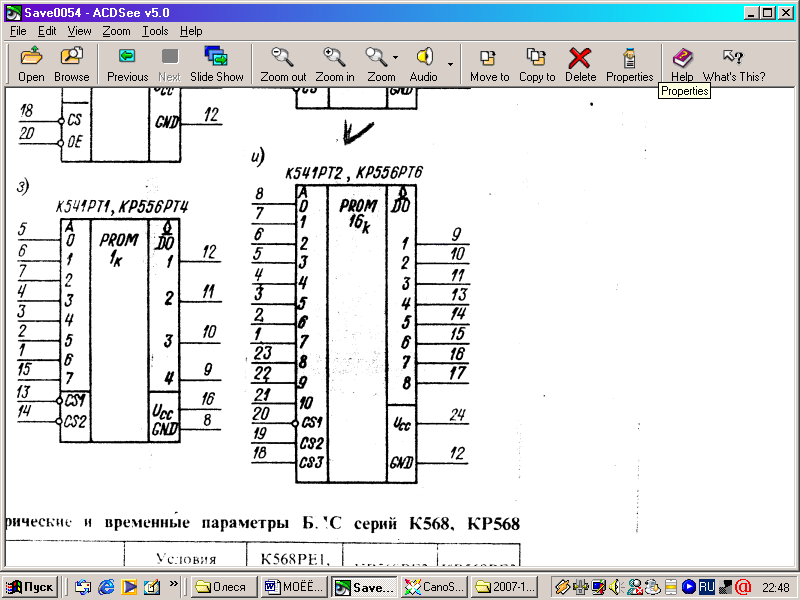

ОПЕРАТИВНОЕ И ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Корпус ОЗУ КР565РУ6 Корпус ПЗУ К541РТ2 Подключение ОЗУ (ПЗУ) к шинам адреса и данных

Назначение

выводов ПЗУ

Выводы Назначение CS1,

CS2,

CS3 Управляющие

сигналы А0

– А10 Входы

адреса D0 Выходные

данные 0V Общий

вывод микросхемы GND Общий Ucc Напряжение

питания

Назначение выводов ОЗУ

|

Выводы |

Назначение |

|

А0 – А6 |

Входы адреса |

|

RAS |

Сигнал выбора адреса строк |

|

CAS |

Сигнал выбора адреса столбца |

|

WE |

Сигнал записи/чтения |

|

D0 |

Считывание информации |

|

DI |

Запись информации |

|

Ucc |

Напряжение питания |

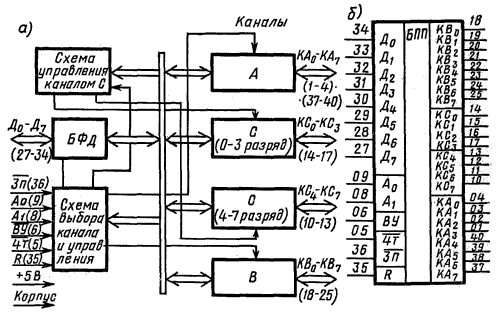

ПРОГРАММИРУЕМЫЙ ПЕРЕФЕРИЙНЫЙ ИНТЕРФЕЙС КР580ВВ55

Назначение

выводов

Выводы Назначение Д0

÷ Д7 Двунаправленная

магистраль данных для передачи данных,

управляющих слов и информации состояния КА0

÷ КА7 Двунаправленная

магистраль данных канала А КВ0

÷ КВ7 Двунаправленная

магистраль данных канала В КС0

÷ КС7 Двунаправленная

магистраль данных канала С ВУ* (CS*) Выбор

устройства А0-А1 Входы,

необходимые для выбора одного из

каналов А, В, С ЧТ* Вход,

на который подается сигнал на выдачу

данных R (RES) Вход,

используемый для начальной установки

схемы ЗП* Вход записи данных

в схему

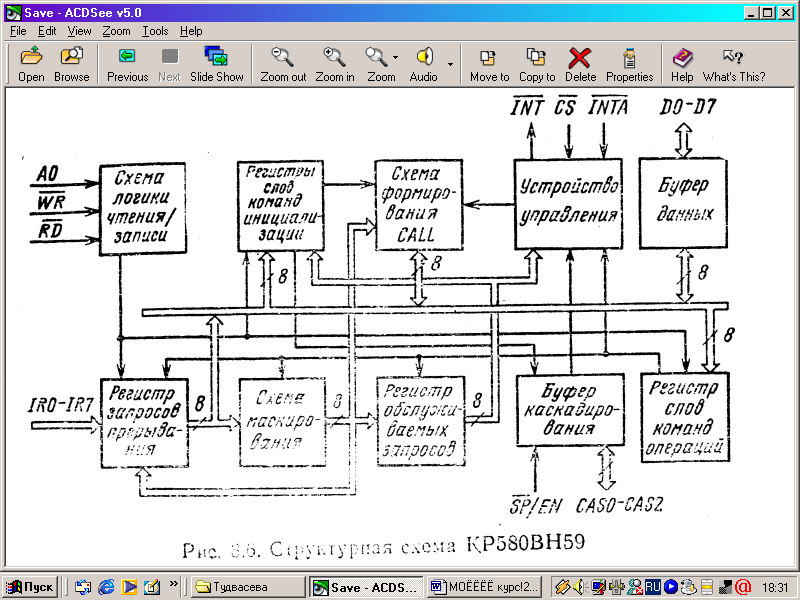

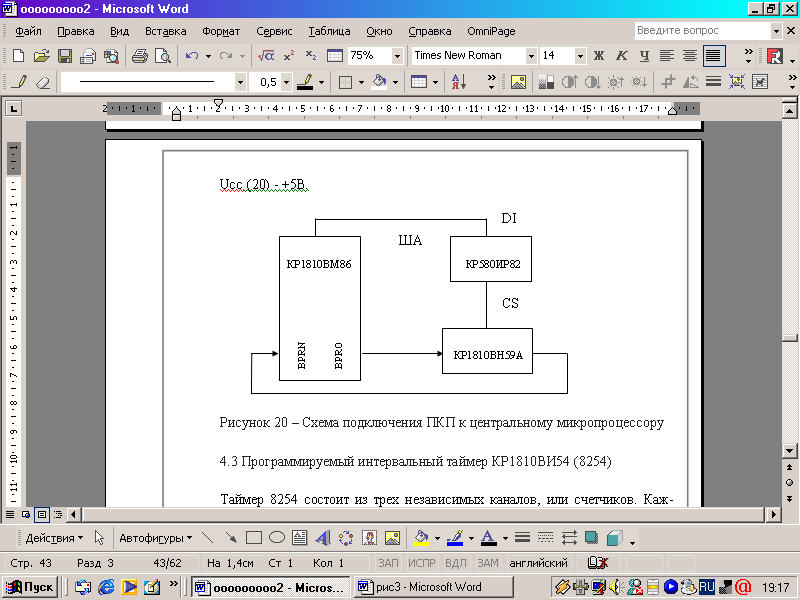

ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР ПРЕРЫВАНИЙ КР1810ВН59А

Выводы Назначение S2-S0

(1, 19, 18) Шина состояния IOB (2) Выбор режима работы SYSB/RESB

(3) Разрешение доступа RESB

(4) Выбор режима работы

с резидентной шиной BCLK

(5) Синхронизация

системной шины INIT

(6) Начальная установка ЧТ* Вход,

на который подается сигнал на выдачу

данных BREQ

(7) Запрос шины BPRO

(8) Выход приоритетного

разрешения доступа BPRN

(9) Вход приоритетного

разрешения доступа GND

(10) Общий BUSY

(11) Занято CBRQ

(12) Вход/выход общего

запроса шины AEN

(13) управление шинными

устройствами МП ANYRQST

(14) Разрешение освобождения

системной шины CRQLCR

(15) Запрет освобождения

системной шины LOCK

(16) Блокировка освобождения

системной шины CLK

(17) Тактовый сигнал

Назначение

выводов

С

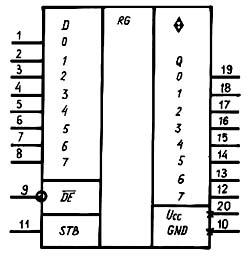

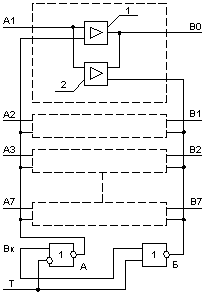

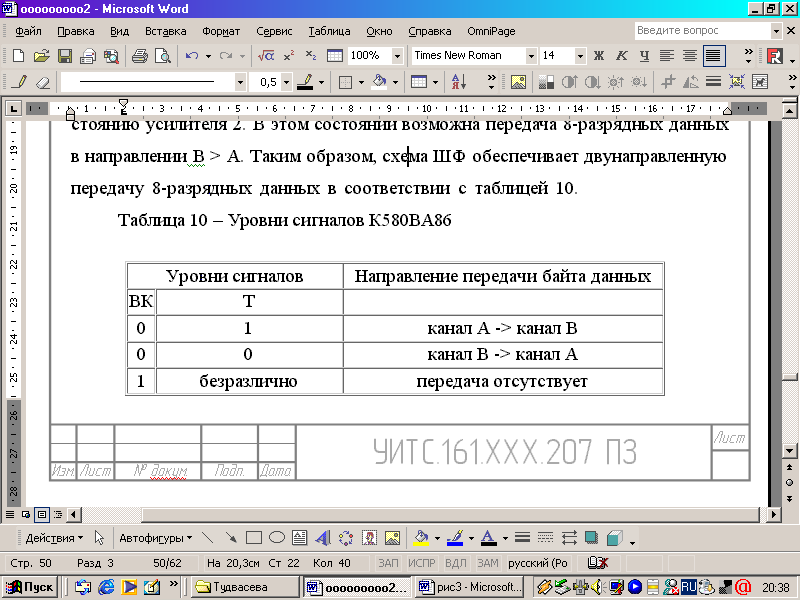

БУФЕРНЫЙ РЕГИСТР КР580ИР82 И ШИННЫЙ ФОРМИРОВАТЕЛЬ К580ВА86

Корпус КР580ИР82 Структурная схема КР580ИР82 Структурная схема К580ВА86

|

Выводы |

Обозначение |

Функциональное назначение |

|

1-8 |

D0-D7 |

Информационная шина |

|

9 |

OE |

Разрешение передачи данных |

|

10 |

GND |

Общий (земля) |

|

11 |

STB |

Стробирующий сигнал |

|

12-19 |

D7-D0 |

Информационная шина |

|

20 |

Ucc |

Напряжение питания +5В |