2.3. Універсальні регістри

В серіях ІС (інтегральних мікросхем) та бібліотеках ВІС/НВІС існує багато варіантів регістрів. Серед них часто зустрічаються багатофункціональні або універсальні регістри, здатні виконувати набір мікрооперацій. Багатофункціональність досягається композицією в одній і тій же схемі частин, необхідних для виконання різних операцій. Керуючі сигнали, що задають вид виконуваної в даний час операції, активують необхідні для цього частини схеми.

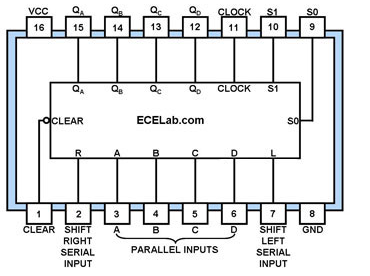

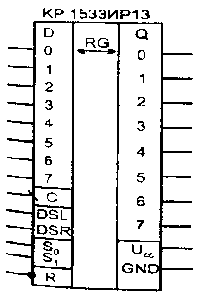

Типовим представником універсальних регістрів являється схема ИР13. Це восьмирозрядний реверсивний регістр, який має також паралельні входи і виходи, вхід асинхронного скиду R і входи вибору режиму S0 и S1, що задають чотири режими (паралельне завантаження, два зсуви і зберігання). Таблиця істинності регістра ИР13 подана в табл. 2.2 , умовне позначення регістра ИР13 на схемі електричній принциповій приведено на рис. 2.10.

Табл. 2.2. Таблиця істинності регістра ИР13

|

Режим |

Входи |

Виходи |

|||||||||||

|

|

C |

|

SO |

S1 |

DSR |

DSL |

Dn |

Q0 |

Q1 |

. . . . |

Q6 |

Q7 |

|

|

Скидання |

X |

0 |

X |

X |

X |

X |

X |

0 |

0 |

. . . . |

0 |

0 |

|

|

Зберігання |

|

1 |

0 |

0 |

X |

X |

X |

Q0 |

Q1 |

. . . . |

Q6 |

Q7 |

|

|

Зсув вліво |

|

1 |

1 |

0 |

X |

0/1 |

X |

Q1 |

Q2 |

. . . . |

Q6 |

DSR |

|

|

Зсув вправо |

|

1 |

0 |

1 |

0/1 |

X |

X |

DSR |

Q0 |

. . . . |

Q5 |

Q6 |

|

|

Паралельне завантаження |

|

1 |

1 |

1 |

X |

X |

Dn |

D0 |

D1 |

. . . . |

D6 |

D7 |

|

Рис. 2.10. Умовне позначення універсального регістра ИР13

3. Особисте завдання

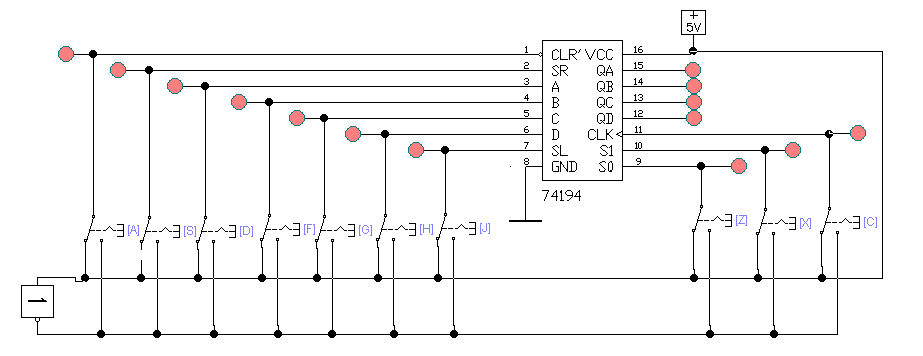

Для дослідження було дано регістр 74194 серії.

|

|

|

Рис. 3.1. Зовнішні виводи регістра

|

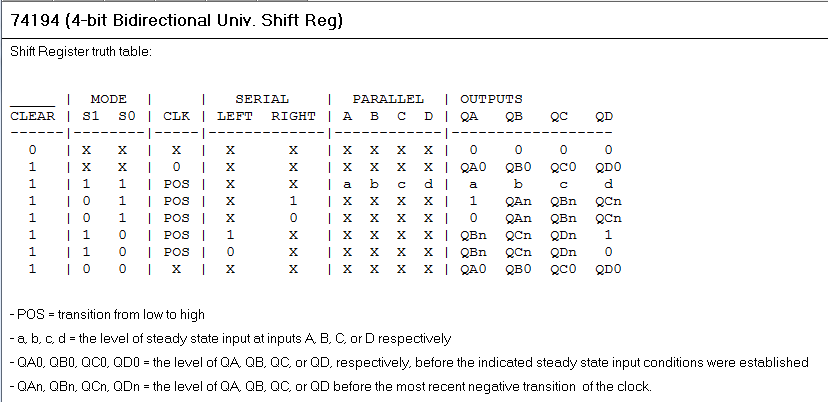

Регістр 74194 – це 4-розрядний двосторонній універсальний регістр зсуву. Часто потрібні складніші регістри: з паралельним синхронним записом інформації, реверсивні, реверсивні з паралельним записом інформації. Такі регістри називають універсальними. Розглянемо одну з таких мікросхем 74194 (аналог К155ІР11) - 4-розрядний двонаправлений універсальний регістр зсуву (рис. 3.1). Можливі 4 режими роботи даного регістру: паралельна завантаження; зсув вправо (в напрямі від QА до QD); зсув вліво (в напрямку від QD до QА); блокування. Синхронне паралельне завантаження здійснюється шляхом подачі 4 розрядів даних на паралельні входи (A-D) і установки сигналу високого рівня на обох керуючих входах S0 і S1. Дані завантажуються у відповідні тригери і з'являються на виходах після проходження фронту тактового імпульсу. Під час завантаження послідовне переміщення даних заборонено. Зрушення вправо здійснюється синхронно з проходженням фронту тактового імпульсу при установці на вході S0 сигналу високого, а на вході S1 сигналу низького рівнів. У цьому режимі дані в послідовній формі надходять на вхід зсуву вправо (SR). При установці на керуючому вході S0 сигналу низького, а на вході S1 сигналу високого рівнів дані синхронно зсуваються вліво, а нові дані надходять на послідовний вхід зсуву вліво (SL). Режим блокування реалізується при подачі на обидва керуючих входу сигналу низького рівня. Режим роботи С LK слід змінювати тільки при високому рівні тактового імпульсу.

Таблиця 3.1. Таблиця істинності регістра

Побудовано наступнусхемудля перевірки таблиці істиності тригера (рис.3.3).

|

|

|

Рис.3.3. Схема з ручним управлінням виводами регістра

|

Вручну було перевірено усі режими роботи регістра. Результати співпали з таблицею істинності.