- Шина питания

Микропроцессор Z80 использует единственное напряжение питания +5 В, подаваемое на вывод 11. “Земля” подаётся на вывод 29.

2.2 Генератор тактовых импульсов КР580ГФ24

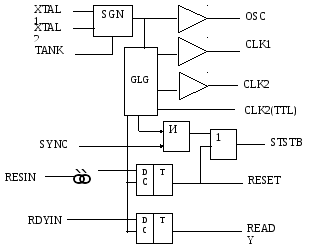

Генератор тактовых импульсов КР580ГФ24 предназначен для синхронного организации микропроцессорной системы. ГТИ формирует тактовые импульсы частотой до 2,5 мГц, амплитудой 12 В, тактовые импульсы амплитудой до 5 В для ТТЛ-схем, а также некоторые управляющие сигналы для микропроцессорной системы. Структурная схема ГТИ представлена на рисунке 4, подключение ГТИ к МП показано на рисунке 5. ГТИ состоит из задающего генератора(SGN), генератора тактовых импульсов(GLG), порогового элемента, формирователей и логических схем. Для работы ГТИ необходимо подключение внешнего кварцевого резонатора с частотой в 9 раз большей, чем частота выходных тактовых импульсов ГТИ.

Основные временные характеристики тактовых импульсов, приведены в таблице 1.

Таблица 1 - Временные характеристики ГТИ КР580ГФ24

|

Временные характеристики |

Значение |

|

время

переднего и заднего фронтов( |

0-50 |

|

Ширина

импульса CLK1( |

|

|

Временной

интервал между задним фронтом СLK1

и передним фронтом CLK2( |

|

|

Временной

интервал между задним фронтом СLK2

и передним фронтом CLK1( |

|

|

Задержка

CLK2

по отношению к CLK1( |

|

Основные электрические параметры микросхемы КР580ГФ24 указаны в таблице 2.

Таблица 2 – Электрические параметры микросхемы КР580ГФ24

-

Электрические параметры

Значение

Входное напряжение L - уровня

,

В

,

В

Напряжение на входе RESIN

,В

,В

Выходное напряжение L - уровня

,В

,В

Выходное напряжение H - уровня

,

В

,

Вна выходе CLK1, CLK2

на выходах READY, RESET

на всех других выходах

Ток источника питания

,

мА

,

мА

Рисунок 4 – Структурная схема ГТИ КР580ГФ24

Рисунок 5 – Схема подключения ГТИ к МП

Опишем выводы ГТИ:

![]() ,

,

![]() -

входы для подключения кварцевого

резонатора (номер контакта 15,14)

-

входы для подключения кварцевого

резонатора (номер контакта 15,14)

![]() -

входы для подключения параллельного

LC

- контура (номер контакта 13)

-

входы для подключения параллельного

LC

- контура (номер контакта 13)

![]() -

вход

синхронизации (номер контакта 5)

-

вход

синхронизации (номер контакта 5)

![]() -

входной сигнал «Сброс»

(номер контакта 2)

-

входной сигнал «Сброс»

(номер контакта 2)

![]() -

вход сигнала «ГОТОВ» для подачи сигналов

о готовности внешних устройств к работе

с МП (номер контакта 3)

-

вход сигнала «ГОТОВ» для подачи сигналов

о готовности внешних устройств к работе

с МП (номер контакта 3)

![]() -

выход генератора, используемый для

тактирования периферийных устройств

(номер контакта 12)

-

выход генератора, используемый для

тактирования периферийных устройств

(номер контакта 12)

![]() -

выходы тактовых импульсов (номер

контакта 11,10)

-

выходы тактовых импульсов (номер

контакта 11,10)

![]() -

выход тактовых импульсов для ТТЛ-схемы

(номер контакта 6)

-

выход тактовых импульсов для ТТЛ-схемы

(номер контакта 6)

![]() -

строб состояния - сигнал L

- уровня, используемый для фиксации

слова-состояния МП (номер контакта 7)

-

строб состояния - сигнал L

- уровня, используемый для фиксации

слова-состояния МП (номер контакта 7)

![]() -

выходной сигнал «СБРОС» (номер контакта

1)

-

выходной сигнал «СБРОС» (номер контакта

1)

![]() -

выходной сигнал «ГОТОВ» (номер контакта

4)

-

выходной сигнал «ГОТОВ» (номер контакта

4)

![]() -

напряжение питания +5 В (номер контакта

16)

-

напряжение питания +5 В (номер контакта

16)

![]() -

напряжение питания +12 В (номер контакта

19)

-

напряжение питания +12 В (номер контакта

19)

![]() -

напряжение питания 0 В (номер контакта

18)

-

напряжение питания 0 В (номер контакта

18)

На функциональной схеме ГТИ изображен в виде микросхемы DD1 (приложение А)

2.3 Шинные формирователи КР580ВА86, КР580ВК28

2.3.1 Шинный формирователь КР580ВА86.Шинный формирователь КР580ВА86 представляет собой 8 - разрядный параллельный приемопередатчик с тристабильными выходами. Они используются для реализации различных буферных схем в микропроцессорных системах на базе Z80. На выходах микросхемы генерируются неинвертированные выходные данные. На функциональной схеме шинный формирователь КР580ВА86 изображен в виде микросхемы DD9 (приложение А).

Структурная схема шинного формирователя представлена на рисунке 6

При Н- уровне сигнала на входе Т и L,- уровне сигнала на входе ОЕ информация с выводов А(7-0) передается на выводы В(7-0). При L - уровне сигнала на входе Т и L - уровне сигнала на входе ОЕ информация с выводов В(7-0) передается на выводы А(7-0). При Н - уровне сигнала на входе ОЕ шинный формирователь переходит в высокоимпедансное состояние.

Рисунок 6 - Структурная схема шинного формирователя КР580ВА86

Опишем выводы шинного формирователя

А(7-0) - выводы данных для локальной шины МП (номер контакта 8-1)

В(7-0) - выводы данных для системной шины (номер контакта 12-19)

Т - вход управления направлением передачи (номер контакта 11)

ОЕ - вход разрешения передачи (номер контакта 9)

![]() -

напряжение питания +5 В (номер контакта

20)

-

напряжение питания +5 В (номер контакта

20)

GND - напряжение питания 0 В (номер контакта 10)

Рисунок 7 - Цоколевка шинного формирователя КР580ВА86

2.3.2 Шинный формирователь КР580ВК28. Шина данных имеет 8 разрядов с двунаправленной передачей информации. Для построения буфера достаточно одной микросхемы шинного формирователя, включенной по схеме с управляемой двунаправленной передачей информациии. Управление направлением передачи осуществляется с помощью сигнал DBIN, формируемого микропроцессором. Формирователь шины данных реализован на БИС КР580ВК28, кроме того эта БИС включает в себя системный контроллер. Выдаваемая из микропроцессора информация о состоянии микропроцессора поступает на вход этой БИС и при поступлении сигнала STSTB фиксируется в специальном внутреннем регистре состояния, где она хранится до наступления следующего цикла. Используя содержимое регистра состояния и управляющие сигналы с выхода микропроцессора DBIN, WR, HLDA БИС формирует системный управляющие сигналы INTA, IOR, IOW, MEMR, MEMW. На функциональной схеме шинный формирователь КР580ВК28 изображен в виде микросхемы DD6 (приложение А).

Рисунок 8 - Структурная схема шинного формирователя КР580ВК28

В состав структурной схемы (рисунок 8) входят: шинный формирователь - усилитель, обеспечивающий увеличение нагрузочной способности системной информационной шины; регистр (RG) - для записи и хранения слова-состояния МП; комбинационная схема (PLA) для формирования выходных управляющих сигналов.

BUSEN DB0 DB1 D0 DB2 D1 DB3 D2 DB4 D3 DB5 D4 DB6 D5 DB7 D6 D7 INTA IOR WR IOW DBIN MEMR HLDA MEMW STSTB

Рисунок 9 - Цоколевка шинного формирователя КР580ВК28

Назначение выводов БИС:

D0 - D7 - информационные входы/выходы шинного формирователя;

DB0 - DB7 - информационные входы/выходы шинного формирователя;

BUSEN - если BUSEN=0, то информационные входы/выход переходят в третье состояние;

WR - входной сигнал “Запись”;

DBIN - входной сигнал “Приём”;

HLDA - входной сигнал “Подтверждение захвата шин”;

STSTB - входной сигнал “Строб записи слова состояния”;

INTA - выходной сигнал “Подтверждение прерывания”;

IOR - выходной сигнал “Чтение УВВ”;

IOW - выходной сигнал “Запись в УВВ”;

MEMR - выходной сигнал “Чтение памяти”;

MEMW - выходной сигнал “Запись в память”.

Буферный регистр КР580ИР82

Буферный регистр КР580ИР82 представляет собой 8- разрядные параллельный регистр с тристабильными выходами. Он используется для реализации схем фиксации, буферизации и мультиплексирования в микропроцессорных системах. На выходах микросхемы КР580ИР82генерируется неинвертируемые выходные сигналы. Структурная схема регистра показана на рисунке 10, условно-графическое обозначение на рисунке 11.

Запись входных данных в буферные регистры производиться при переходе сначала STB с Н- уровня в L- уровень. При Н-уровне сигнала ОЕ выходы буферных регистров находятся в высокоимпедансном состоянии.

Опишем выводы буферного регистра КР580ИР82.

DI(7-0) - входы данных(номер контакта 8, 7, 6, 5)

STB - вход сигнала стробирования (номер контакта 11)

ОЕ - вход сигнала разрешения ввода (номер контакта 9)

DO(7-0) - выходы данных (номер контакта 12-19)

![]() -

напряжение питания +5 В (номер контакта

20)

-

напряжение питания +5 В (номер контакта

20)

GND - напряжение питания 0 В (номер контакта 10)

Рисунок 10 – Структурная схема буферного регистра КР580ИР82

Рисунок 11 – Цоколевка буферного регистра КР580ИР82

На функциональной схеме буферный регистр КР580ИР82 изображен в виде микросхемы DD9 (приложение А).

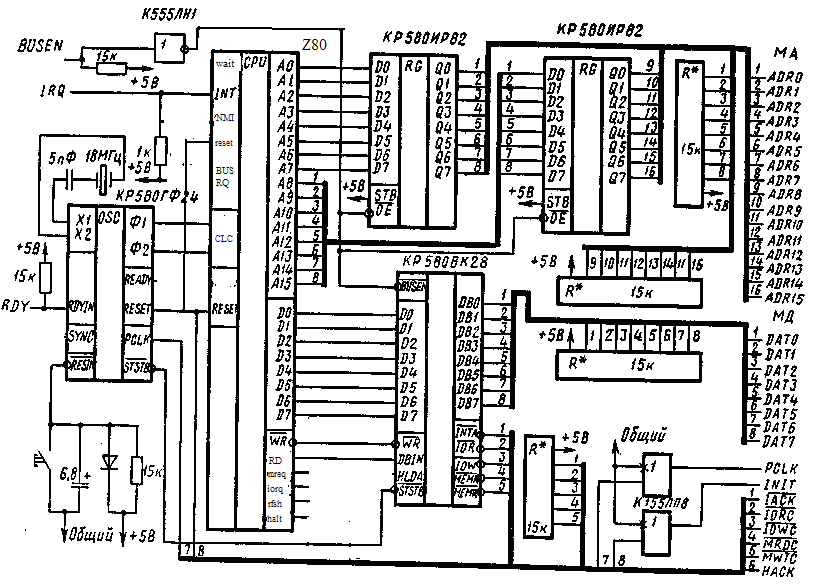

Уточненная схема микропроцессорного блока

Блок процессора, основой которого является МП БИС Z80, формирует и обрабатывает большинство сигналов магистрали микроЭВМ. Входящие в его состав ИМС служат для обеспечения работы процессора и сопряжения его с магистралью. Карта памяти микропроцессорной системы определяется микросхемотехникой построения дешифратора адреса и используемыми для управления ЗУ и УВВ стробами чтения и записи. В проектируемой МПС дешифратор адреса построен на логическом элементе.

При совмещенной карте памяти все устройства расположены в одном адресном пространстве, а обращение к регистрам устройства ввода-вывода осуществляется также как к ячейкам запоминающего устройства.

Так как режим прямого доступа к памяти не применяется, то построение дешифраторов адреса задающего устройства и устройства ввода-вывода одинаково.

Рисунок 12 - Блок микропроцессора

Упрощенная структурная схема микро ЭВМ

В общем виде разрабатываемая микропроцессорная система включается в себя :

- микропроцессор;

- генератор тактовых импульсов;

- шинный формирователь;

- буферный регистр;

- БИС ОЗУ;

- БИС ПЗУ;

- интервальный таймер;

- параллельный порт;

- устройство ввода-вывода;

- контроллер прерываний.

Рисунок 13 – Структурная схема микро ЭВМ

РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

3.1 БИС оперативно-запоминающего устройства К537РУ8

Основные характеристики К537РУ8, приведены в таблице 3

Рисунок 14 – Цоколевка БИС ОЗУ К537РУ8

Приведенные значения параметров характеризуют микросхему в диапазоне рабочих температур — 10... +70° С.

Для микросхемы памяти К537РУ8 характерно сравнительно невысокое быстродействие, определяемое временем цикла обращения, равным сотням наносекунд, высокая помехоустойчивость, малая потребляемая мощность, способ -

Таблица 3 – Статические характеристики К537РУ8

|

|

|

|

|

|

|

| ||||

|

|

|

L |

H |

L |

H |

L |

H | |||

|

5±5% |

- |

36 |

1 |

- |

0,4 |

4,1 |

0,4 |

2,4 |

1,6 |

0,1 |

ность сохранять записанную информацию при напряжении питания 1,5 ... 3 В и при значительно меньшем уровне энергопотребления, чем в режиме обращения, и возможность использования источника низковольтного резервного питания - для обеспечения свойства энергонезависимости.

Таблица истинности К537РУ8, приведена в таблице 4

Таблица 4 - Таблица истинности К537РУ8

-

Режим работы

1

Х

Х

Z

хранение

0

0

А

запись

0

1

А

считывание

Микросхема КР537РУ8 имеет словарную организацию Эти микросхемы допускают запись и считывание информации 8-разрядными словами. Информационные входы и выходы в этих микросхемах совмещены, поэтому записываемая информация вводится в микросхему, а считываемая выводится из нее по одним линиям, что обусловливает мультиплексный режим их работы.

Другой особенностью названных микросхем является наличие у них дополнительного сигнала управления ОЕ состоянием выхода. Он может подаваться одновременно с сигналом выбора CS или с некоторой задержкой. Отсутствие разрешающего состояния этого сигнала, как можно видеть из таблиц истинности, не позволяет вывести считанную информацию из микросхемы. В этом режиме выходы находятся в Z-состоянии. При наличии всех необходимых для считывания сигналов выходы переходят в функциональное состояние только по сигналу ОЕ = 0. Считываемые данные появятся на выходах спустя время выборки сигнала разрешения выхода.

Микросхемы КР537РУ8 имеет по два равнозначных сигнала выбора. Условием разрешения доступа к микросхеме является CS1 = CS2 = 0 Кроме того, надо учитывать, что в микросхеме КР537РУ8, относящейся к группе тактируемых статических ОЗУ, код адреса фиксируется перепадом одного из сигналов выбора из состояния высокого уровня в состояние низкого уровня напряжения, причем того из сигналов, который совершит указанный переход последним.

Отличительной особенностью микросхемы является способность сохранять информацию при пониженном напряжении источника питания, что расширяет сферу применения этих БИС.

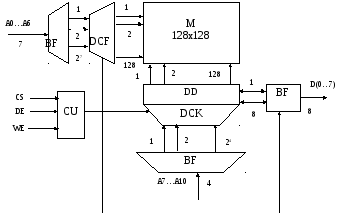

Структурная схема БИС приведена на рисунке 15.

Рисунок 15 - Структурная схема БИС ОЗУ К537РУ8

Она содержит матрицу запоминающих элементов 128х128 М, представляющую собой накопитель емкостью 16384 бит, дешифраторы адреса строк DCK и столбцов DCS, блок управления СИ, адресные и выходные формирователи BF и разрядные усилители записи/считывания DD/ Режим работы устанавливается с помощью сигналов CS1, CS2 и WE.

Чтение и запись информации ведутся словами, размерностью в 1 байт. Дешифратор адреса строки, реализует функцию одной линии из 128, а столбца - функцию выбора 8-ми линий из 128. Выходной формирователь содержит восемь усилителей считывания и следующих за ними оконченных каскадов, осуществляющих усиление и передачу данных на выход. Адресный код А0 - А11 запоминается в регистре адреса и не зависит от состояния внешних адресных шин.

На функциональной схеме БИС ОЗУ изображена в виде микросхемы DD8 (приложение А).

БИС постоянно-запоминающего устройства К541РЕ1

Микросхемы МПЗУ программируют на заводе-изготовителе по заданиях заказчика. Однако часть микросхем этой группы выпускается для общего применения в запрограммированном виде, то есть с записанной программой такого типа, как коды различных символов, значения широко применяемых математических функций, стандартные программы, подпрограммы и так далее.

Параметры микросхемы К541РЕ1 представлены в таблице 5

Таблица 5 – Характеристики микросхемы К541РЕ1

|

Емкость, бит |

|

|

|

Тип выхода |

технология |

Тип корпуса |

|

2Кх8 |

150 |

5 |

1000 |

ТТЛ-ОК |

ИИЛ-ТТЛ |

405.24-2 |

Цоколевка БИС ПЗУ К541РЕ1 приведена на рисунке 16

Микросхема К541РЕ1 относится к масочным ПЗУ. Масочные ПЗУ - это микросхемы, в которых информация записывается при изготовлением с фиксированным рисунком межсоединений, определяемым маской (фотошаблоном). В ПЗУ запоминающие элементы объединяются в двухкоординатную матрицу, образованную при пересечении входных(чисел) и выходных (разрядов) информационных шин.

Рисунок 16 - Цоколевка БИС ПЗУ К541РЕ1

В местах пересечения шин могут быть включены диоды, биполярные транзисторы и МОП-транзисторы. Наибольшее распространение получили ПЗУ на МОП-транзисторах ввиду технологической простоты и связанной с этим возможностью получения высокой степени интеграции, а также малой потребляемой мощностью.

Запоминающим элементом накопителя ПЗУ является один МОП-транзистор, выполняемый с тонким, либо с толстым слоем под затвором, в зависимости от того какая информация должна храниться в данной ячейке. Преимуществом ПЗУ, выполненных на биполярных транзисторах является более высокое быстродействие по сравнению с ПЗУ на МОП-транзисторах.

Запись информации в масочное ПЗУ производиться с помощью сменного заказного фотошаблона. Документов, определяющим хранимую в накопителе информацию, является карта заказа на данную микросхему. Изготовление маски довольно дорого, но с помощью одной маски можно запрограммировать любое число модулей памяти. Следовательно масочные ПЗУ рентабельны при крупносерийном производстве.

О бобщенная

логическая структура приведена на

рисунке 17

бобщенная

логическая структура приведена на

рисунке 17

Рисунок 17 - Обобщенная логическая структура БИС К541РЕ1

В ее состав входят дешифратор адреса строк(DCS), дешифратор адреса колонки (DCK), накопитель(М), устройство управления(СИ), буфер данных (BD).

На функциональной схеме БИС ПЗУ изображена в виде микросхемы DD7 (приложение А).

Уточненная схема подсистемы памяти

Подключение БИС ОЗУ КР580РУ8 и БИС ПЗУ КР541РЕ1 к магистралям зависит от их разрядности, а для оперативной памяти - от ее типа. В микропроцессорной системе серии Z80 удобнее всего использовать восьмиразрядные запоминающие устройства. Подключение статических ОЗУ осуществляется аналогично ПЗУ. Объем памяти определяется количеством используемых БИС. При большом их количестве в схемы ЗУ вводиться буферирование линий данных и адреса.

Схема подключение ОЗУ и ПЗУ к магистралям показа на рисунке

Рисунок 18 - Схема подключения ОЗУ и ПЗУ к магистралям

4 РАЗРАБОТКА ПОДСИСТЕМ ПРЕРЫВАНИЙ, ВВОДА/ВЫВОДА, ВЫБОР ТАЙМЕРА

4.1 Интервальный таймер КР580ВИ53

Микросхема КР580ВИ53 представляет собой программируемый трехканальный таймер-счетчик, вырабатывающий временные интервалы, управляемые программой. Три канала программируются и работают независимо друг от друга. Длительность интервалов может задаваться программно в двоичной или двоично-десятичной форме записи. Для каждого канала имеется возможность задания одного из шести режимов работы:

- выдачи сигнала прерывания по счету до конечного числа;

- программируемого ждущего одновибратора;

- генератора тактовых импульсов;

- генератора прямоугольных импульсов;

- программно-управляемого строба;

- схемотехнически управляемого строба.

Процесс формирования временных интервалов в каждом канале может управляться (начинаться, останавливаться или инициироваться вновь) внешним сигналом, подаваемым на вход разрешения работы. Работа схемы тактируется сигналами внешнего генератора с частотой до 2 МГц. Для микро-ЭВМ схема представляется либо как устройство ввода — вывода, либо как ОЗУ.

Структура микросхемы КР580ВИ53 приведена на рисунке 19, условное обозначение на рисунке 20. Упрощенно схему можно представить в виде буфера канала данных БД, схемы выборки канала ВК, определяющей, к какому каналу обращается микро-ЭВМ, и трех независимых каналов. Каждый канал включает в себя счетчик Сч, регистр режима РгР, в который записывается управляющее слово, схемы управления СУ и синхронизации канала СС и 16-разрядный счетчик.

D7

–D0

(![]() )

- двунаправленная

магистраль данных с тремя состояниями,

используемая для передачи данных и

управляющих слов между микро-ЭВМ и

выбранными регистрами.

)

- двунаправленная

магистраль данных с тремя состояниями,

используемая для передачи данных и

управляющих слов между микро-ЭВМ и

выбранными регистрами.

CS

(![]() )

(выбор

микросхемы) - вход для подачи сигнала

выбора

схемы.

)

(выбор

микросхемы) - вход для подачи сигнала

выбора

схемы.

RD(![]() )

(чтение) -

вход, на который подается сигнал на

выдачу

данных из внутренних регистров схемы

на МД

микро-ЭВМ.

)

(чтение) -

вход, на который подается сигнал на

выдачу

данных из внутренних регистров схемы

на МД

микро-ЭВМ.

Рисунок 19 - Структурная схема интервального таймера КР580ВИ53

Рисунок 20 - Цоколевка интервального таймера КР580ВИ53

WR

(![]() )

(запись) -

вход, используемый для записи данных

из МД микро-ЭВМ

в схему.

)

(запись) -

вход, используемый для записи данных

из МД микро-ЭВМ

в схему.

![]() -

входы используются для сообщения выбора

одного из каналов или регистра управления.

-

входы используются для сообщения выбора

одного из каналов или регистра управления.

CLK0

– CLK2

(![]() )

- входы разрешения работы (начальной

установки каналов0-2).

)

- входы разрешения работы (начальной

установки каналов0-2).

CATE0

– CATE2

(![]() )

- входы

тактовой частоты каналов 0-2.

)

- входы

тактовой частоты каналов 0-2.

OUT0

– OUT2

(Вых0—Вых2)

- выходы

каналов![]() .

.

Режимы работы микросхемы КР580ВИ53 задаются при начальной установке. Каналы схемы полностью независимы друг от друга, и каждый может иметь свой режим работы. Счетчик каналов представляет собой 16-разрядный счетчик с предустановкой, работающей на вычитание в двоичном либо в двоично-десятичном коде. Таким образом, загрузка всех «0» в счетчике канала дает максимальное число при счете (216 при работе в двоичном коде или 104 при работе в двоично-десятичном коде). Следует отметить, что, поскольку счетчик работает на вычитание, конечным числом на которое будет реагировать схема управления канала, является число «0», а начальным — число, загруженное в счетчик с МД микро-ЭВМ. Существует шесть режимов работы схемы.

Режим 0 - выдача сигнала прерывания по конечному числу. При работе по этому режиму на выходе канала появляется уровень «0» сразу же после установления режима работы. После загрузки числа в счетчик канала выход остается в «0» и счетчик начинает считать, если на входе разрешения установлен уровень «1». После того как достигается конечное число, на выходе устанавливается уровень «1» и остается до тех пор, пока канал не будет перезагружен режимом работы или новым числом.

Режим 1 - программируемый ждущий мультивибратор. В этом режиме выход канала после загрузки числа в счетчик канала устанавливается в уровень «0» после первого тактового сигнала, следующего за передним фронтом на управляющем входе. Одновременно начинается счет, а при достижении конечного числа на выходе устанавливается уровень «1». Таким образом, в этом режиме канал представляет собой ждущий мультивибратор с программно-устанавливаемой длительностью сигналов.

Режим 2 - генератор тактовых сигналов. В этом режиме на выходе канала через заданное число периодов тактовой частоты появляется уровень «0» длительностью в один период тактовой частоты. Число периодов определяется числом, записанным в счетчике канала.

Режим 3 - генератор прямоугольных сигналов. В этом режиме на выходе канала будет высокий уровень в течение половины интервала времени, заданного числом N (если число четное), и уровень «0» в течение другой половины.

Режим 4 - программно-управляемый строб. После установления режима 4 на выходе канала появляется уровень «1». Когда число полностью загружено в счетчик канала и на управляющий вход подан сигнал уровня «1», начинается счет и при достижении конечного числа на выходе появляется импульс уровня «0» длительностью в один период тактовой частоты.

Режим 5 — схемотехнически управляемый строб. Работа канала в этом случае аналогична работе по режиму 4 с той разницей, что счетчик канала после загрузки начинает счет только по переднему фронту на управляющем входе. Кроме того, если во время счета на управляющем входе появится передний фронт сигнала, то счет будет начат сначала.

Режим

работы каналов схемы КР580ВИ53 выбирают

с помощью простых команд вывода данных

из микро-ЭВМ путем записи управляющего

слова в регистр режима канала (![]() ).

).

При использовании таймера программа должна задать каждому каналу режим работы и число для счетчика (один или два 8- ми разрядных). Порядок программирования произвольный, то есть управляющие слова и константы для всех каналов могут быть загружены в любой последовательности с учетом двух ограничений:

- управляющее слово записывается в программируемый канал первым

- счетчик канала загружается нужным числом в определенной последовательности.

Схема подключения интервального таймера к микроЭВМ показана на рисунке 21.

На функциональной схеме интервальный таймер КР580ВИ53 изображен в виде микросхемы DD4 (приложение А).

Рисунок 21 – Схема подключения интервального таймера к МП

4.2 Программируемый блок приоритетного прерывания КР580ВН59

Микросхема

КР580ВН59

является многофункциональным

программируемым

устройством, формирующим запрос на

прерывание работы МП БИС и выдающим

на МД

микро-ЭВМ

трехбайтовую

команду CALL

![]() в ответ на последовательное поступление

трех сигналов

в ответ на последовательное поступление

трех сигналов![]() с МУ микро-ЭВМ.

Значения адресов

с МУ микро-ЭВМ.

Значения адресов

![]() и

и![]() сообщаютсясхеме

в процессе выполнения программы ее

начальной установки.

Схема имеет восемь уровней запросов

прерывания. Возможно расширение

уровней запросов прерывания до 64 за

счет девяти схем КР580ИК.59, одна из которых

является ведущей, а восемь остальных —

ведомыми.

Схемы выборки различных приоритетов

могут быть установлены

отдельно как для ведущей, так и для

ведомых схем. Существует четыре типа

обслуживания сигналов на запрос

прерывания, устанавливаемых для схемы

КР580ВН59 программно.

сообщаютсясхеме

в процессе выполнения программы ее

начальной установки.

Схема имеет восемь уровней запросов

прерывания. Возможно расширение

уровней запросов прерывания до 64 за

счет девяти схем КР580ИК.59, одна из которых

является ведущей, а восемь остальных —

ведомыми.

Схемы выборки различных приоритетов

могут быть установлены

отдельно как для ведущей, так и для

ведомых схем. Существует четыре типа

обслуживания сигналов на запрос

прерывания, устанавливаемых для схемы

КР580ВН59 программно.

При одновременном поступлении импульсов на запрос прерывания схема определяет приоритетный уровень запроса, а также выполняет прерывание текущей программы обслуживания прерывания по входу запроса с более высоким приоритетом.

Упрощенная

схема КР580ВН59 приведена на рисунке 22,

а ее

условное обозначение — на рисунке 23.

Схема имеет

двунаправленную МД с возможностью

перевода ее в третье состояние при

подаче единичного сигнала на вход

выборки ВМ

при

одновременной подаче единичных

сигналов на входы

![]() и

и

![]() .

Магистраль

данных используется для выдачи в

микро-ЭВМ команды CALL

.

Магистраль

данных используется для выдачи в

микро-ЭВМ команды CALL

![]() информации состояния, содержания

внутренних регистров, а также для

записи управляющих слов в схему.

информации состояния, содержания

внутренних регистров, а также для

записи управляющих слов в схему.

Рисунок 22 – Структурная схема КР580ВН59

Рисунок 23 – Цоколевка КР580ВН59

Кроме шины данных, обеспечивающей информационную и управляющую связь ПКП с МП, имеются следующие управляющие сигналы:

CS

(![]() )

- сигнал выбора корпуса, разрешающий

связь ПКП с шиной данных МП;

)

- сигнал выбора корпуса, разрешающий

связь ПКП с шиной данных МП;

WR(![]() )

- сигнал записи байта из шины данных в

адресуемый регистр ПКП. По этому

сигналу в ПКП осуществляется загрузка

управляющих слов инициализации (УСИ) и

управляющих слов операции (УСО);

)

- сигнал записи байта из шины данных в

адресуемый регистр ПКП. По этому

сигналу в ПКП осуществляется загрузка

управляющих слов инициализации (УСИ) и

управляющих слов операции (УСО);

RD

(![]() )

- сигнал чтения, по которому ПКП может

выдать на ШД для МП содержимое регистра

запросов прерываний РЗПР, регистра

обслуживаемых запросов РОЗПР, регистра

масок МЗПР, двоично-десятичный код

регистра запросов прерываний РЗПР;

)

- сигнал чтения, по которому ПКП может

выдать на ШД для МП содержимое регистра

запросов прерываний РЗПР, регистра

обслуживаемых запросов РОЗПР, регистра

масок МЗПР, двоично-десятичный код

регистра запросов прерываний РЗПР;

SP (ПР) - сигнал, генерируемый ПКП для передачи на вход прерывания МП;

INT

(![]() )

- подтверждение прерывания. По первому

сигналу ППР от МП контроллер выдает

в ШД код операции САLL,

а по второму и третьему — младший и

старший байты адреса начала

соответствующей программы обслуживания

прерывания;

)

- подтверждение прерывания. По первому

сигналу ППР от МП контроллер выдает

в ШД код операции САLL,

а по второму и третьему — младший и

старший байты адреса начала

соответствующей программы обслуживания

прерывания;

IR0

– IR7

(![]() )

- запрос прерывания. На эти входы ПКП

подаются сигналы запроса прерывания

от УВВ или заводятся сигналы ПР от ПКП,

работающих в расширенной системе в

качестве ведомых;

)

- запрос прерывания. На эти входы ПКП

подаются сигналы запроса прерывания

от УВВ или заводятся сигналы ПР от ПКП,

работающих в расширенной системе в

качестве ведомых;

![]() -

адрес. Входной сигнал, подключаемый

обычно к младшей линии Ао

шины адреса и совместно с УСИ и УСО

используемый для инициализации и чтения

состояния ПКП;

-

адрес. Входной сигнал, подключаемый

обычно к младшей линии Ао

шины адреса и совместно с УСИ и УСО

используемый для инициализации и чтения

состояния ПКП;

INTA

(![]() )-

ведущий/ведомый. Сигнал 1 на этом входе

ПКП означает, что контроллер является

ведущим по отношению к аналогичным ПКП;

)-

ведущий/ведомый. Сигнал 1 на этом входе

ПКП означает, что контроллер является

ведущим по отношению к аналогичным ПКП;

CAS0

–CAS2

(![]() )-

линии каскадирования. Используются

только в случае применения нескольких

ПКП в системе. Эти линии образуют

локальную шину, двунаправленные линии

которой являются выходными в случае

использования ПКП в качестве ведущей

{при этом выдается номер ведомого ПКП)

и входными, если ПКП выступает в качестве

ведомого.

)-

линии каскадирования. Используются

только в случае применения нескольких

ПКП в системе. Эти линии образуют

локальную шину, двунаправленные линии

которой являются выходными в случае

использования ПКП в качестве ведущей

{при этом выдается номер ведомого ПКП)

и входными, если ПКП выступает в качестве

ведомого.

Режимы работы микросхемы КР580ВН59 задаются при ее начальной установке. Существует четыре режима работы схемы КР580ВН59:

- полностью установленные (неизменные) приоритеты прерывания;

- перемещаемые приоритеты прерывания;

- специальное маскирование приоритетов прерывания;

- считываемые прерывания.

Указанные режимы работы схемы различаются алгоритмами задания уровней приоритетов запросов прерывания и устанавливаются в зависимости от записи в схему слов управления (СУ). Запись СУ в схему возможна в любой момент времени после выполнения команд начальной установки. Любой вход запроса прерывания можно выборочно маскировать с помощью записи слова управления первого вида (СУ1) в РгМП. Состояние РгМП воздействует на состояние РгОП. Если запрос на прерывание уже сформирован схемой на какой-либо уровень, то любой из уровней с более низшим приоритетом не в состоянии прервать работу микро-ЭВМ, если в схему не записывается специальная команда EOI (конец прерывания); запись ее осуществляется с помощью слова управления второго вида (СУ2). Команда позволяет обнулить разряд РгОП, соответствующий текущему прерыванию. Эту же цель можно также реализовать с помощью перевода работы схемы к специальному режиму маскирования, используя слово управления третьего вида (СУЗ).

1)

Режим полностью установленных приоритетов

прерываний

схема имеет

сразу после окончания выполнения команд

начальной установки, и он не требует

дополнительных слов управления для

его задания. Приоритеты прерывания в

нем последовательно уменьшаются от

высшего

(на входе

![]() )

до

низшего (на входе

)

до

низшего (на входе

![]() ),

и

их порядок

неизменен.

),

и

их порядок

неизменен.

2) Существует два вида перемещаемых приоритетов прерываний: вид А и вид В. Перемещаемый приоритет вида А отличается от полностью установленного режима приоритетов тем, что после выполнения команды конца прерывания автоматически этот запрос определяется схемой КР580ВН59 как низший по уровню.

Запись

команды прерывания со специфическим

сдвигом позволяет схеме работать по

перемещаемому типу прерываний

вида В. В результате выполнения этой

команды наивысший

по приоритету из установленных в «1»

разрядов РгОП

сбрасывается

и происходит смена приоритетов входных

уровней схемы. Низший по приоритету

уровень задается

в разрядах

![]() СУ2. Такой

способ задания приоритетов дает

дополнительные программные возможности

управления каналами запросов прерывания.

СУ2. Такой

способ задания приоритетов дает

дополнительные программные возможности

управления каналами запросов прерывания.

3)

При работе в режиме

считываемых прерываний

прерывание

работы микро-ЭВМ осуществляется не по

входу

![]() МП БИС, а

программным путем. Схема КР580ВН59 не

использует свой вход

МП БИС, а

программным путем. Схема КР580ВН59 не

использует свой вход

![]() и выход

и выход![]() для передачи

запроса прерывания в микро-ЭВМ.

для передачи

запроса прерывания в микро-ЭВМ.

Установка

режима считываемых прерываний

инициируется записью в схему СУ3

с единицей,

записанной в разряде Д2.

При получении СУ3

схема ведет

себя так же,

как и при получении уровня «0» сигнала

![]() на входе

на входе

![]() .

Так, схема

определяет наивысший по приоритету

запрос на прерывание из запросов,

зафиксированных в РгЗП,

и записывает

«1» в соответствующий разряд РгОП.

При следующем

такте чтения информации из того же

адреса она будет выдавать слово состояния

с указанием наличия запроса на прерывание

(«1»—в разряде

.

Так, схема

определяет наивысший по приоритету

запрос на прерывание из запросов,

зафиксированных в РгЗП,

и записывает

«1» в соответствующий разряд РгОП.

При следующем

такте чтения информации из того же

адреса она будет выдавать слово состояния

с указанием наличия запроса на прерывание

(«1»—в разряде

![]() )

и номера

приоритета запроса прерывания, указанного

в разрядах

)

и номера

приоритета запроса прерывания, указанного

в разрядах

![]() .

.

Таким образом, при работе по считываемому типу начало обслуживания запросов на прерывание, поступивших на вход схемы, осуществляется программно при обращении к схеме (с помощью записи СУ3). Определение наличия запроса и сообщение его номера производятся путем чтения из схемы слова состояния. Внешние устройства теперь не могут прерывать выполнение текущей программы после подачи импульса запроса прерывания на входе схемы. Места в программах, когда микро-ЭВМ считывает сигналы прерывания, фиксированы. Каждый ввод нового запроса прерывания из схемы должен сопровождаться процессом записи в нее СУЗ и чтением слова состояния.

Схема подключения контроллера приоритета прерываний показан на рисунке 24.

На функциональной схеме программируемый блок приоритетного прерывания КР580ВН59 изображен в виде микросхемы DD2 (приложение А).

Рисунок 24 - Схема подключения контроллера приоритета прерывания к МП

4.3 Программируемое устройство ввода - вывода параллельной информации различного формата КР580ВВ55

Микросхема КР580ВВ55 представляет собой программируемое устройство, используемое для ввода — вывода параллельной информации. Схема позволяет осуществлять обмен 8-разрядными данными по трем каналам: А, В, С. Направление обмена и режим работы для каждого канала задается программно. Каналы служат для передачи как данных, так и управляющих сигналов.

Упрощенно схема состоит из регистра управления и трех регистров, предназначенных для ввода — вывода данных.

Структура микросхемы КР580ВВ55 приведена на рисунке 25, а ее условное обозначение—на рисунке 26. Назначение выводов:

D0-D7

(![]() )

- двунаправленная магистраль данных

для передачи данных, управляющих слов

и информации состояния;

)

- двунаправленная магистраль данных

для передачи данных, управляющих слов

и информации состояния;

PA0

– PA7

(![]() )-

двунаправленная магистраль данных

канала А;

)-

двунаправленная магистраль данных

канала А;

PB0

– PB7

(![]() )- двунаправленная

магистраль данных канала В;

)- двунаправленная

магистраль данных канала В;

PC0

PC7

(![]() )

- двунаправленная

магистраль данных канала С

(магистрали

каналов передачи данных, управляющих

сигналов и сигналов запроса на прерывание

от ВУ и _МП БИС);

)

- двунаправленная

магистраль данных канала С

(магистрали

каналов передачи данных, управляющих

сигналов и сигналов запроса на прерывание

от ВУ и _МП БИС);

CS

(![]() )-

выбор устройства;

)-

выбор устройства;

![]() -

входы, необходимые для выбора одного

из каналов

А, В, С или

регистра управления;

-

входы, необходимые для выбора одного

из каналов

А, В, С или

регистра управления;

RD

(![]() )

(чтение)

— вход, на который подается сигнал на

выдачу данных из внутренних регистров

схемы на МД;

)

(чтение)

— вход, на который подается сигнал на

выдачу данных из внутренних регистров

схемы на МД;

RESET (R) - вход, используемый для начальной установки схемы. При подаче сигнала на этот вход содержание всех внутренних регистров устанавливается на ноль;

WR(![]() )

(запись) -

вход записи данных в схему.

)

(запись) -

вход записи данных в схему.

Рисунок 25 – Структурная схема КР580ВВ55

Для

микро-ЭВМ схему можно представить

состоящей либо из четырех ВУ, либо из

четырех адресов памяти. Для формирования

сигнала выборки устройства, подаваемого

на вход

![]() ,

можно использовать шины

,

можно использовать шины![]() МА

микро-ЭВМ.

МА

микро-ЭВМ.

Рисунок 26 – Цоколевка КР580ВВ55

При

обращении к схеме как к четырем ВУ входы

![]() и

и

![]() должны быть

должны быть

подключены

к шинам

![]() и

и

![]() МУ микро-ЭВМ.

При обращении к схеме как к четырем

адресам памяти ее входы

МУ микро-ЭВМ.

При обращении к схеме как к четырем

адресам памяти ее входы

![]() и

и

![]() должны

быть соответственно подключены к шинам

должны

быть соответственно подключены к шинам![]() и

и

![]() МУ микро-ЭВМ.

МУ микро-ЭВМ.

Схема может выполнять следующие функции: буферизацию (при асинхронном режиме обмена данными); преобразование формата данных- сопряжение микро-ЭВМ с ВУ в режиме прерывания.

Режимы работы микросхемы К580ВВ55 задаются при ее начальной установке. Четыре подадресных регистра схемы включают в себя три регистра каналов ввода - вывода данных (А, В, С) и регистр управления. Регистр канала С может быть подразделен на два четырехразрядных регистра ввода - вывода данных, к которым осуществляется доступ как к отдельным независимым регистрам (рисунок 7). Имеется возможность подразделения трех каналов на две группы (рисунок 8). В этих группах каналы А и В используются для обмена данными с микро-ЭВМ, а отдельные шины канала С - для записи управляющих сигналов.

Тип 0 — это простой ввод — вывод данных по трем 8-разрядным каналам, причем канал С может быть подразделен на два 4-разрядных канала. Каждый из каналов может быть использован отдельно для ввода или вывода информации. При работе схемы в этом режиме никаких дополнительных сигналов управления не требуется.

Тип 1. Позволяет осуществлять обмен данными по каналам А ц В с помощью сигналов управления, передаваемых по каналу С. Для каналов А и В существует четыре комбинации взаимных направлений передачи данных:

а) каналы А и В работают в режиме вывода данных;

б) каналы А и В работают в режиме ввода данных;

в) канал А работает в режиме ввода, а В - в режиме вывода данных;

г) канал А работает в режиме вывода, а В - в режиме ввода данных.

Незадействованные для управляющих сигналов шины канала С могут быть использованы для ввода - вывода информации. Направление передачи информации по этим шинам определяется управляющим словом, записанным в регистре управления.

Тип

2.

При работе по этому типу

канал А

используется

для двунаправленной передачи данных,

канал С -

для записи управляющих сигналов,

обеспечивающих передачу данных по

каналу А.

Управляющие

сигналы являются комбинацией

сигналов, необходимых

при работе канала А

по типу

1.Шины

![]() могут быть

задействованы для ввода

- вывода или передачи управляющего

сигнала.

могут быть

задействованы для ввода

- вывода или передачи управляющего

сигнала.

Комбинации режимов задаются путем записи управляющего слова по адресу регистра управления схемы. В регистр управления можно только записывать управляющие слова. Чтение информации из регистра управления недопустимо.

Схема подключения клавиатуры и дисплея с использованием КР580ВВ55 представлена на рисунке 27

На функциональной схеме программируемое устройство ввода - вывода КР580ВВ55 изображен в виде микросхемы DD10 (приложение А).

Рисунок 27 - Схема подключения клавиатуры и дисплея к микро ЭВМ

4.2 Программируемый контроллер клавиатуры и индикации КР580ВВ79

БИС КР580ВВ79 представляет собой программируемое интерфейсное устройство, предназначенное для ввода и вывода информации в системах на основе микропроцессоров КР580ИК80А и Z80. Микросхема программируемого контроллера клавиатуры и индикации (ПККИ) состоит из двух основных функционально разделимых частей; клавиатурной и дисплейной. Клавиатурная часть предназначена для сопряжения с клавиатурой печатающих устройств и с произвольными наборами переключателей. Дисплейная часть ПККИ позволяет отображать информацию с помощью индикаторов различных типов (дисплеев). Упрощенная структурная схема ПККИ приведена на рисунке 27.

В состав БИС входят: буферы клавиатуры и датчиков (ВF), включающие также схему управления и устранения дребезжания клавиатуры, предназначенные для хранения входной информации в режимах сканирования клавиатуры, наборов датчиков и ввода по стробу; схема управления вводом/выводом (RWCU), вырабатывающая сигналы управления обменом с МП и внутренними пересылками данных и команд; буферы канала данных (ВD), предназначенные для обмена информацией между ПККИ и МП.

Рисунок 28— Структурная схема программируемого контроллера клавиатуры и индикации КР580ВВ79

ОЗУ клавиатуры датчиков (SТАСК), работающее по принципу ПРО и предназначенное для хранения кодов позиций клавиш и состояний ключей датчиков; ОЗУ отображения (RАМ), сохраняющее информацию, отображаемую на дисплее; регистр адреса ОЗУ отображения (RGА), предназначенный для хранения адреса данных, записываемых или считываемых микропроцессором; схема управления и синхронизации (СU), состоящая из регистров хранения команд и счетчика синхронизации и осуществляющая управление работой всей микросхемы; схема анализа состояния ОЗУ-датчиков (STCU) контролирующая число символов в ОЗУ и формирующая сигнал прерывания INТ; регистры ОЗУ отображения (RG), предназначенные для хранения данных отображаемых на выходах каналов А и В; счетчик сканирования (СТ), вырабатывающий сигналы сканирования клавиатуры, датчиков и дисплея.

Назначение входных, выходных и управляющих сигналов ПККИ:

RET (7-0) – (8;7;6;5;2;1; 39; 38) - входы линий возврата, служащие для подачи сигналов от датчиков через контакты клавиш или ключа;

SH – (36) - вход сигнала сдвига, используемого для ска-нирования клавиатуры;

V/ STB – (37) - вход сигнала управления для режима сканирования клавиатуры или стробирующего сигнала для режима ввода по стробу;

R – (10) - вход сигнала чтения L-уровня, разрешающего передачу информации из ПККИ в канал данных МП;

W – (11) - вход сигнала записи L-уровня, разрешающего передачу информации из канала данных МП в ПККИ;

![]() -

(21) - вход для управления записью/чтением

данных или команд; при сигнале Н-уровня

происходит запись команды или чтения

состояния ПККИ, при сигнале L-уровня

— запись или чтение данных;

-

(21) - вход для управления записью/чтением

данных или команд; при сигнале Н-уровня

происходит запись команды или чтения

состояния ПККИ, при сигнале L-уровня

— запись или чтение данных;

CS –(22) - вход сигнала выбора микросхемы; L-уровень сигнала разрешает работу схемы;

CLK – (3) - вход сигнала синхронизации микросхемы;

CLR – (9) - вход сигнала установки ПККИ в исходное состояние;

D(7-0) – (19;18;17;16;15;14;13;12) - входы/выходы канала данных;

DSP A( 3-0) – (24-27) - выхода канала А;

DSP B( 3-0) – (28-31) - выхода канала В;

BD – (23) - выход канала гашения отображения уровня L;

S(3-0) – (35;34;33;32) - выходы сигналов сканирования клавиш клавиатуры или набора датчиков и дисплея;

INT – (4) - выход сигнала прерывания;

Ucc – (40) - вход напряжения питания ( + 5 В) ;

GND –(20) - вход напряжения питания (0 В).

Клавиатурная часть ПККИ имеет три режима работы: режим сканирования клавиатуры, режим определения состояния набора датчиков и режим ввода по стробу.

В режиме сканирования клавиатуры байт информации, вводимой в SТАСК, содержит код позиции нажатой клавиши и два бита сигналов управления. Разряду D7 соответствует состояние сигнала V/STB, а разряду D6 — сигнала SH. Разряды D3 - D5 определяют номер строки нажатой клавиши, а разряды D0 - D2 — номер столбца. После записи кода позиции клавиши в SТАСК на выходе INT устанавливается напряжение Н-уровня. В этом режиме с помощью схемы управления и устранения дребезжания клавиатуры осуществляется также отработка ситуаций, возникающих при одновременном нажатии клавиш.

Режим сканирования клавиатуры может выполняться с обнаружением двух нажатых клавиши. В этой разновидности режима вводится код только одной нажатой клавиши. Одновременное нажатие двух клавиш не воспринимается до тех пор, пока одна из них не будет отпущена. Другая разновидность режима разрешает одновременное нажатие N клавиш (не более восьми), распознает их и вводит коды позиций в SТАСК в соответствии с порядком обнаружения. В последнем варианте с помощью специальной команды можно задать режим обнаружения ошибок, в котором наличие двух нажатых клавиш рассматривается как одновременное нажатие и вызывает установку в слове состояния ПККИ флага ошибки.

В

режиме определения состояния набора

датчиков по входам RЕТ (7 — 0) производится

построчный ввод в SТАСК состояний

ключей датчиков. При этом SТАСК работает

как обычное ОЗУ, каждая ячейка которого

загружается состоянием соответствующей

строки набора датчиков. В этом режиме

не используются входы

![]() и SН и схема устранения дребезжания

клавиатуры. При обнаружении изменения

состояний датчиков на выходе INТ в

конце интервала сканирования

устанавливается, как правило, напряжениеH-уровня.

и SН и схема устранения дребезжания

клавиатуры. При обнаружении изменения

состояний датчиков на выходе INТ в

конце интервала сканирования

устанавливается, как правило, напряжениеH-уровня.

В

режиме ввода по стробу ввод в SТАСК со

входов RЕТ(7 — 0) происходит при переходе

стробирующего сигнала на входе

![]() из состоянияL-уровня

в состояние H-уровня.

Вход SН и схема устранения дребезжания

клавиатуры в этом режиме не используются,

а длительность стробирующего сигнала

должна быть не меньше периода частоты

синхронизации микросхемы.

из состоянияL-уровня

в состояние H-уровня.

Вход SН и схема устранения дребезжания

клавиатуры в этом режиме не используются,

а длительность стробирующего сигнала

должна быть не меньше периода частоты

синхронизации микросхемы.

Дисплейная часть ПККИ имеет два режима работы: режим ввода слева и режим ввода справа со сдвигом.

В режиме ввода слева каждой позиции дисплея соответствует определенная строка в ОЗУ отображения (RАМ). Нулевому адресу в RАМ соответствует крайний левый символ. Ввод символов, начиная с нулевого адреса, вызывает построчное отображение информации слева направо.

Ввод справа со сдвигом используется в электронных калькуляторах. Здесь ввод первого символа производится в крайнюю справа позицию дисплея. Следующий ввод также производится в крайнюю правую позицию, а все отображение сдвигается на один символ влево. В этом режиме нет прямого соответствия между позицией отображаемого символа и адресом строки RАМ, поэтому рекомендуется использовать последовательный ввод, начиная с нулевого адреса.

Информация на выходах DSРА (3 - 0) канала А соответствует разрядам D7 - D4 канала данных, а на выходах DSРВ(3-0) — разрядам D3 - D0.

Сигналы сканирования на выходах S(3 — 0) вырабатываются счетчиком сканирования (СТ), обеспечивающим два вида сигналов сканирования: кодированные сигналы и дешифрированные. Кодированные сигналы сканирования являются выходами четырех последних разрядов счетчика синхронизации и должны дешифрироваться внешним дешифратором для получения сигналов сканирования клавиатуры и индикаторов.

Режимы работы ПККИ устанавливаются программно с помощью записи в него команд по каналу данных. Перед программированием режима микросхема должна быть установлена в исходное состояние подачей на вход СLR напряжения H-уровня длительностью не менее шести тактовых импульсов.

Для контроля состояния ПККИ микропроцессор может считывать слово-состояние БИС из внутреннего 8-разрядного регистра слова-состояния.

Разряды D3 — D0 слова-состояния определяют число символов в ОЗУ клавиатуры и датчиков. Разряды D4 и D5 представляют флаги ошибок и используются в клавиатурном режиме и режиме ввода по стробу. Разряд D4 устанавливается при чтении символа из пустого ОЗУ, а разряд D6— при записи в заполненное ОЗУ. Разряд D6 в режиме набора датчиков устанавливается в том случае, если происходит замыкание хотя бы одного ключа датчиков. В режиме сканирования клавиатуры при записи команды «сброс прерывания — установка режима обнаружения ошибок» разряд D6 выполняет функцию флага ошибки. Он устанавливается при обнаружении одновременного нажатия нескольких клавиш. Разряд D7 слова состояния информирует о прекращении доступа к ОЗУ-отображения.

На рисунке 29 показано включение микросхемы в микропроцессорную систему, управляющую работой клавиатуры и дисплея.

Рисунок 29 - Схема включения программируемого контроллера клавиату- ры и индикации КР580ВВ79 в микропроцессорную систему

На функциональной схеме программируемый контроллер клавиатуры и индикации КР580ВВ79 изображен в виде микросхемы DD11 (приложение А).

На рисунке 30 изображена уточненная схема микро ЭВМ.

Рисунок 30 - Уточненная структурная схема микро ЭВМ

5 РАЗРАБОТКА АЛГОРИТМА РАБОТЫ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ

Обработка

информации от цифровых датчиков и выдача

управляющего воздействия y1

производится путем ввода значений x1,

x2,

x3,

x4

и вычисления булевой функции f1(x1,

x2,

x3,

x4)=

![]() .

.

При единичном значении f1 вырабатывается управляющий сигнал y1=1 длительностью t1=10мкс.

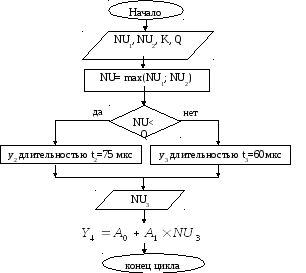

При обработке информации с аналоговых датчиков ПМ принимает коды NU1, NU2 с выходов АЦП и код константы К с регистра пульта управления. Далее вычисляется значение функции NU=f2(NU1,NU2, К)=max(NU1,NU2) и сравнивается с константой Q, хранящейся в ПЗУ. В зависимости от результатов сравнения вырабатывается (аналогично y1) один из двух двоичных управляющих сигналов y2 или y3 заданной длительности по следующему правилу: если NU<Q, то выдать y2 длительностью t2=75 мкс, иначе выдать y3 длительностью t3=60мкс.

Далее формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3 и производится вычисление по формуле:

![]()

Значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

Все двоичные переменные и константы, участвующие в вычислениях: NU1, NU2, NU3, К, Q, A0, A1, Y4 рассматриваются как целые без знака.

После выдачи всех управляющих воздействий проверяется состояние тумблера «СТОП» на пульте управления. Если СТОП=0, цикл управления начинается с начала, иначе выполняется процедура останова системы, включающая следующие действия: формируется сигнал установки системы в исходное состояние путем подачи на линию начальной установки интерфейса двух прямоугольных импульсов длительностью 30 мкс интервалом 30 мкс, выполняется команда процессора СТОП.

Блок-схема заданного цикла управления разбита на две части (рисунок 31 и 32), общая блок-схема представлена на рисунке 33.

Рисунок 31– Цикл 1 управляющей программы

В общем виде управляющая программа состоит из двух циклов, по результатам выполнения которых осуществляется выдача управляющих воздействий на индикацию. Управляющая программа выполняется до тех пор пока на пульте управления не будет включен тумблер «СТОП».

Цикл

1 управляющей программы заключается в

вводе в центральный процессор значений

сигналов из цифровых датчиков, вычислении

булевой функции

![]() .

Если по результатам вычисления получилось,

что управляющий сигнал стал равен 1, то

выдается управляющий сигнал длительностью

t1=10

мкс. Если же управляющий сигнал принял

значение 0, то булевая функция

.

Если по результатам вычисления получилось,

что управляющий сигнал стал равен 1, то

выдается управляющий сигнал длительностью

t1=10

мкс. Если же управляющий сигнал принял

значение 0, то булевая функция

![]() вновь.

вновь.

Цикл 2 управляющей программы заключается в воде в центральный процессор двоичных кодов с выходов АЦП и констант К и Q, вычислении значения функции f2(NU1, NU2, К), по выражению NU= max(NU1; NU2). Если по результатам вычисления получилось, что NU<Q, то вырабатывается управляющий сигнал длительность

t2=75

мкс, если же получилось что NU>Q,

то вырабатывается управляющий сигнал,

длительностью t3=60мкс.

Далее осуществляется ввод в центральный

процессор двоичного кода с выхода АЦП

NU3

и производиться вычисление функции

![]() .

.

Цикл 2 изображен на рисунке 32

Рисунок 32 - Цикл2 управляющей программы

Рисунок 33– Общая блок-схема программы