- •Введение

- •Постановка задачи

- •1 Выбор и обоснование структурной схемы

- •Разработка алгоритма функционирования мк

- •Окончание работы? (10)

- •Разработка принципиальных электрических схем блоков

- •3.1 Микропроцессорный блок

- •3.2 Блок памяти

- •3.3 Блок ввода аналоговых данных

- •3.4 Интерфейсный блок

- •3.5 Блок отображения и вывода информации

- •4 Разработка принципиальной электрической схемы мк

- •Разработка программного обеспечения

- •Заключение

- •Список литературы

- •Приложение a.

- •Ввод данных с ацп

- •Mvi a, 00000000b запуск ацп;

- •Mvi a, 00000001b остановить преобразование в ацп;

- •Арифметические вычисления

- •Деление аккумулятора а на значение в l

- •Преобразование к семиразрядному числу

- •Вывод результата на цап и индикаторы

- •Преобразование в двоично-десятичный код

- •Вывод на индикаторы

- •Подпрограмма деления

-

3.2 Блок памяти

Блоком памяти в проектируемом устройстве являются ПЗУ и ОЗУ. В первом хранятся коды программы, а во втором – вводимые, промежуточные и выводимые данные.

Аппаратным путем ячейкам памяти ПЗУ и ОЗУ можно присвоить любые адреса, начиная от 0 до 65535, но при этом надо учитывать то обстоятельство, что при включении питания и после сброса микропроцессор всегда начинает считывать код команды, расположенный в ячейке с адресом 0000H.

Для разделения области ПЗУ и ОЗУ необходимо дешифрировать верхние разряды адреса. После подачи сигнала сброса на процессор счётчик команд принимает значение 0, то есть выполнение программы начинается с адреса 0. Следовательно, область ПЗУ, в котором хранится код программы, должна начинаться с адреса 0. Тогда верхний адрес ПЗУ 2 Кбайт будет равен 2047 (07ffH), что соответствует двоичному 0000011111111111. Область ОЗУ начинается со следующих адресов. Нижний адрес ОЗУ в этом случае 2048 (0800H), то есть 0000100000000000. Верхняя граница в 2 Кбайт соответствует адресу 4095 (0fffH), то есть 0000111111111111. Как видно, для адресации к памяти используются только нижние 12 бит адреса А0-А11. При этом биты А15-А12 принимают значение 0 как для ПЗУ, так и для ОЗУ, а бит А11 принимает значение 0 для ПЗУ и 1 для ОЗУ. Это обстоятельство и применяется для построения дешифратора, разделяющего области ПЗУ и ОЗУ. Также учитывается, что при обращении к памяти, ЦПМ устанавливает в 0 сигналы MEMW или MEMR, обращение ПЗУ возможно только при чтении данных, но не при их записи. Сигналы с дешифратора имеют активный уровень 0 и подключены ко входам выборки кристалла CS и перевода выходов в Z-состояние OE микросхем ОЗУ и ПЗУ. Выводы микросхем объединены в общую шину данных соответствующими разрядами и подключаются к ЦПМ.

Таблица 1 – Карта памяти

|

Тип ЗУ |

ША |

А15 |

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

|

ПЗУ |

0000h |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

07FFh |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

ОЗУ |

0800h |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0FFFh |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

Микропроцессоры семейства К1821 адресуют пространство ЗУ объемом 1 Мбайт с байтовой и двухбайтовой организацией. Время цикла чтения/записи без использования тактов ожидания при частоте синхронизации 5 МГц составляет менее 600 нс, а время выборки порядка 160 нс. Запоминающие устройства микропроцессорных систем на базе БИС МП К1821ВМ85 имеют байтовую организацию и реализуются так же, как и ЗУ для систем на базе БИС КР580 и 8086А.

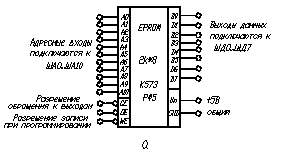

Поэтому, в качестве ПЗУ можно использовать БИС К573РФ5 (DD12). Это ПЗУ может быть реализовано на базе одной микросхемы памяти с ультрафиолетовым стиранием, имеющей организацию 2к*8 и имеет время выборки адреса 450 нс. ИМС имеет 11 адресных входов, 8 выходов данных, входы разрешения программирования WE, выборки кристалла CЕ, разрешения выходов ОЕ.

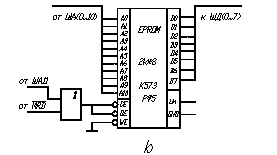

Назначение выводов микросхемы памяти и функциональная схема представлена на рисунке 6(а,б).

Рисунок 6 – Назначене выводов микросхемы памяти (а) и функциональная схема ПЗУ (б)

В качестве проектируемого ОЗУ выбираем статическое ОЗУ КР537РУ8 (DD18) объёмом 2 Кбайт. ОЗУ бывают статического и динамического типов. Так как объем оперативной памяти в проектируемом контроллере мал, то нет смысла применять в нем динамическое ОЗУ. А также применение ОЗУ статического типа позволяет решить задачу сохранения данных в памяти (в отличие от динамического ОЗУ статическое не требует циклов регенерации памяти). Это позволяет существенно упростить аппаратную часть контроллера. Для записи данных с входов D0-D7 в микросхему необходимо на входах А0-А9 установить требуемый адрес ячейки памяти, подать на входы CS и WR напряжение низкого уровня. Для чтения данных из памяти необходимо установить адрес ячейки, на вход CS подать напряжение низкого уровня, а на вход WR – высокого. Функциональное обозначение и назначение выводов данной микросхемы представлено на рисунке 7.

Рисунок 7 - Функциональное обозначение и назначение выводов

БИС КР537РУ8