лекции / логические элементы

.pdf

|

|

|

|

Конъюнкция – логическое умножение |

|

X1 |

|

Y |

|||

& |

|||||

|

|

||||

X2 |

|

y x1 x2 |

|||

|

|||||

|

|

|

|

|

|

Дизъюнкция – логическое сложение

X1 |

|

Y |

|

||

|

|

||||

|

|

|

|

||

X2 |

1 |

|

y x1 |

x2 |

|

|

|||||

|

|

|

|

||

|

|

|

|

|

|

Элемент Шеффера, И-НЕ

X1 |

|

|

|

|

Y |

|

|

|

|

|

|

|

x1 |

|

|

|

|

x2 |

|

|

|

y |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

X2 |

& |

|

|

|

|

|

|

|

0 |

|

|

0 |

|

|

1 |

||||||||||||||||||

|

|

|

|

|

|

y |

|

|

|

, |

0 1 1 |

||||||||||||||||||||||

|

|

|

|

|

x1 x2 |

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

|||||||||||||

|

|

|

|

Элемент Пирса, ИЛИ-НЕ |

|

|

|

|

|

||||||||||||||||||||||||

X1 |

|

|

|

|

Y |

|

|

|

|

|

|

|

x1 |

|

|

|

|

x2 |

|

|

|

y |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

X2 |

1 |

|

|

|

|

|

|

|

0 |

|

|

0 |

|

|

1 |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

y x1 x2 , |

0 1 0 |

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

0 |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

0 |

|||||||||||||

|

|

|

|

Элемент неравнозначности |

|||||||||||||||||||||||||||||

X1 |

|

|

|

|

|

|

|

|

y |

|

|

x2 x1 |

|

, |

|

y x1 x2 , |

|||||||||||||||||

|

|

|

|

Y |

x1 |

x2 |

|||||||||||||||||||||||||||

=1 |

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

X2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Элемент И-ИЛИ-НЕ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

X1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

X2 |

|

|

1 |

|

|

|

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

X3 |

|

|

& |

|

|

|

|

y x1 x2 x1 x2 |

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

X4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

RS – триггер на элементах И-НЕ |

|

|

|

|

|

|

||||

|

Q S RQt 1 |

a a |

Q S RQt 1 |

|

|

|

|

|

|

||

S |

& |

Qt 1 |

|

Временная диаграмма: |

|

|

|||||

|

|

|

|

|

|

|

|||||

|

|

|

S |

Т |

Q |

S |

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

||

R |

& |

Q |

R |

|

|

R |

|

|

t |

|

|

|

|

Q |

Qt 1 |

|

|

t |

|

|

|||

|

|

|

|

|

|

Q |

|

|

t |

|

|

|

Построение RS – триггера на ИЛИ-НЕ элементах |

|

|

|

|

||||||

|

|

|

Q RS RQt 1 R S Qt 1 |

|

|

|

|

|

|

||

|

|

|

R S Qt 1 R S Qt 1 |

|

|

|

|

|

|

||

S |

|

1 |

Qt 1 |

S Т |

Q |

S |

|

|

t |

|

|

|

|

|

|

R |

|

|

t |

|

|

||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

R |

Q |

Qt 1 |

|

|

t |

|

|

|

|

|

|

|

Q |

|

|

t |

|

|

|

R |

|

1 |

Q |

|

|

|

|

|

|

|

|

|

Счетные триггеры |

|

|

|

|

|

|

|

|||

|

Схема асинхронного, двухтактного T – триггера: |

|

|

|

|

|

|||||

S |

|

|

|

|

|

|

Qt 1 Qt T Qt |

T |

|||

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

&1 |

&3 |

&5 |

&3 |

C T Qt |

Qt 1 |

|

|||

T c |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

&2 |

&4 |

&6 |

&4 |

Q |

0 |

1 |

0 |

1 |

|

R |

|

0 |

1 |

1 |

0 |

|

|||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

|

|

|

Qt+1 |

||

|

|

|

|

|

|

|

|

|

|

||

2 |

|

|

|

|

|

|

|

|

|

|

|

Синхронный T – триггер

Строится на базе двухтактных RS – триггерах.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

&2 |

|

S |

TТ |

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

t |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

C |

|

|

|

|

|

|

|

Т |

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

R |

|

|

|

|

|

|

|

Qt 1 |

|

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

&2 |

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D – триггер (триггер с задержкой по времени)

D |

S Т |

|

Q |

|

C

&2 R  Q

Q

С |

t |

|

D |

||

t |

||

Q |

||

t |

||

1Т |

||

|

||

2 |

T |

|

|

JK – триггер (универсальный)

Qt 1 \ JK  00 01 11 10

00 01 11 10

0 |

|

0 |

0 |

1 |

1 |

Q JQt Qt K |

|

||||||

|

||||||

|

||||||

1 |

|

1 |

0 |

0 |

1 |

|

|

|

|||||

|

|

|||||

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

&2 |

|

S |

TТ |

|

|

|

Q |

||

J |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

|

|

R |

|

|

|

|

|

|

|

|

&2 |

|

|

|

|

Q |

||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3

Функциональная схема трехразрядного параллельного регистра,

на базе однотактных D – триггерах.

T

X0 &2 D

Q0

K

T

X1 &2 D

Q1

K

T

X2 &2 D

Q2

Запись слова

Установка 0-я K

Трехразрядный, параллельный, парафазный регистр на синхрон-

ном RS – триггере

X0 R T

СQ0

X0 S

X1 R T

C Q1

X1 S

X2 R T

C Q2

X2 S

V – запись слова

4

Пример передачи кода слова между двумя, двухразрядными, па-

раллельными и парафазными регистрами.

|

X0 |

|

|

R |

T |

|

|

|

|

R |

T |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|||||||||

|

|

|||||||||||||

|

|

|

|

|

С |

|

|

|

|

|

С |

|

|

Q0 |

|

|

|

|

|

|

|

Q0 |

|

||||||

X0 |

|

|

|

S |

|

|

S |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

рг1 |

|

|

|

|

|

рг2 |

||

|

X1 |

|

|

|

R |

T |

|

|

|

|

R |

T |

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

С |

|

|

|

|

|

С |

|

|

Q1 |

|

|

|

|

|

|

|

Q1 |

|

||||||

X1 |

|

|

|

S |

|

|

S |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V – запись слова

1

Трехразрядный последовательный сдвигающий регистр построен-

ный на синхронных D – триггерах

D  D T

D T

|

|

|

|

|

С |

|

|

|

Q0 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

R |

|

|

ОС |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

D |

T |

|

||

|

|

|

|

|

|||||

|

|

|

|

|

С |

|

|

|

Q1 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

D |

T |

|

||

|

|

|

|

|

|

|

|

||

V – запись слова |

|

|

|

С |

|

|

|

Q2 |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

||||

|

|

|

R |

|

|

|

|

||

|

|

|

|

|

|

|

|||

|

R |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

5

Двухразрядный реверсивный сдвигающий регистр

E

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|||

|

|

|

|

& |

1 |

|

|

|

|

D |

T |

& |

1 |

|

D |

T |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

X1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

& |

|

|

|

|

|

C |

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

C |

|

|

|

Q1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V

Универсальный последовательный параллельный регистр (5 эле-

ментов 2-И-ИЛИ, 4 синхронных D – триггера)

|

|

|

D |

|

& |

|

b0 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

X0 |

1 |

D |

T1 |

|

|

Q0 |

|||||

|

|

|

|

|

||||||||||

& |

|

|

||||||||||||

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

C |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

1 |

b1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

X1 |

D T2 |

Q1 |

|||||||||

|

|

& |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

& |

|

1 |

b2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

X2 |

|

|

D T3 |

|

|||||||

|

|

|

|

|

|

||||||

&Q2

|

|

|

& |

|

1 |

b3 |

|

|

|

C |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

X3 |

|

|

D T4 |

|

|||||||

|

|

|

|

||||||||

&Q3

C1 |

|

C |

V |

& |

1 си |

C2 |

||

1 |

& |

|

|

|

6

Трехразрядный суммирующий счетчик с последовательным пере-

носом

T0 |

|

|

|

|

Q0 |

|

|

|

|

Q1 |

|

|

|

Q2 |

|

|

Т |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

T |

TT |

|

|

|

T |

TT |

|

|

|

|

T |

TT |

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

R |

1 |

|

|

|

R |

2 |

|

|

|

|

R |

3 |

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

Уст 0-я |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Q0t Q0 t 1 |

|

|

|

|

|

|

T0 |

Q1t |

Q1 t 1 |

|

|

|

|

|

|

|

Q0 |

Q2t Q2 t 1 |

|

|

|

Q1 |

||||||||||||||||||

T0 |

Q0 t 1 |

Q0 |

Q1 t 1 |

Q1 |

Q2 t 1 |

|||||||||||||||||||||||||||||||||||

Трехразрядный вычитающий счетчик с последовательным пере-

носом

|

|

|

|

|

Q0 |

|

|

Q1 |

|

|

|

Q2 |

Т0 |

|

|

|

|

|

|

|

|

|

|

|

t |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

T0 |

|

T |

TT |

|

|

|

T |

TT |

|

|

|

T |

TT |

|

|

|

S |

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

S |

1 |

|

|

|

S |

2 |

|

|

|

S |

3 |

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

t |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t |

|||||||

Уст 1-ы |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

Трехразрядный реверсивный счетчик на двухтактных T – тригге-

рах, и еще два элемента И-ИЛИ.

V |

1 |

TT Q0 |

T TT Q1 |

|

T TT Q2 |

|

|

T |

& |

||||

|

|

& |

|

1 |

|

|

|

|

1 |

|

|

|

|

|

R |

& |

R 2 |

& |

R |

3 |

|

1 |

|

||||

Устначсост |

|

|

|

|

|

|

7

Реверсивный счетчик со сквозным переносом

Кслед

разряду

|

|

|

|

|

|

|

|

Q0 |

|

|

|

1 |

|

|

|

|

|

1 |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

T0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

Q2 |

||||||||||

|

|

|

T |

TT |

|

|

|

|

|

|

|

T |

TT |

|

|

|

|

|

|

T |

TT |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

С |

|

|

|

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

0 |

|

|

|

|

Q1 |

|

|

|

|

Q2 |

|||||||||||||||

|

|

|

|

R |

1 |

|

|

|

|

|

R |

2 |

|

|

|

R |

3 |

||||||||||||||||

Устначсост |

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Четырехразрядный суммирующий счетчик с последовательным

переносом

|

|

Q0 |

|

Q1 |

|

|

Q2 |

|

|

1 |

|

1 |

|

1 |

|

|

TT Q3 |

|

J |

TT |

J |

TT |

J |

TT |

J |

|

T0 |

С |

|

С |

|

С |

|

С |

|

|

K |

1 |

K |

2 |

K |

3 |

K |

3 |

|

1 |

|

1 |

|

1 |

|

|

|

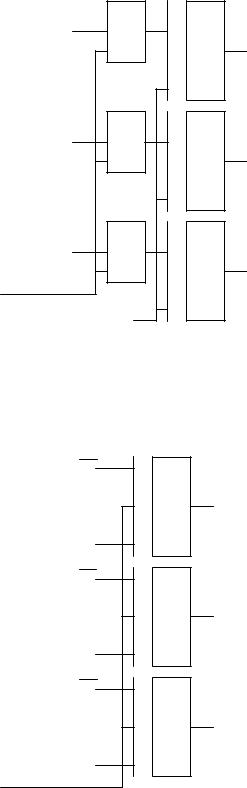

12-ти разрядный счетчик со сквозным переносом

T0 +1 |

Cч0 |

|

1 |

& |

|

|

2 |

|

|

3 |

|

24=16 |

|

|

T1 +1 |

Cч0 |

|

1 |

& |

|

|

2 |

|

|

3 |

|

28=256 |

|

|

T2 +1 |

Cч0 |

|

1 |

& |

|

|

2 |

|

|

3 |

|

212=4086 |

|

|

8

Функциональная схема трехразрядного кольцевого счетчика на

JK – триггерах.

|

X1 |

|

|

|

|

|

|

|

Q0 X2 |

|

|

Q1 X3 |

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

S |

T |

S |

T |

S |

T |

|

|

Q2 |

|

S |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

|||||||||

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

|

|

|

|

J |

|

|

|

|

|

|

|

J |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X2 |

|||

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X3 |

|||

|

|

|

|

|

|

|

K |

1 |

|

|

|

|

|

|

|

|

|

|

K |

2 |

|

|

|

|

|

|

K |

|

3 |

|

|

|

|

X4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

T0 |

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

R |

|

|

|

|

|

C |

|||

Уст0-я |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0

1

2

3

P

ЗУ с непосредственной адресацией

ША |

РгА |

|

|

|

|

|

|

|

0 |

|

n-1 |

|

|||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

ДША |

*** |

|

ЗМ |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

N-1 |

|

||

|

|

|

|

Поиск адреса |

|

|

Поиск ячейки |

||||||||

|

|

|

|

Подготовка |

|

|

|

|

|

|

|

|

|

|

|

|

|

ПР |

УУ |

|

УС…1 |

|

БУЗ |

|

|||||||

|

|

Код операции |

|

|

|

||||||||||

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

УСn |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

УС5 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

УС4

УС4

БСУ РгИ

РгИ

УС3 УС2 УС1

чтение

ШД

запись

Алгоритм работы устройства

Подготовка к работе

УС

Прием с ША в РгА

УС

|

|

ДША→ЗМ |

нет |

чтение |

|

запись |

||

Поиск ячейки информации в ЗМ

да

ШД→РгИ→БУС→ЗМ

ЗМ→БУС→РгИ

ЗМ→БУС→РгИ

РгИ→ШД

Конец

9

Сверх оперативное ЗУ с непосредственной адресацией

Данная ЗУ строится на основе регистра:

|

|

УС5 |

|

|

|

ШД |

|

|

|

|

|

|

|

|

|

|

|

УС7 |

|

ШY |

|

|

|

ШХ |

|

УС2 |

УС6 |

|

|

|

|

УС4 |

|

||

|

|

|

|

|

|

УС3 |

||

|

|

|

|

|

|

|

|

|

|

РгИ |

|

0 |

РгИ0 |

n-1 |

РгА |

ОЗУ |

РгИ |

|

|

|

|

|

|

|

||

АЛУ |

|

|

РгИ1 |

|

|

|

|

|

|

|

|

0 |

n-1 |

|

|

|

|

|

|

|

… |

|

|

|

||

|

|

|

|

|

информации |

|

|

|

|

|

|

0 |

РгИN |

n-1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

0 |

m |

|

|

Запись |

|

|

ДША |

РгА |

|

|

|

|

|||

|

|

|

|

|

||||

|

УС1 |

КО |

А1 |

А2 |

|

|

|

|

|

УС8 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

Ассоциативные ЗУ |

|

|

|||||

Сигнал |

маски |

|

|

ША

0 |

РгАП |

|

n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

α0 |

|

|

|

|

|

|

|

|

|

N |

|

|

|

|

РгМ |

|

n |

|

|

|

КС |

|

РгП0 |

|

ФС |

α1 |

0 |

|

|

|

|

|

|

α2 |

|||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

ЗМ |

N |

|

|

|

|

|

|

|

|

|

|

0 |

|

n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

0 РгИ n

запись ШД чтение

10