Министерство образования и науки Российской Федерации

Саратовский государственный технический университет

Балаковский институт техники, технологии и управления

Кодовые дешифраторы

Методические указания к практическим занятиям

по дисциплине "Информационные сети и телекоммуникации"

для студентов специальности 210100

дневной и вечерней форм обучения

Одобрено

редакционно-издательским советом

Балаковского института техники,

технологии и управления

Балаково 2005

Кодовые дешифраторы

Так же, как и шифраторы, дешифраторы делятся на комбинационные и последовательностные (декодеры). Чтобы построить дешифратор, необходимо знать и уметь формализовать 32 процедуры декодирования выбранного кода. Обычно в основе этих процедур лежат процедуры кодирования. Сопоставляя принятый сигнал с правилами кодирования, можно найти ошибки в сигналах и даже их исправить.

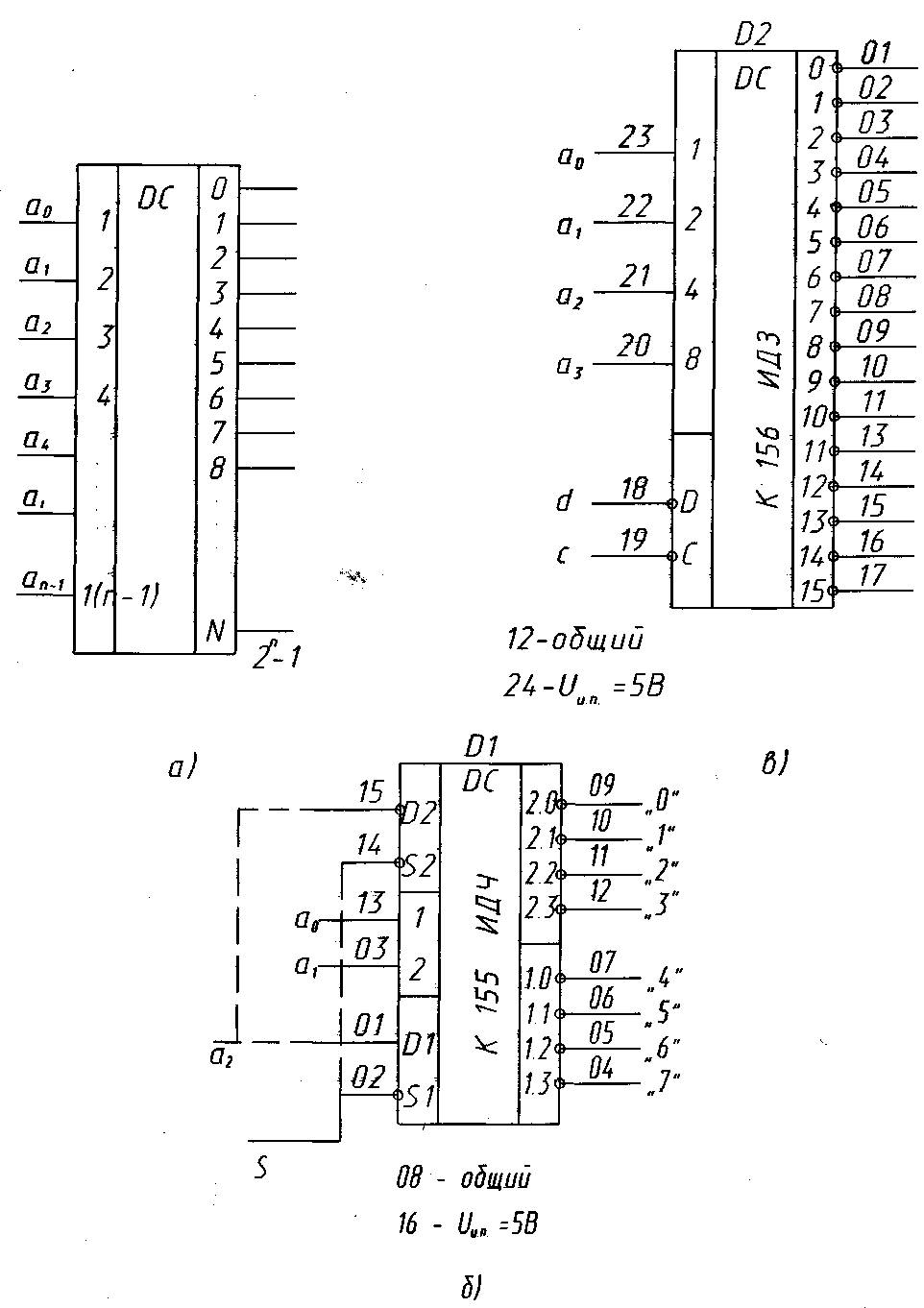

Обнаружение ошибок возможно только тогда, когда минимальное кодовое расстояние больше единицы, т.е. когда код избыточный. В основу построения дешифраторов безызбыточных кодов положено использование многовходовых схем совпадения (логических элементов И или И-НЕ). Дешифратор, имеющий "n" входов и 2n выходов, называется полным n-го порядка. В интегральном исполнении выпускаются полные дешифраторы 2-, 3-, 4-го порядков. Они имеются в составе различных серий микросхем и, в том числе, в серии К155 (рис.1).

Дешифраторы безызбыточных кодов

Эти дешифраторы (ДШ) обычно входят как составные части в более сложные декодирующие устройства, но могут применяться и для других целей [1]. Общее условно графическое обозначение (УГО) таких ДШ на функциональных схемах показано на рис.1, а. Входы ДШ, на которые подается декодируемая комбинация, обозначаются весовыми коэффициентами <1>, <2>, <4>, <8>, <16> и т.д. и называются адресными. Допускается использовать метки ↑0, ↑1, ↑2,.... ↑ (n-l), где стрелка ↑ означает возведение в степень двойки, а цифра есть показатель степени. Выходы ДШ нумеруются десятичными числами, начиная с нуля, и могут быть

прямыми или инверсными (рис. 1,б, в).

Рис. 1. Дешифраторы двоичных безызбыточных кодов:

а-общее УГО; б, в–серии К155

Номер выхода (его «адрес») укажет комбинацию сигналов по адресным входам, при которой сигнал на данном выходе примет активное значение. В любой момент времени на выходах ДШ активное значение может принять только один сигнал, причем на том выходе, номер которого отображается в данный момент времени комбинацией сигналов на адресных входах. Адресный вход с меткой <1> или <↑0> является входом младшего разряда <а0>, а с меткой <↑(n-1)> -самого старшего разряда

(n - число элементов кода).

Реальные ДШ, как правило, кроме адресных имеют управляющие входы, которые используются для подачи сигналов «разрешения декодирования». Так микросхема К155ИДЗ представляет собой полный ДШ 4-го порядка, имеющий 16 инверсных выходов, 4 адресных и 2 инверсных управляющих входа (выводы 18 и 19, рис.1,в). Функция управления этим ДШ имеет вид fu=dS, где d и S - сигналы по управляющим входам D и S. Если fu=0, то на всех выходах ДШ устанавливается сигнал лог.1 (неактивный). При fu=1(d=S=0) сигнал лог.0 (активный) будет только на одном из выходов, номер которого определяется комбинацией

<a3a2ala0>i(i=0,1,...15). Например, при <a3a2a1a0>=<a3a2a1a0>→ →<1001> =<9> на 9-м выходе будет лог.0, а на остальных 15 - лог. 1.

Микросхема К155ИД4 является сдвоенным ДШ 2-го порядка с общими адресными входами (<1> и <2>, выводы 13 и 03 соответственно). Один из ДШ, входящих в микросхему, управляется функцией fu1=d1s1 и имеет выходы 1.0, ... ,1.3 (выводы 07...04). Для другого функция fu2=d2s2 и выходами являются выводы 09,...,12 (2.0;...;2.3). Если d1=d2=a2 и s1=s2=s, то микросхема будет выполнять функции полного ДШ 3-го порядка со стробирующим входом S и тремя адресными входами: a0, a1 и а2.

На рис. 1,б соединения, соответствующие этому варианту, показаны пунктиром, а нумерация выходов - цифрами в кавычках.

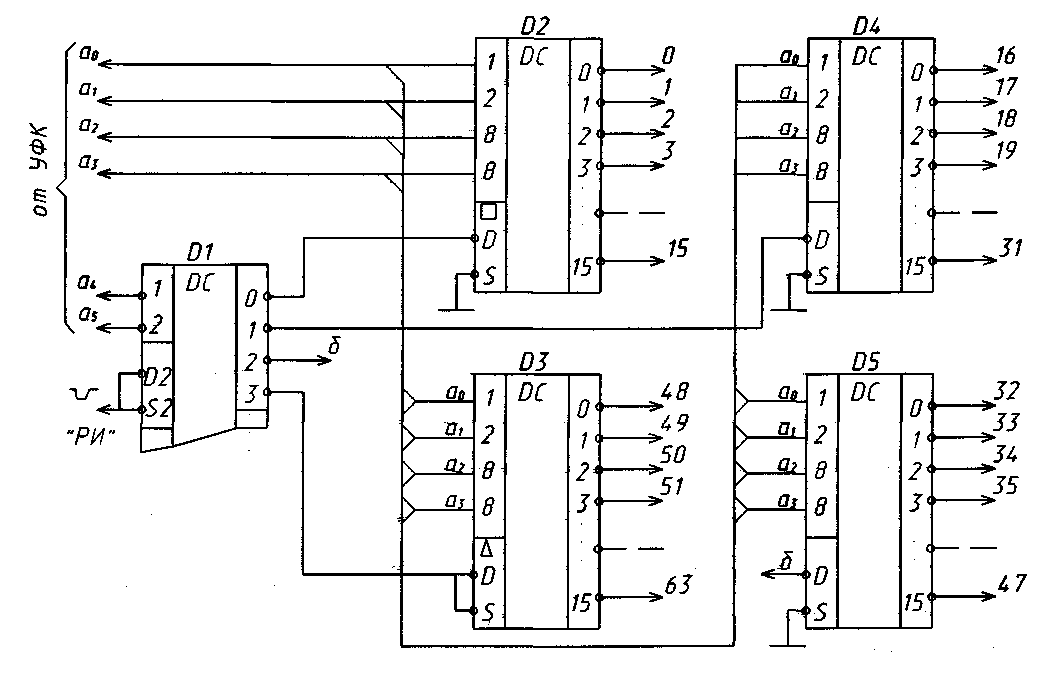

Чтобы построить ДШ на большее число разрядов, следует воспользоваться принципом «ступенчатого декодирования». Он заключается в том, что многоразрядная комбинация расшифровывается по частям: младшие разряды - отдельно от старших разрядов, а ДШ старших разрядов управляют ДШ младших разрядов (рис.2).

Рис. 2. Дешифратор 6–элементного безызбыточного двоичного кода,

(схема принципиальная)

При использовании ИС К 155 достаточно двухступенчатого ДШ, чтобы декодировать 8-элементную комбинацию безызбыточного кода. У такого ДШ будет 256 выходов. На рис.2 первая ступень декодирования комбинаций вида (а5а4а3а2а1а0) реализована на «половине» ДШ К155ИД4 и расшифровывает комбинации старших двух разрядов (а5а4). Вторая ступень образована ДШ 4-го порядка D2,...,D5 (типа ИДЗ), каждый из которых декодирует комбинации младших 4-х разрядов (а3а2а1а0). Поэтому их адресные входы соединены параллельно соответственно. Если сигнал РИ равен лог.1, то накладывается запрет на декодирование комбинаций и на всех выходах (0,1,...,63) будут сигналы неактивного уровня (лог.1). Очевидно, используя микросхему D1 как ДШ 3-го порядка, из схемы рис.2 легко получить ДШ 7-го порядка. Для этого следует добавить ещё 4 микросхемы ИДЗ (всего потребуется 9 микросхем).