- •Лабораторна робота № 1 дослідження основних логічних елементів

- •Основні теоретичні відомості

- •4 Якщо для побудови схеми використати елементи і – не, тоді одержану функцію за законом інверсії можна привести до вигляду

- •Порядок виконання роботи

- •Лабораторна робота № 2 Дослідження тригерів

- •Контрольні запитання

- •Лабораторна робота № 3

- •Мета роботи

- •Порядок виконання роботи

- •Обробка результатів досліджень

- •Лабораторна робота № 4

- •Дослідження основних комбінаційних

- •Логічних пристроїв

- •Мета роботи

- •Порядок виконання роботи

- •Лабораторна робота № 5

- •Дослідження чотирирозрядного

- •Паралельного суматора

- •Мета роботи

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Лабораторна робота № 6

- •Десять станів

- •Порядок виконання роботи

- •Обробка результатів

- •Контрольні запитання

- •Перелік рекомендованих джерел

Контрольні запитання

-

Які логічні пристрої називаються тригерами?

-

Поясніть призначення R, S, D, C, T-входів тригерів.

-

Поясніть роботу асинхронних RS-тригерів.

-

Поясніть роботу синхронних RS-тригерів.

-

Принцип роботи D- та T-тригерів.

-

JК-тригери та їх часові діаграми.

Лабораторна робота № 3

ДОСЛІДЖЕННЯ ПАРАЛЕЛЬНОГО, ПОСЛІДОВНОГО ТА УНІВЕРСАЛЬНОГО РЕГІСТРІВ

Мета роботи

Вивчити будову та принцип дії чотирирозрядних паралельних, послідовних та універсальних регістрів.

ОСНОВНІ ТЕОРЕТИЧНІ ВІДОМОСТІ

Регістри – це функціональні пристрої, призначені для запису, зберігання та видачі інформації у вигляді двійкових кодів. Для зберігання кожного двійкового розряду в регістрі використовується одна тригерна комірка. Отже для зберігання n-розрядного двійкового коду регістр повинен мати n - кількість тригерів.

На рисунку 3.1 зображена схема чотирирозрядного паралельного регістра пам’яті, виготовленого на ІМС типів 155ТМ7 і 155ЛИ1. При подачі керуючого сигналу у1 = 1 інформація на входах х1 – х4 записується у відповідні розряди чотирьох D – тригерів (αі = хі). Якщо у1= у2 = 0 інформація зберігається в регістрі пам’яті, а при у2 = 1 відбувається паралельне зчитування інформації (вихідні сигнали zi = αі y2).

Рисунок 3.1 – Схема чотирирозрядного паралельного регістра пам’яті з потенціальним керуванням

Для побудови регістрів пам’яті, які керуються спадом імпульсу, можна використати синхронні D – тригери, наприклад ІМС типу 155ТМ8. Схема даного чотирирозрядного паралельного регістра зображена на рисунку 3.2.

Рисунок 3.2 – Схема чотирирозрядного паралельного регістра пам’яті з керуванням за спадом імпульсу

Встановлення регістра в нульовий стан здійснюється подачею сигналу у3, який відповідає рівню логічного нуля. Інформація хі, яка надходить до кожного з входів регістра, подається на відповідний вихід Qi в момент переходу тактуючого сигналу у1 із стану логічної одиниці в стан логічного нуля. При цьому сигнал скидання у3 повинен відповідати рівню логічної одиниці (у3 = 1). Якщо у2 = 1 відбувається зчитування інформації яка записана в регістр (zi = Qі). Цей регістр володіє кращою завадозахищеністю в порівнянні з розглянутим вище регістром тому, що запис інформації в ІМС типу К155ТМ8 здійснюється тільки під час спаду імпульсу у1.

На рисунку 3.3 зображений зсуваючий послідовний регістр, який складається з послідовно з’єднаних D – тригерів. По передньому фронту синхронізуючого імпульсу С інформація із входу х записується в перший тригер:

Q1+ = x.

Інформація, яка зберігається впродовж деякого такту у тригері Qі–1, в наступному такті передається в тригер Qі , тобто відбудеться зсув даних від тригера до тригера:

Q1+ = Qi – 1(i = 2,3,…,m).

Такий регістр зсуває коди в одному напрямі. Інформація, яка надійшла на вхід х під час будь-якого такту, з’явиться на виході Qm зсуваючого регістра через m тактів.

Рисунок 3.3 – Схема

зсуваючого послідовного регістра

Рисунок 3.3 – Схема

зсуваючого послідовного регістра

Якщо Qm вважати старшим розрядом, тоді зсув даних відбувається в сторону старших розрядів, тобто вліво. Якщо Qm – молодший розряд, тоді відбувається зсув даних вправо від старших розрядів до молодших.

В розглянутому регістрі запис інформації здійснюється за входом х послідовним кодом (розряд за розрядом). Часто потрібні більш складні регістри: з паралельним синхронним записом інформації, реверсивні, з паралельно – послідовним синхронним записом. Такі регістри називають універсальними.

Рисунок 3.4 – Схема універсального регістра 155ИР1

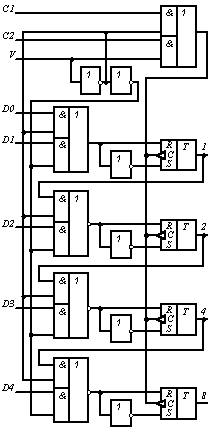

Прикладом універсального регістра є ІМС типу 155ИР1, який зображений на рисунку 3.4, а на рисунку 3.5 його функціональна схема. Це чотирирозрядний зсуваючий регістр з можливістю послідовного і паралельного запису інформації. Регістр реалізований на чотирьох RS – тригерах і має два тактуючі входи С1, С2 і один вхід V, який керує режимом роботи регістра. Інформаційний вхід D0 призначений для занесення даних в послідовному коді, а входи D1 – D4 – для занесення даних в паралельному коді.

Рисунок 3.5 – Функціональна схема регістра 155ИР1

Регістр може працювати в чотирьох різних режимах, при яких виконується: зсув кодів вправо; зсув кодів вліво; паралельне занесення даних; зберігання інформацій. Вибір того чи іншого режиму здійснюється подачею відповідного рівня логічного сигналу на керуючий вхід V.

При V=0 здійснюється зсув ходів вправо і зберігання інформації при зсуві вправо. Якщо V=1, тоді відбувається або паралельне занесення інформації за входами D1 – D4, або зсув кодів вліво.

При роботі регістра в режимі перетворення послідовного коду в паралельний із зсувом вправо (V=0) вимикаються входи D1 – D4 паралельного запису, дозволяються занесення даних в регістр за входом DO в послідовному коді та проходження тактуючих сигналів входом С1, а також встановлюються зв’язки виходу кожного старшого розряду із входом наступного молодшого. Зсув на один розряд вправо здійснюється при кожному спаді тактуючого імпульсу на вході С1. Інформація у вигляді чотирирозрядного паралельного коду з’явиться на виходах 1, 2, 4, 8 через чотири такти вхідного імпульсу. (Нумерація здійснюється від старших розрядів до молодших).

Паралельне занесення даних здійснюється через входи D1 – D4 при наявності керуючого сигналу V=1 з надходженням спаду імпульсу на вхід С2. При цьому вхід послідовного занесення D0 і вхід тактуючих сигналів С1 вимикаються.

Рисунок 3.6 – Реверсний зсуваючий регістр ІМС типу 155ИР1

При організації зсуву кодів вліво необхідно здійснити зовнішні з’єднання, як показано на рисунку 3.6. Послідовний запис в регістр здійснюється входом D4 при керуючому сигналі V=1. Паралельний запис при зсуві кодів вліво неможливий тому, що канали паралельного занесення використовуються для передачі даних від молодших розрядів до старших. Зсув кодів вліво здійснюється при кожному спаді тактуючого імпульсу (С2). У випадку з’єднань, показаних на рисунку 3.6, відсутня можливість тільки паралельного занесення даних. Зсув кодів вправо можливий і здійснюється подачею тактуючих сигналів на вхід С1 при низькому рівні логічного сигналу на керуючому вході V. Отже, зсуваючий регістр, який зображений на рисунку 3.6, є реверсивний.

При зсуві кодів вправо послідовні коди поступають каналом x на вхід D0 (V=0), а при зсуві кодів вліво (V=1) – каналом y на інформаційний вхід D4.