- •Лабораторна робота № 1 дослідження основних логічних елементів

- •Основні теоретичні відомості

- •4 Якщо для побудови схеми використати елементи і – не, тоді одержану функцію за законом інверсії можна привести до вигляду

- •Порядок виконання роботи

- •Лабораторна робота № 2 Дослідження тригерів

- •Контрольні запитання

- •Лабораторна робота № 3

- •Мета роботи

- •Порядок виконання роботи

- •Обробка результатів досліджень

- •Лабораторна робота № 4

- •Дослідження основних комбінаційних

- •Логічних пристроїв

- •Мета роботи

- •Порядок виконання роботи

- •Лабораторна робота № 5

- •Дослідження чотирирозрядного

- •Паралельного суматора

- •Мета роботи

- •Основні теоретичні відомості

- •Порядок виконання роботи

- •Лабораторна робота № 6

- •Десять станів

- •Порядок виконання роботи

- •Обробка результатів

- •Контрольні запитання

- •Перелік рекомендованих джерел

Лабораторна робота № 2 Дослідження тригерів

МЕТА РОБОТИ

Вивчити будову і принцип роботи тригерів RS-, D таT- типів

ОСНОВНІ ТЕОРЕТИЧНІ ВІДОМОСТІ

Найпростішими логічними пристроями з пам’яттю є тригери, які можуть знаходитися в одному з двох стійких станів і переходити з одного стану в другий внаслідок дії зовнішніх сигналів. Перехід в кожний наступний стан залежить не тільки від поточних значень вхідних сигналів, але й від попереднього стану тригера. Інформація про попередній стан тригера, яка надходить з виходів тригера разом із зовнішніми сигналами керує його роботою. Тому тригери є пристроями із зворотними логічними зв’язками.

Логічна функція, яка встановлює залежність стану, в який переходить тригер з поточного стану при дії заданих сигналів керування, називається функцією переходів тригера. Функції переходів задаються логічними формулами або у вигляді таблиць.

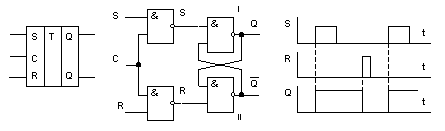

Асинхронний

RS-тригер

з прямими входами S

(set-встановити)

і R

(reset-знову

встановити, тобто скинути) і двома

виходами -

![]() та

та

![]() може

бути реалізований на логічних елементах

АБО-НЕ (рисунок 2.1) та І-НЕ (рисунок 2.2).

може

бути реалізований на логічних елементах

АБО-НЕ (рисунок 2.1) та І-НЕ (рисунок 2.2).

Літерами,

![]() ,

,![]() позначають

вихідні логічні сигнали тригера до

поступлення вхідних сигналів, а літерами

позначають

вихідні логічні сигнали тригера до

поступлення вхідних сигналів, а літерами

![]() та

та

![]() - вихідні сигнали тригера після дії

вхідних сигналів. Тригер називають

асинхронним тому, що перехід в новий

стан відбувається відразу після

надходження вхідного сигналу .

- вихідні сигнали тригера після дії

вхідних сигналів. Тригер називають

асинхронним тому, що перехід в новий

стан відбувається відразу після

надходження вхідного сигналу .

а) б) в)

Рисунок 2.1-Позначення асинхронного RS-тригера (а), реалізація на логічних елементах АБО-НЕ (б) та часові діаграми вхідних та вихідних сигналів тригера(в)

При відсутності вхідних сигналів (R=0, S=0) тригер зберігає інформацію на виході (Q=0 або Q=1). Після надходження сигналу на вхід установлення (S=1) тригер встановлюється в стан “1”(Q=1). Подача сигналу на вхід скидання (R=1) призводить до скидання тригера в стан “0”(Q=0). Одночасна подача сигналів на два входи (S=1, R=1) заборонена, тому що при цьому неможливо передбачити стан тригера.

На рисунку 2.2 приведене позначення асинхронного RS-тригера, його реалізація на логічних елементах І-НЕ та часові діаграми вхідних і вихідних сигналів тригера. У схемах асинхронних тригерів мають місце зворотні зв’язки з виходів тригера на входи логічних елементів, що дозволяє враховувати його попередній стан. Таблиця 2.1 - це таблиця істинності RS- тригера для ряду вхідних сигналів.

а) б) в)

Рисунок 2.2-Позначення асинхронного RS-тригера (а), його реалізація на логічних елементах І-НЕ (б) та часові діаграми вхідних та вихідних сигналів тригера (в)

Таблиця 2.1

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

заборонена комбінація |

|

В першому рядку

таблиці 2.1 показано, що відсутність

вхідних сигналів S=R=0

призводить до появи на виходах

![]() i

i

![]() логічних одиниць.

логічних одиниць.

Попередній стан

сигналу

![]() дає на виходах елемента ІІ (рисунок 2.2,

б) логічні одиниці, якщо на вході S

був сигнал 0. Отже, на виході отримують

інверсний сигнал

дає на виходах елемента ІІ (рисунок 2.2,

б) логічні одиниці, якщо на вході S

був сигнал 0. Отже, на виході отримують

інверсний сигнал![]() .

Попередній стан сигналу

.

Попередній стан сигналу

![]() дає на одному з входів елемента І сигнал

0, в зв’язку з чим на виході цього елемента

І-НЕ отримують

дає на одному з входів елемента І сигнал

0, в зв’язку з чим на виході цього елемента

І-НЕ отримують![]() .

Отже, відсутність сигналів на входах S

і R

не викликає зміни вихідних сигналів.

Поява сигналу R=1,

S=0

призводить до зміни станів вихідних

сигналів (

.

Отже, відсутність сигналів на входах S

і R

не викликає зміни вихідних сигналів.

Поява сигналу R=1,

S=0

призводить до зміни станів вихідних

сигналів (![]() ,

,

![]() ).

Подача сигналів S=1,

R=0

призводить до нової зміни станів вихідних

сигналів (

).

Подача сигналів S=1,

R=0

призводить до нової зміни станів вихідних

сигналів (![]() ,

,![]() ).

Одночасна подача сигналів S=1,R=1

викликає

).

Одночасна подача сигналів S=1,R=1

викликає![]() ,

,![]() і призводить до появи Q=1,

і призводить до появи Q=1,![]() .

Такий сигнал не використовується. В

скороченому вигляді таблицю істинності

можна зобразити наступним чином:

.

Такий сигнал не використовується. В

скороченому вигляді таблицю істинності

можна зобразити наступним чином:

Таблиця 2.2

|

|

|

|

|

0 |

0 |

Qn |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

Заборонена комбінація |

Якщо в пристрої є декілька асинхронних RS-тригерів, тоді часто виникає необхідність синхронізації перемикань тригерів у часі, оскільки неодночасне їх перемикання може призвести до виникнення непередбачених станів. В таких випадках використовуються синхронні тригери.

Синхронні тригери мають додатковий тактовий вхід і сприймають інформацію на входах лише за наявністю тактового імпульсу. На рисунку 2.3 зображені позначення синхронного тригера та його схема, яка реалізована на логічних елементах І-НЕ. Із схеми видно, що за відсутністю тактового сигналу на вході

а) б)

Рисунок 2.3 - Позначення синхронного тригера (а) та його реалізація на логічних елементах І-НЕ (б)

С

(С=0)

на виходах

![]() і

і![]() логічні одиниці,

логічні одиниці,

![]() ,

,![]() .

Як було показано вище, елементи І і ІІ

(рисунок 2.3, б), маючи такі вхідні сигнали,

не змінюють сигналів на виходах Q,

.

Як було показано вище, елементи І і ІІ

(рисунок 2.3, б), маючи такі вхідні сигнали,

не змінюють сигналів на виходах Q,![]() .

.

Найбільш універсальним серед синхронних тригерів є JК-тригер. Схемна реалізація його досить складна, але для використання тригера достатньо знати призначення його виводів та алгоритм роботи. На рисунку 2.4 зображені схемне позначення JК-тригера та часова діаграма, яка пояснює його роботу.

а) б)

Рисунок 2.4-Схемне позначення JК-тригера (а) та його часова діаграма (б)

При наявності

нульових сигналів на входах J,

С, К тригер

зберігає свій стан. Сигнал J=1

вмикає тригер: після закінчення тактового

імпульсу С=1

тригер приймає стан “ввімкнено” і

![]() .Сигнал

на вході К вимикає тригер по зрізу

тактового імпульсу С. За наявністю

сигналів J=К=0

надходження тактових імпульсів не

викликає змін у стані тригера. Якщо ж

вхідні сигнали J=К=1,

надходження тактового імпульсу перекидає

тригер до протилежного стану:

.Сигнал

на вході К вимикає тригер по зрізу

тактового імпульсу С. За наявністю

сигналів J=К=0

надходження тактових імпульсів не

викликає змін у стані тригера. Якщо ж

вхідні сигнали J=К=1,

надходження тактового імпульсу перекидає

тригер до протилежного стану:

![]() (для

RS-тригерів

така вхідна комбінація сигналів

заборонена).

(для

RS-тригерів

така вхідна комбінація сигналів

заборонена).

Промисловістю

випускаються готові JК-тригери

у вигляді інтегральних мікросхем (ІМС),

які мають додаткові установчі входи R

і S.

Ці входи асинхронні. Після подачі R=0,

S=1

тригер миттєво встановлює на виході

Qn+1=1,

а після подачі сигналів R=1,

S=0

встановлює

![]() .

Таблиця істинності JК-тригера

має вигляд (таблиця 2.3):

.

Таблиця істинності JК-тригера

має вигляд (таблиця 2.3):

Таблиця 2.3

|

J |

К |

Qn+1 |

|

0 |

0 |

Qn |

|

1 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

|

На базі JК-тригера можна побудувати ряд інших тригерів, наприклад:

1 Синхронний RS-тригер. Якщо прийняти, що J=S, К=R, а комбінацію J=1, К=1 вважати забороненою, тоді таблиця істинності JК-тригера буде еквівалентною до таблиці істинності RS-тригера з тією різницею, що зміна вихідних сигналів для JК-тригера відбу-вається лише в момент зрізування тактового імпульсу на вході С.

2 Лічильний Т-тригер (“tumble”-перекидатися). В цьому тригері входи J та К під’єднуються до потенціалу, що відповідає логічній одиниці: J=1, К=1, а вхід синхронізуючого тактового імпульсу позначають Т. В момент зрізу чергового тактового імпульсу тригер перекидається в попередній стан Qn+1=Qn. Позначення Т-тригера та часові діаграми його роботи приведені на рисунку 2.5.

а) б)

Рисунок 2.5-Схемне позначення (а) та часові діаграми роботи

Т-тригера (б)

З діаграм видно, що частота повторення сигналу на виході Q вдвічі менша від частоти повторення тактових імпульсів Т, тобто він ділить вхідну частоту на два. Тому Т-тригери використовують в лічильниках, подільниках частоти, різного роду перемикачах.

3 D-тригер.

В D-тригері

J=![]() =D.

Він має тільки тактовий вхід С та вхід

D.

D-тригер

може бути виконаний на базі JК-тригера

вмиканням на входах J,

К елемента

НЕ, який забезпечує виконання умови

J=

=D.

Він має тільки тактовий вхід С та вхід

D.

D-тригер

може бути виконаний на базі JК-тригера

вмиканням на входах J,

К елемента

НЕ, який забезпечує виконання умови

J=![]() =D.

В такому тригері використовують лише

другий та третій рядки таблиці істинності

JК-тригера.

З таблиці видно, що в D-тригері

Qn+1=D,

тобто тригер запам’ятовує сигнал на

вході D

в момент тактового імпульсу і тримає

його до наступного тактового імпульсу

(“delay”-затримка).

Тому цей тригер може використовуватися

як елемент пам’яті.

=D.

В такому тригері використовують лише

другий та третій рядки таблиці істинності

JК-тригера.

З таблиці видно, що в D-тригері

Qn+1=D,

тобто тригер запам’ятовує сигнал на

вході D

в момент тактового імпульсу і тримає

його до наступного тактового імпульсу

(“delay”-затримка).

Тому цей тригер може використовуватися

як елемент пам’яті.

Промисловістю випускаються спеціальні ІМС - D-тригери (по два-чотири тригери). Мікросхеми D-тригерів мають особливість, що перемикання D-тригера відбувається на фронті тактового імпульсу. Схемне позначення та часові діаграми роботи D-тригера приведені на рисунку 2.6.

а)

б)

а)

б)

Рисунок 2.6-Схемне позначення (а) на часові діаграми D-тригера (б)

Використовуються також тригери із синхронізуючим входом, але без інформаційних входів. Вони працюють аналогічно, як і Т-тригери, в яких сигнал на вході Т сталий і дорівнює одиниці. Такий тригер при подачі кожного тактового імпульсу змінює свій стан на протилежний. Він і є основним елементом подільників частоти, хоча окремо і не випускається. Однак цей тригер легко реалізувати на основі D-тригера, як показано на рисунку 2.7.

Рисунок 2.7-Схемне позначення тактуючого Т-тригера на основі

D-тригера

ПОРЯДОК ВИКОНАННЯ РОБОТИ

Робота виконується на платі П2 з використанням техноло-гічних карт ІІ-1, ..., ІІ-7.

1 Дослідити роботу RS-тригера (плата П2, технологічні карти ІІ-1, ІІ-2, ІІ-3). Скласти таблицю зміни станів в залежності від вхідних сигналів, враховуючи всі можливі комбінації вхідних сигналів.

2 Дослідити роботу D-тригера (плата П2, технологічні карти ІІ-4,

ІІ-5) враховуючи всі можливі комбінації вхідних сигналів.

3 Дослідити роботу Т-тригера (плата П2, технологічні карти ІІ-6, ІІ-7) враховуючи всі можливі комбінації вхідних сигналів.

ОБРОБКА РЕЗУЛЬТАТІВ ДОСЛІДЖЕННЯ

-

За таблицею зміни станів RS-тригерів пояснити принцип їх роботи. Побудувати часові діаграми вхідних та вихідних напруг.

-

Побудувати часові діаграми роботи D-тригера.

-

Побудувати часові діаграми роботи Т-тригера.

Зробити висновки про виконану роботу.