лекции / Лекции по схемотехнике / Лекция_09

.docЛЕКЦИЯ №9

Типовые функциональные узлы.

План:

-

Особенности проектирования функциональных узлов.

-

Состояния сигналов в цифровых схемах.

Ключевые слова:

Функциональные узлы, операционные автоматы, автоматы с памятью, последовательностные схемы, задержки в элементах, средства реализации комбинационных цепей, средства реализации автоматов с памятью, основные этапы проектирования автоматов, риски статические и динамические, сопки в цифровых схемах.

Особенности проектирования функциональных узлов и влияние времени задержек на работу устройств.

Функциональные узлы (структурные элементы, элементарные структуры, операционные автоматы) сложнее, чем логические элементы, поэтому их реализовывают не на уровне электронных схем, что зачастую неприемлемо, а в виде логических структур, составленных из идеализированных логических элементов.

При рассмотрении функциональных узлов встречаются не только действия над буквенными переменными, но и над многоразрядными словами, т.е. упорядоченными совокупностями переменных, в которых между значениями в отдельных разделах существует связь. Машинное слово обозначается:

![]() ,

где i

- вес разряда.

,

где i

- вес разряда.

При проектировании цифровых устройств необходимо учитывать не только реализуемые логические операции, но и задержки сигналов в логических элементах.

В простейшей и наиболее распространенной модели логического элемента характеристикой времени распространения символов служит «чистая» задержка t3. Задержка сигнала в цепи из последовательно соединенных элементов при этом определяется суммированием задержек в логических элементах и элементах связи.

Задержки в элементах являются случайными величинами, их учет осуществляется различными методами.

Способ задания задержек элементов может быть различным. Наиболее часто изготовитель элементов указывает только предельные максимальные значения задержек*. При известных предельных значениях задержек часто производят расчеты по методу наихудшего случая, основанному на предположении, что задержки элементов принимаются максимально затрудняющими выполнение необходимого условия.

Разделение цифровых устройств на комбинационные схемы (КС) и автоматы с памятью (АП) обусловлено фундаментальными различиями в их свойствах.

Выходная переменная комбинационных цепей зависит только от действующих на ее входах текущих значений входных переменных.

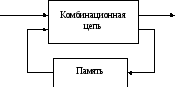

Автомат с памятью вырабатывает выходную величину, зависящую не только от действующих на его входах текущих значений переменных, но и от того состояния, которое имел автомат к моменту поступления данного набора входных переменных. Состояние АП фиксируется с помощью элементов памяти, входящих в состав автомата. Состояние схемы в данный момент оказывается в АП функцией предыдущих состояний. АП называют также последовательными схемами. Они содержат две части: непосредственно память и комбинационную цепь для управления элементами памяти и выработки выходных переменных.

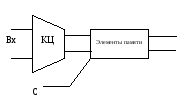

Обобщенная структура автомата с памятью:

К функциональным узлам комбинационного типа относятся преобразователи кодов, дешифраторы, схемы свертки по модулю, сумматоры и т.д.

К АП относятся: триггерные устройства, регистры, счетчики, сумматор, распределители тактов и т.д.

Средства описания и преобразования комбинационных цепей и АП.

Функционирование КЦ и АП описывается различными способами: таблицами, матрицами, графиками, временными диаграммами и др.

Если размерность анализируемого устройства невелика, то эти способы надежны и удобны. Для устройств большой размерности описание становится громоздким и проектировщику сложно с ними работать. Для таких устройств применяется машинные методы проектирования.

При проектировании типовых функциональных устройств часто встречаются задачи малой размерности, для которых удобно применение ручных методов.

Для каждого уровня интеграции ИМС типовые средства реализации основных частей автомата с памятью изменяются

|

Уровень интеграции ИМС |

Средства реализации комбинационных цепей |

Средства реализации АП |

|

Малый |

Логические элементы |

Триггеры |

|

Средний |

Мультиплексоры, дешифраторы, сумматоры |

Регистры, счетчики |

|

Большой |

Постоянные ЗУ, ПЛМ |

ОЗУ, регистры с большой разрядностью |

При проектировании функциональных узлов могут применяться как эвристические, так и формализованные методы.

На пути от исходного описания функционирования КЦ до готовой документации для ее изготовления, представляющем процесс проектирования, можно выделить несколько основных этапов:

-

Выяснение особенностей функционирования КЦ, связей ее с внешними устройствами по входам и выходам, установление соглашений положительной или отрицательной логики по переменным.

-

Оценка размерности задачи и решение вопроса о разделении КЦ на части, если это необходимо.

-

Составление таблиц или карт функционирования КЦ.

-

Минимизация.

-

Выбор функционального состава логических элементов и переход к соответствующему логическому базису в полученном в п.4. выражении.

-

Оформление документации.

Разбиение КЦ на втором этапе может понадобится для упрощения задачи, если ее размерность слишком велика. Схема при этом упрощается, но не достигается максимальное быстродействие.

Таблицы функционирования или карты, составляемые на третьем этапе – исходный материал для минимизации КЦ.

Минимизацию следует понимать в более широком смысле, когда речь идет о таком преобразовании подлежащих реализации функций, которое упрощает их в смысле заданного критерия:

-

Когда логические элементы были дороги, традиционным критерием было количество букв в реализуемых переключательных функциях. Для минимизации по этому критерию были разработаны несколько методов, в т.ч. аналитические и графические. Удобны для использования карты Карно (если размерность не больше 6).

-

По мере роста уровня интеграции микросхем, критерием сложности устройств стало количество корпусов ИМС, затрачиваемое на их реализацию. При этом минимизация в традиционном смысле перестала точно соответствовать новому критерию, но между обоими критериями сохранилась достаточно сильная связь.

-

Для микросхем высокого уровня интеграции (БИС и СБИС) большое значение приобретают морфологические свойства реализуемых схем, их топология. Важным становятся регулярность структуры, повторяемость ее элементов и связей, минимальность длин межсоединений. При этом снижается полезность минимизации переключательных функций в традиционном смысле, может противоречить морфологическим критериям. Методы проектирования схем с точки зрения морфологических критериев только начинает развиваться.

ПЗУ – в СДНФ

Следующий этап проектирования – выбор функционального состава логических элементов и переход к соответствующему логическому базису.

Этот этап нужен потому, что Fmin обычно выражается в ДНФ, т.е. в базисе И, ИЛИ, НЕ. В практических же сериях ИМС чаще представлены базисы И-НЕ, ИЛИ-НЕ. Переход обычно осуществляется применением теоремы де’Моргана.

Состязания сигналов в цифровых схемах.

Понятие риска.

Влияние задержек в элементах на работу цифровых устройств может существенно изменить их функционирование. Для КЦ задержки не только ограничивают быстродействие, но могут также создавать на выходе временно существующие логические шкалы. Эти ложные сигналы называют рисками.

Различают статические и динамические риски.

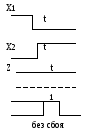

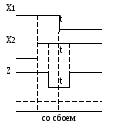

Статические риски существуют, когда состояние выхода должно остаться неизменным, но кратковременно изменяется.

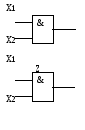

Цепь

реализует операцию

![]() ,

причем предусмотрено одновременное

изменение аргументов. Из-за разных

задержек X1

и X2

в цепях схемы возникают ситуации без

сбоя или со сбоем.

,

причем предусмотрено одновременное

изменение аргументов. Из-за разных

задержек X1

и X2

в цепях схемы возникают ситуации без

сбоя или со сбоем.

Статический риск без сбоя может привести к изменению состояния элемента памяти.

В последнем случае появляется статический риск сбоя – на выходе временно появляется нулевой сигнал, не предусмотренный работой схемы.

Динамический риск возникает, когда логика работы схемы предусматривает на выходе схемы изменение состояния, однако вместо однократного перехода выходной величины с одного уровня на другой происходят многократные переходы.

При динамическом риске первый и последний переходы всегда совпадают с алгоритмическим переходом, предусмотренным логикой функционирования схемы. Статический риск такого свойства не имеет и считается более неблагоприятным.

Для устранения возможных сбоев используется синхронизация процессов приема информации элементами памяти, подключенными к выходам КЦ.

Сигнал С подается на элементы памяти после завершения переходных процессов в КЦ. Следовательно, ложные сигналы не будут воздействовать на элементы памяти.

В АП из-за задержек сигналов наблюдается их временные состязания, что может иметь возможные последствия. Состязания могут быть критическими, т.е. приводить к нарушению нормальной работы автоматов. При проектировании критические состязания должны быть устранены.

Важнейший прием борьбы с критическими состязаниями – синхронизация.

Вопросы для контроля:

-

Как влияют задержки в элементах на работу схемы?

-

В чем разница между комбинационными и последовательностными схемами?

-

Чем отличаются статические риск от динамических?

-

Как влияют статические риски на работу комбинационных и последовательностных схем?

Литература:

-

Угрюмов Е.П. Проектирование элементов и узлов ЭВМ – М.; Высш.шк., 1987, с.96-104.

* Если известны только максимальные значения задержек, то относительно любой цепочки распространения сигнала можно сказать лишь одно – сигнал в ней задержится не более, чем на сумму максимальных задержек.