лекции / Лекции по схемотехнике / Лекция_11

.docЛЕКЦИЯ №11

Преобразователи кодов.

План:

-

Преобразователи прямого кода в обратный.

-

Преобразователи прямого кода в дополнительный.

-

Построение произвольного преобразователя кода.

Ключевые слова:

Преобразователи кодов, преобразователи прямого кода в обратный, преобразователи прямого кода в дополнительный, произвольный преобразователь кода, пара «декодер-кодер».

Преобразователи кодов изменяют вид кодирования данных. двоичные числа могут быть представлены в прямом, обратном или дополнительном коде.

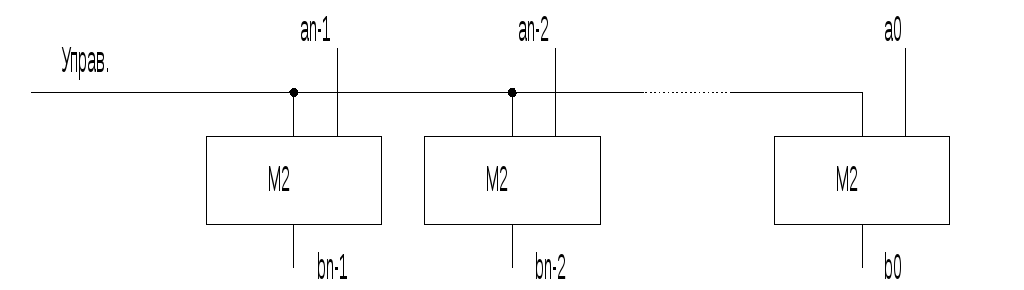

Преобразование прямого кода в обратный реализуется сложением по mod2 значений кода данного разряда и сигнала управления преобразователем.

Выходы.

При этом нулевое значение сигнала управления обеспечивает прохождение на выход схемы прямого кода числа. При единичном сигнале управления каждый разряд выходного кода будет инверсией соответствующего разряда входного кода. Если преобразуется число, содержащие знаковый разряд, то его значение может быть непосредственно использовано как сигнал управления.

Преобразование прямого кода в дополнительный.

В этом случае операция преобразования не является поразрядной, и для определения значения кода в каком-либо разряде требуется анализ значений других разрядов. Для получения дополнительного кода нужно проинвертировать все разряды преобразуемого кода и затем добавить к результату единицу.

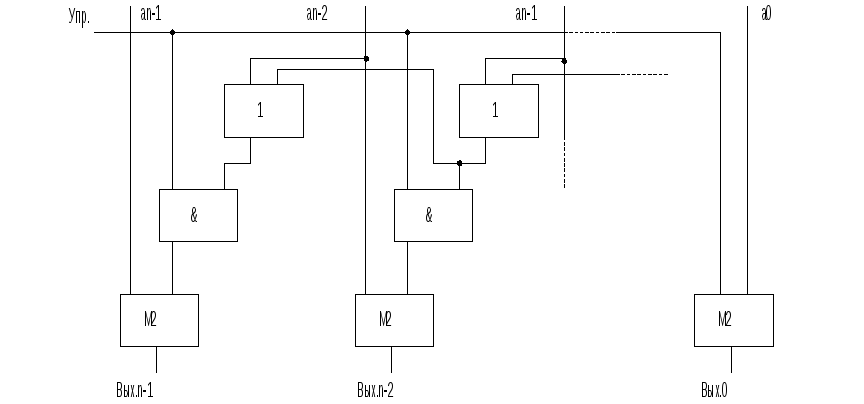

Схема преобразования прямого кода в дополнительный.

Сопоставление прямого и дополнительного кодов показывает что последний отличается от первого инвертированием старших разрядов от n-1 до i+1 включительно, где i – номер первой справа разряда, содержащего единицу. Остальные разряды остаются неизмененными. Например, для прямого кода 10100100 дополнительным будет код 01011100. Аналитически это правило записывается в виде:

![]()

Согласно ююю для получения i-го разряда дополнительного кода нужно сложить по mod2 исходный код этого разряда с дизьюнкцией всех предыдущих (младших) разрядов. Знаковый разряд преобразуемого кода может использоваться как управляющий сигналов.

С ростом объемов постоянного ЗУ стало рациональным выполнять преобразователь кодов на основе памяти (табличным методом).

Если закон работы преобразователя не описывается каким-либо достаточно понятным правилом, то единственно практически приемлемой формой задания преобразователя становиться таблица, которая способна задавать абсолютно любое значение.

Пусть задан следующие значения преобразователя:

Таблица 1.

|

A |

B |

|

a2 |

a1 |

|

z |

jk |

|

0 |

0 |

|

1 |

1 |

|

0 |

1 |

|

0 |

1 |

|

1 |

0 |

|

0 |

0 |

|

0 |

0 |

|

1 |

0 |

|

0 |

1 |

|

1 |

0 |

Таблица 2.

|

A |

B |

|

0 |

1 |

|

2 |

3 |

|

4 |

1 |

|

3 |

0 |

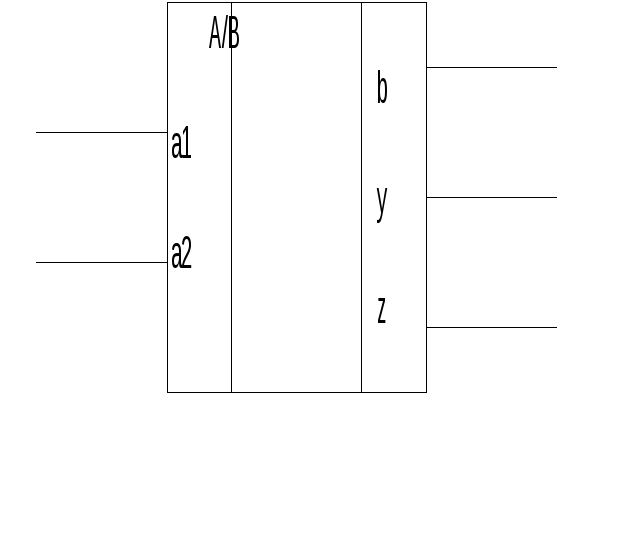

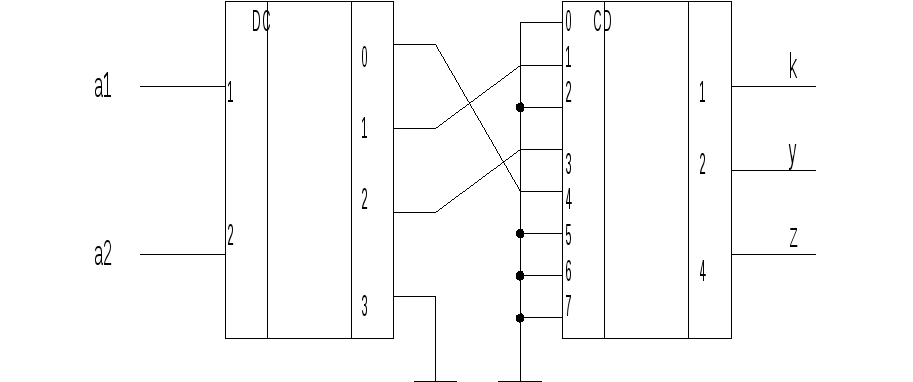

Условное обозначение такого преобразователя кода A в код B.

К построению кодового преобразователя можно подойти с 2-х позиций.

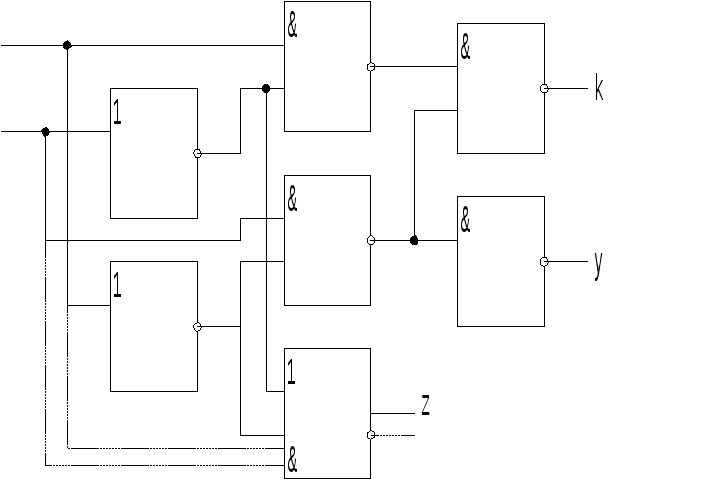

При первом подходе преобразователь реализуется как система булевых функций группы аргументов.

![]()

Независимая

схемная реализация этих выражений не

оптимальна, т.к. элементы, реализующие

выражение

![]() оказываются дублированными.

оказываются дублированными.

Более экономично получается реализация, если выявить общие логические фрагменты, входящие в формулу несколько раз, и реализовать их только один раз.

Однако каких-либо алгоритмов эффективного целенаправленного выявления общих частей, к сожалению не существует.

При втором подходе к построению кодового преобразователя он представляется как пара декодер-кодер. Схема этого же преобразователя, построенного по этому способу выглядит следующим образом.

Число входов Дш равно числу входов преобразователя, число выходов ююю – числу выходов преобразователя. Соединяя выходы Дш и входы Ш. производятся в соответствии с таблицей 2. Часть выходов декодера и входов кодера может не использоваться. Если нескольким входным комбинациям соответствует одна и та же выходная комбинация, то ююю выходы ДС объединяются элементом ИЛИ и выход последнего подается на нужный вход кодера.

При синтезе схемы на матричной БИС преобразователь, построенный по принципу реализации булевых функций в среднем более экономичен по оборудованию, но менее быстродействующий, чем в варианте декодер-кодер, а при проектировании из готовых микросхем более выгодным и по числу корпусов и по быстродействию оказывается структура декодер-кодер. Однако потребляемая мощность в этом случае больше чем у схемы из отдельных логических элементов.

Затраты времени ююю по логическому проектировании по схеме ДС-СД неизмеримо меньше, чем затраты на проектирование преобразователь из отдельных логических элементов.

Вопросы для контроля:

-

Для чего служат преобразователи кодов?

-

Какие методы построения произвольных преобразователей кодов Вы знаете?

-

В чем заключается метод построения на основе логических элементов?

-

В чем заключается метод построения на основе пары «декодер-кодер»?

Литература:

-

Угрюмов Е.П. Проектирование элементов и узлов ЭВМ – М.; Высш.шк., 1987, с169-173.

-

«Функциональные узлы цифровой автоматики» Потёмкин И.С. – М.; Энергоатомиздат, 1988г., с107-109,