лекции / Лекции по схемотехнике / Лекция_10

.docЛЕКЦИЯ №10

Дешифраторы. Шифраторы.

План:

-

Дешифраторы.

-

Каскадные дешифраторы.

-

Матричные дешифраторы.

-

Шифраторы.

Ключевые слова:

Кодирующее устройство, дешифратор, декодер, неполный дешифратор, линейный дешифратор, каскадный дешифратор, пирамидальный дешифратор, прямоугольный (матричный)дешифратор, шифратор (кодер).

Кодирующим устройством называют логический узел преобразующий много разрядный входной код в выходной код, построенный по иному закону. Название достаточно условное, т.к. любое цифровое устройство является кодовым преобразователем. Традиционно это название применяется к узлом, работа которых не описывается достаточно простым алгоритмом, а задается таблицей соответствия входов и выходов.

Дешифратором (Дш) или декодером называют кодирующие устройство преобразующие двоичный код в унитарный. Из всех m выходов Дш активный уровень имеется только на одном, а именно на том, номер которого равен поданному на вход двойному числу. Условное обозначение Дш показано на рис.

Если декодер имеет n входов, m выходов и использует все возможные наборы входных переменных, то m=2n.

Такой дешифратор называют полным в отличие от неполного, использующего лишь часть возможных наборов.

Декодер используют, когда нужно общаться к различным цифровым устройствам, и при этом номер устройства, его адрес, представлен двоичным кодом. Входы декодера (адресные входы) часто нумеруют не порядковыми номерами, а в соответствии с весами двоичных разрядов, т.е. не 1,2,3…, а 1,2,4,8,16 и т.д. Число входов и выходов DC указывают следующим образом 3-8 (три в восемь), 4-16, 4-10 (неполный DC).

Формально работу ДС можно описать задав функции, отрабатываемые каждым из его выходов.

ДС3-8

Реализация этих выражений с помощью 8-ми 3-х входовых элементов и дает наиболее простой по структуре Дш, называемый линейным.

Основной объем его оборудования составляет в общем случае m входных элементов. Кроме того, к оборудованию Дш обычно относят n инверторов входных переменных и m входных буферных усилителей, обычно инвертирующих, что характерно для интегральной технологии. Назначение буферных усилителей – свести к единице кратность нагрузки, которую передает Дш для источника сигнала. иначе каждый источник сигнала будет нагружен на m/2 входов элементов И.

Если

Дш построен на элементах И-НЕ, то на него

входах отрабатываются

![]() т.е.

активным будет низкий уровень.

т.е.

активным будет низкий уровень.

Избавиться от инверсии можно подключив на входы инверторы, либо построив схему Дш на элементах ИЛИ-НЕ. Число входных инверторов и усилителей не изменяется при этом.

Дешифратор часто имеют разрешающий (стробирующий, управляющий) вход E. При E=1 дешифратор работает как обычно, при E=0 на всех входах устанавливаются неактивные уровни независимо от входных сигналов. Вход E часть выполняют инверсным.

Дш, имеющий разрешающий вход E, иногда называют декодером – демультиплексором и обозначают не ДС, а ДХ.

Управление дешифрующими элементами разрешающим входом Дш.

Другая схема:

Этот способ экономичен по оборудованию, но увеличивает задержку Дш.

Каскадные соединения Дш.

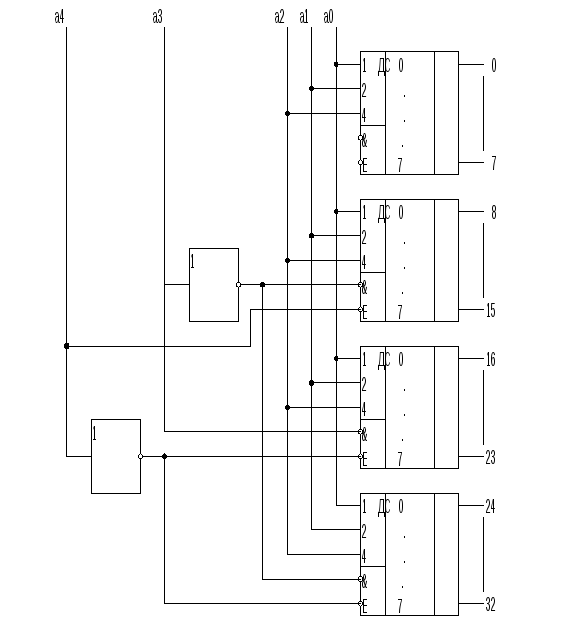

Два старших разряда a4a3 расшифровываются ДС4 2-4, который по входам E управляет 4 Дш 3-8 второго каскада.

Младшие разряды a2a1a0 поступают на входы всех Дш второго каскада, но срабатывает только один из них.

В данном случае 5 разрядный адрес был разбит на 2-раз и 3-х разрядные, что определило структуру схемы. В общем случае много разрядный адрес можно разбить на группы различными способами, и каждому будет соответствовать свой вариант схемы, который отличен аппаратной реализацией, временной задержкой и т.п.

В предельном случае при числе каскадов, равном числу разрядов адреса, получается пирамидальный Дш, который обладает max задержкой. Достоинством является только на 2-х входовых элементах И, что определило его широкое распространение на заре развития цифровой техники. В настоящее время эта схема не выдерживает конкуренции с другими схемами Дш.

Матричные (прямоугольные) дешифраторы

Существуют также прямоугольные дешифраторы. В них разряды адреса разбиты на 2 группы, каждая из которых независимо от другой расшифровывается своим Дш первого каскада ДС1 и ДС2.

В схеме такого дешифратора при любой комбинации оказываются выбранными одна строка и один столбец сетки, в узлах которой расположены элементы «И» второй ступени. Всегда возбуждается только один элемент «И». Сетку из элементов «И» называют матричным или прямоугольным дешифратором.

При использовании во второй ступени элементов И-НЕ выходы Дш будут инверсными. Их можно сделать прямыми, построив сетку второго каскада на элементах ИЛИ-НЕ. Тогда инверсными должны быть входы Дщ первого каскада.

Делить разряды адреса между ДС1 и ДС2 нужно по возможности поровну: чем ближе прямоугольник 2-го каскада к квадрату, тем при этом же числе выходных элементов И меньше сумма строк и столбцов, т.е. меньше число выходов Дш 1-го каскада. В качестве входа E всего 2-х каскадного Дш удобно использовать разрешающий вход одного из Дш 1-го каскада. При этом запрашиваются либо все строки, либо все столбцы.

При сравнении различных типов Дш:

При большом числе выходов (сотни и более) прямоугольный Дш – самый экономический по оборудованию, чем объясняется его широкое применение в БИС34.

При уменьшении числа выходов до нескольких десятков более экономичными являются каскадные дешифраторы, а при малом числе выходов самым экономичными быстродействующим является линейный Дш.

Выше сказанное справедливо для Дш, построенных непосредственно на логических элементах. При проектировании блоков из готовых ИС, когда затраты оборудования определяется не числом элементов, а количеством корпусов, даже большие Дш экономичнее строить по каскадному принципу на основе Дш 3-8 или 4-16.

Обозначение Дш. Дш, выпускаемые в виде отдельных микросхем, имеют буквенные обозначения ИД. В сериях ТТЛ (элементы И-НЕ) Дш обычно имеют инверсные выходы. В КМДП – сериях (ИЛИ-НЕ) – прямые выходы.

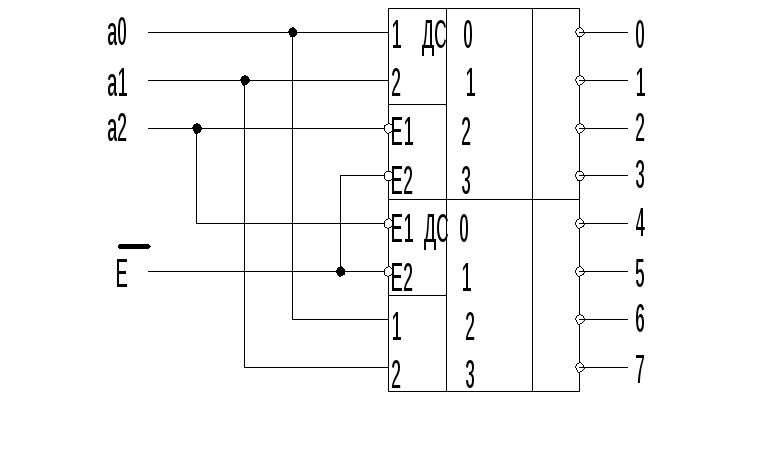

Часто в микросхемах Дш делают несколько разрешающих входов, а разрешающей комбинацией является их конъюнкция. При этом удобно наращивать Дш, используя каскадный принцип и строя 1 каскад дешифрации не на отдельных спец. Дш, а собирая его из конъюнкторов разрешающих входов.

Дш 5-32 построен на 4-х 3-8.

Ниже приводится еще одна схема, в которую входят 2 декодера – демультиплексора 2-4 (К155ИД4).

Каждый

декодер имеет по 2 разрешающих входов.

Один вход одной из секций инвертирован.

Это позволяет объединив его с не

инвертированным разрешающим входом

другой секции и подав на эту пару третью

переменную a4,

использовать ту же схему как Дш 3-8 с

разрешающим входом

![]() .

.

Универсальная микросхема дешифратора 4-10 и декодера-дешифратора 3-8.

Шифраторы.

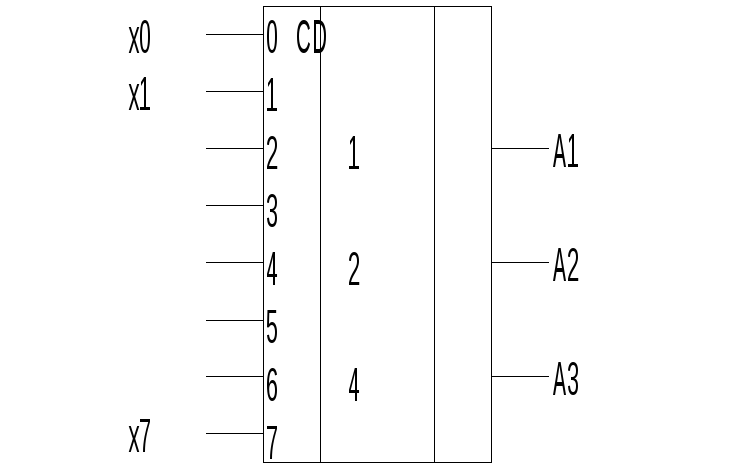

Шифратор, или кодер, выполняет операцию, обратную дешифратору.

Условное обозначение.

Классический шифратор имеет m – входов и n – выходов, и при подаче сигнала на один из входов, на выходе появляется двоичный код номера возбужденного кода.

Число входов связано между собой m=2n.

Шифратор можно использовать, например, для отображения в виде двоичного кода по мере нажатой кнопки, или положения многопозиционного переключателя, а также для определения номера устройства, подавшего сигнал запроса на обслуживание в микропроцессорных системах, входя в состав контроллеров прерывания.

Двоичные шифраторы преобразуют код “1 из N” в двоичный код, т.е. выполняют микрооперацию, обратную функции дешифратора. При возбуждении одной из входных цепей шифраторе на его выходах формируется слово, отображающие номер возбужденной цепи. Полный двоичный Ш. имеет m=2n входов и n выходов.

Одно из основных применений шифратора – ввод данных с клавиатуры, при котором нажатие клавиши с десятичной цифрой должно приводить к передаче в устройство двоичного кода данной цифры (тетрада 2/10 кода).

|

xi |

A3 |

A2 |

A1 |

|

x0 |

0 |

0 |

0 |

|

x1 |

0 |

0 |

1 |

|

x2 |

0 |

1 |

0 |

|

x3 |

0 |

1 |

1 |

|

x4 |

1 |

0 |

0 |

|

x5 |

1 |

0 |

1 |

|

x6 |

1 |

1 |

0 |

|

x7 |

1 |

1 |

1 |

Вопросы для контроля:

-

Какие комбинационные схемы называются дешифраторами?

-

Какой дешифратор называется полным?

-

Что за вход E и для чего он используется?

-

Как можно увеличить размерность дешифратора (увеличить количество входов)?

-

Для чего используется шифратор?

-

Как он работает?

Литература:

-

Угрюмов Е.П. Проектирование элементов и узлов ЭВМ – М.; Высш.шк., 1987, с.160-164.

-

Схемотехника ЭВМ. Учебник для ВУЗов под редакцией Соловьева Г.Н. – М.; Высш.шк., 1985, с.110-112.

-

Микропроцессоры т.2/ Под редакцией М.Н.Преснухина – М.; Высш.шк., 1986, с.118-121.