лабораторные работы / Лабораторная работа 3

.docЛабораторная работа №3.

Исследование параллельного, последовательного и универсального регистров.

На плате П-2 (карты П-5, П-6)

На плате П-3 (карты Ш-1, Ш-2, Ш-3)

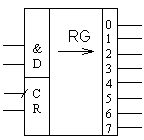

(RG)

Регистрами называются устройства, выполняющие функции приема, хранения и передачи информации.

Информация в регистре хранится в виде числа, представленного комбинацией 0 и 1. Каждому разряду числа, записанному в регистр, соответствует свой разряд регистра, выполненный, как правило, на основе триггеров RS, D, JK- типов.

По способу записи информации, регистры делятся на 3 типа;

-

Параллельные;

-

Последовательные;

-

Параллельно-последовательные.

В параллельные регистры запись числа осуществляется параллельным кодом, т.е. во все разряды одновременно.

Последовательные регистры характеризуются последовательной записью кода числа, начиная с младшего или старшего разряда, путем последовательного сдвига кода тактирующими импульсами (сдвиговые).

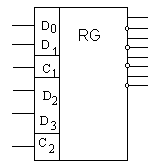

Параллельные регистры (регистры памяти) используются для записи и хранения небольшого объема цифровой информации (1-2 Байта). Рассмотрим параллельный регистр на D-триггерах, где каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый информационный выход. Тактовые входы (С) всех триггеров объединены между собой. В результате параллельный регистр представляет собой многоразрядный, многовходовый триггер.

С

Т

D

D0 Q0

D0 Q0

С

Т D

D1 Q1

D1 Q1

С

Т D

Dn Qn

C

Пример: 4-х разрядный регистр памяти, на микросхемах D-триггера 155 ТМ7

x 1

При у1=1-происходит параллельная

запись

1

При у1=1-происходит параллельная

запись

x2 значений сигналов xi в регистр.

При у1=0- записанная информация хранится в регистре.

x3

x4

y1

Параллельные регистры делятся на 1) регистры, срабатывающие по фронту управляющего сигнала (тактируемые регистры), 2) регистры, срабатывающие по уровню управляющего сигнала С (отроббируемые регистры).

Принцип действия регистров, срабатывающие по фронту С, не отличается от принципа действия D-триггеров. По / фронту тактового сигнала С каждый из выходов регистра устанавливается в тот уровень, который был в этот момент на соответствующем данному выходу входе D и сохраняется таким до прихода следующего положительного фронта сигнала С. То есть, если триггер запоминает один сигнал, то регистр запоминает сразу несколько (4, 6, 8, 16). Память регистра сохраняется до момента включения питания схемы.

Параллельные регистры, срабатывающие по фронту, различаются:

-

количеством разрядов

-

наличием или отсутствием инверт. выхода.

-

наличием входа сброса – R или разрешения записи – WE

-

типом выходных каскадов (2С или 3С)

-

наличием или отсутствием входа разрешения – EZ

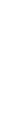

Он может рассматриваться как регистр, т.к. С и вход

сброс R у 4 триггеров объединены между собой

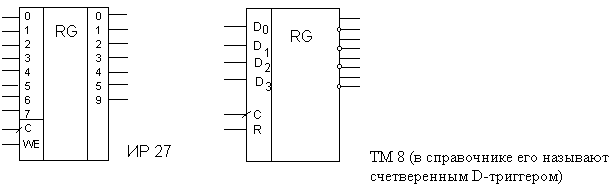

Таблицы истинности регистров практически не отличаются от таблиц D-триггеров. Отличие только для WE и EZ.

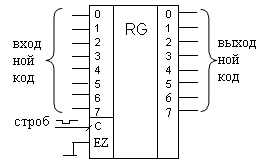

Для ИР 27

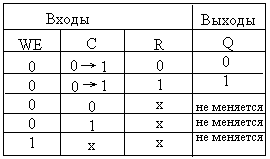

Одно из основных применений регистров состоит в хранении требуемого кода в течении нужного времени.

С

троб

троб

Принцип работы: Код на входе регистра может изменяться, но в момент, когда код принимает необходимое значение, на вход С подается сигнал (строб), который записывает код в регистр. Этот код будет храниться в регистре до прихода следующего строба.

Параллельные регистры, срабатывающие по уровню стробир. сигнала – гибрид между буфером и регистром. Когда сигнал строб =1, регистр пропускает через себя входные информационные сигналы, а когда строб =0, переходит в режим хранения последнего из пропущенных значений входных сигналов (применение таких регистров ограничено).

Пример:

м/с

ТМ 7: 4-разрядный регистр.

м/с

ТМ 7: 4-разрядный регистр.

М/с состоит из 4-х триггеров, строббирующие входы С, соединены попарно. Входы С1 и С2 м/с управляют каждый двумя разрядами данных.

ТМ6 7

|

Входы |

Выходы |

||

|

D |

C |

Q |

Q |

|

0 1 |

1 1 |

0 1 |

1 0 |

|

0 |

0 |

не меняется |

|

|

1 |

0 |

не меняется |

|

При С=0 на выходе регистра хранится та входная

информация, которая была в момент прихода отр.

фронта сигнала С.

!!! Информация на выходе меняется не только по

фронту, но и в момент изменения входных сигналов

при С=1 Основное применение регистра срабатывает по уровню строббирования сигнала, в запоминании на какое-то заданное время входного кода, причем, в остальное время выходной код регистра должен повторять входной. Строббирующий сигнал, в этом случае должен быть отрицательным на все время запоминания. Регистр, продлевает во времени необходимое значение входного кода, в остальное время, работая, как повторитель.

Строб

повт. входной время запоминания повт. входной

с игнал сигнал

игнал сигнал

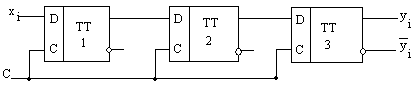

П оследовательные

(сдвиговые регистры) представляют

собой последовательную соединенную

цепочку триггеров (выход каждого

предыдущего триггера соединен со входом

D следующего триггера).

Тактовые входы всех триггеров (С)

объединены между собой. В результате,

такой триггер может рассматриваться

как линия задержки, входной сигнал

которой последовательно перезаписывается

из триггера в триггер по фронту тактового

сигнала С. Информационные входы и выходы

триггеров могут быть выведены наружу,

а могут и не выводиться, в зависимости

от функций, выполняемых регистром.

Основной режим их работы – это сдвиг

(вправо) разрядов кода, записанного в

эти триггеры, т.е. по тактовому сигналу

содержимое каждого предыдущего триггера

переписывается в следующий по порядку

в цепочке триггер. Код, хранящийся в

регистре, с каждым тактом сдвигается

на 1 разряд в сторону старших или младших

разрядов (сдвиг вправо – основной режим,

есть у всех сдвиг. регистров; влево –

только у реверсивных сдвиг. регистров).

оследовательные

(сдвиговые регистры) представляют

собой последовательную соединенную

цепочку триггеров (выход каждого

предыдущего триггера соединен со входом

D следующего триггера).

Тактовые входы всех триггеров (С)

объединены между собой. В результате,

такой триггер может рассматриваться

как линия задержки, входной сигнал

которой последовательно перезаписывается

из триггера в триггер по фронту тактового

сигнала С. Информационные входы и выходы

триггеров могут быть выведены наружу,

а могут и не выводиться, в зависимости

от функций, выполняемых регистром.

Основной режим их работы – это сдвиг

(вправо) разрядов кода, записанного в

эти триггеры, т.е. по тактовому сигналу

содержимое каждого предыдущего триггера

переписывается в следующий по порядку

в цепочке триггер. Код, хранящийся в

регистре, с каждым тактом сдвигается

на 1 разряд в сторону старших или младших

разрядов (сдвиг вправо – основной режим,

есть у всех сдвиг. регистров; влево –

только у реверсивных сдвиг. регистров).

С каждым тактовым импульсом С информация, стоящая на входе xi, записывается в 1 триггер, а из других триггеров смещается на 1 разряд вправо. За три такта может быть записано трехразрядное число, а затем за следующие 3 такта полностью выведено на выход регистра yi.

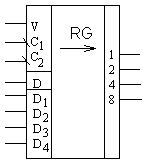

Ч асто

требуются более сложные сдвигающие

регистры: с параллельной синхронной

записью информации; реверсивные;

реверсивные с параллельной синхронной

записью информации. Такие регистры

называются универсальными регистрами.

Примером сдвигающего регистра с

синхронной записью информации является

м/с 155 ИР1

асто

требуются более сложные сдвигающие

регистры: с параллельной синхронной

записью информации; реверсивные;

реверсивные с параллельной синхронной

записью информации. Такие регистры

называются универсальными регистрами.

Примером сдвигающего регистра с

синхронной записью информации является

м/с 155 ИР1

Входы D1- D4 – предназначены для параллельной записи информации, вход D – для последовательной записи. Вход V является управляющим. При V=0 – схема работает, как двигающий регистр по отрицательному перепаду (с1 на 0) сигнала С1, а при V=1 – схема работает в режиме синхронной записи в регистр значений сигналов D1- D4 по отрицательному перепаду сигнала С2.

Последовательные (сдвиговые регистры) в них триггеры нумеруются слева на право от 0 до7 (для 8-ми разрядных регистров). Сдвиг вправо – это сдвиг в сторону разрядов, имеющих большие номера, сдвиг влево - разрядов, имеющих меньшие номера. Сдвиг влево – в сторону старших разрядов, вправо – младших.

В двоичном коде:

с

лева

справа

лева

справа

старшие младшие

разряды разряды

Последовательные регистры отличаются:1 режимом работы; 2 режимом записи; 3 режимом чтения и сдвига; типом выходных каскадов (2С или 3С)

Большинство регистров сдвига имеют 8 разрядов.

И Р8

– самый простой из регистров сдвига.

Он представляет собой 8-ми разрядную

линию задержки, т.е. имеет 1 информационный

вход, на который подается последовательно

сдвигаемая информация (точнее 2 входа,

обычно И (2И)) и 8 параллельных выходов.

Сдвиг в сторону выходов со старшими

номерами осуществляется по переднему

фронту / тактового

сигнала С.

Р8

– самый простой из регистров сдвига.

Он представляет собой 8-ми разрядную

линию задержки, т.е. имеет 1 информационный

вход, на который подается последовательно

сдвигаемая информация (точнее 2 входа,

обычно И (2И)) и 8 параллельных выходов.

Сдвиг в сторону выходов со старшими

номерами осуществляется по переднему

фронту / тактового

сигнала С.

Вход сброса R – по его нулевому сигналу все выходы регистра сбрасываются в 0.

|

Входы |

Выходы |

||||||

|

R |

C |

D1 |

D2 |

Q0 |

Q1 |

… |

Q7 |

|

0 |

X |

X |

X |

0 |

0 |

… |

0 |

|

1 |

0 |

X |

X |

не меняется |

|||

|

1 |

1 |

X |

X |

не меняется |

|||

|

1 1 1 |

0 0 0 |

1 0 1 |

1 X 0 |

1 0 0 |

Q0 Q0 Q0 |

… … … |

Q6 Q6 Q6 |

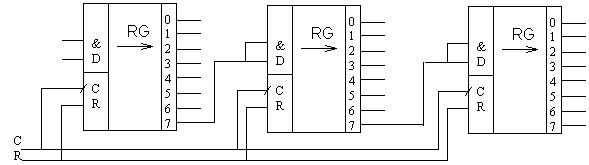

В ходной

последовательный код преобразовался

в 24-разрядный выходной параллельный

код.

ходной

последовательный код преобразовался

в 24-разрядный выходной параллельный

код.

1

1 1

1 1

1