1.2 Rs триггеры

RSтриггер составлен с использованием двух информационных входов:RиS.

1.2.1 Асинхронный RSтриггер - элементарный цифровой автомат с двумя входами и двумя устойчивыми состояниями.

Таблица переходов.

|

Qt |

R |

S |

Qt+1 |

|

0 0 0 0 1 1 1 1 |

0 0 1 1 0 0 1 1 |

0 1 0 1 0 1 0 1 |

0 (хранение 0) 1 (установка 1) 0 (установка 0) x(неопределенное состояние) 1 (хранение 1) 1 (подтверждение 1) 0 (установка 0) x(неопределенное состояние) |

Характеристическое уравнение:

Q

t+1=Qt-1RtVSt; (1)

t+1=Qt-1RtVSt; (1)

R*S=0

Выбрав в качестве

элементной базы И - НЕ, преобразуем

уравнение (1) с применением теоремы де

Моргана:

![]()

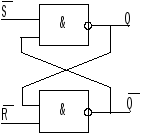

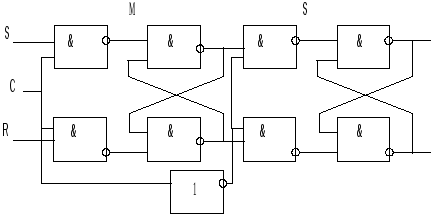

С хемаRSтриггера, реализующего

данное выражение:

хемаRSтриггера, реализующего

данное выражение:

Рисунок 1

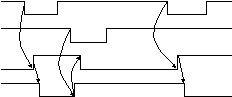

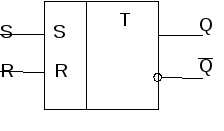

Для данного триггера комбинация входных сигналов Rt=0 иSt=0, является запрещенной, а комбинацияRt=1 иSt=1 не меняет его предыдущего состояния. На рис. 2 приведено обозначение триггера (б) и временная диаграмма (а).

S

R

Q

Q

Q

а) б)

Рисунок 2

В

ыбрав

в качестве элементной базы базис ИЛИ-НЕ

и используя закон отрицания,

получим:Qt+1=RtV(QtVSt).

В данном случае соединение элементов

обеспечивает два устойчивых состояния.

ыбрав

в качестве элементной базы базис ИЛИ-НЕ

и используя закон отрицания,

получим:Qt+1=RtV(QtVSt).

В данном случае соединение элементов

обеспечивает два устойчивых состояния.

Рисунок 3 Рисунок 4

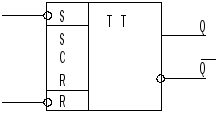

На рис. 4 приведено обозначение RS-триггера, на рис. 5 - временная диаграмма.

S

R

Q

Q

Рисунок 5

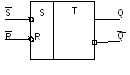

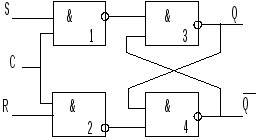

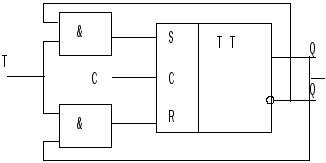

1.2.2 Синхронные RSтриггеры. На входы логического элемента сигналы не всегда поступают одновременно, так как перед этим могут проходить разное число узлов. Это явление называют состязаниями или гонками, в результате чего могут произойти ложные срабатывания ЛЭ. Для устранения такого явления используется синхросигнал, то есть на элемент кроме информационных сигналов подаются тактирующие, к моменту прихода которых информационные сигналы успевают установиться на входах. На рис. 6 приведено условное обозначение (б) и схема (а).

а) б)

Рисунок 6

Элементы И-НЕ1и И-НЕ2передают переключающую логическую 1 с информационного входаRилиSна соответствующие входыRSтриггера с инверсными входами только при наличие на синхронном входе С уровня логической 1.

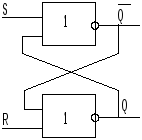

1 .2.3

Двухступенчатый синхронныйRSтриггер. Строится на базе двух

последовательно соединенных одноступенчатыхRSтриггеров со специальной

организацией цепи синхронизации.

.2.3

Двухступенчатый синхронныйRSтриггер. Строится на базе двух

последовательно соединенных одноступенчатыхRSтриггеров со специальной

организацией цепи синхронизации.

Рисунок 7

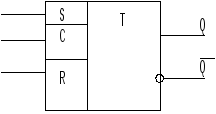

На рис.8 приведено обозначение двухступенчатого синхронного RSтриггера.

Рисунок 8

При с=1 осуществляется прием информации в 1-ый триггер, а при с=0 – передача информации с 1-го во 2-ой и блокируются информационные входы первого триггера. Поэтому схема состояния триггера для внешних схем происходит при переходе сигнала синхронизации из 1 в 0.

1.3 Т- триггер

Имеет только один информационный вход Т, называемый счетным входом и изменяет свое состояние после прихода на счетный вход Т каждого управляющего (счетного) сигнала.

Таблица переходов.

|

Qt |

Tt |

Q(t+1) |

|

0 0 1 1 |

0 1 0 1 |

0 1 1 0 |

Х арактеристическое

уравнение:

арактеристическое

уравнение:

Q t+1=TtQtVTtQt;

приTt=0,

получаемQt+1=Qt,

приTt=1,

получаемQt+1=Qt.

t+1=TtQtVTtQt;

приTt=0,

получаемQt+1=Qt,

приTt=1,

получаемQt+1=Qt.

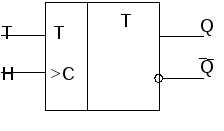

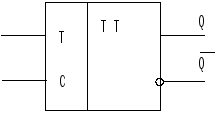

На

рис. 9 представлено обозначениеT-триггера.

На

рис. 9 представлено обозначениеT-триггера.

Рисунок 9

Триггер реализует операцию сложения по модулю 2. Сигнал на выходе Qпоявляется в 2 раза реже, чем на входе Т.

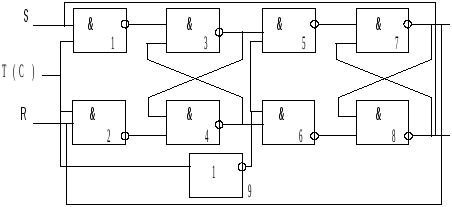

1.3.1 Асинхронный Т- триггер. Он может быть построен на базе двухступенчатого синхронного RSтриггера с дополнительными связями. В исходном состоянии (R=S=0) при Т=0 происходит постоянное копирование состояния триггера М триггеровS, так как элемент И-НЕ9выдает уровень 1 на входы И-НЕ5и И-НЕ6.

Рисунок 10

Если Т-триггер находится в состоянии 0, то (Q=0) , то на входеR=0 и входеS=0.

При поступлении на вход Т первого счетного сигнала (Т=1) в триггер (М) запишется 1 уровнем логического 0 с выхода логического элемента И-НЕ1. Состояние триггера (S) при этом не изменится, так как уровень логического 0 с выхода элемента И-НЕ9будет блокировать его состояние. После окончания действия второго счетного сигнала на входе Т (Т=0) в триггер (S) запишется 0 уровнем логического 0 с выхода элемента И-НЕ6. На выходах Т-триггера произойдет изменение потенциалов (Q=0,Q=1), а также наRиS-входах триггера М. Таким образом, каждый счетный сигнал на входе Т переводит триггер М в противоположное состояние.

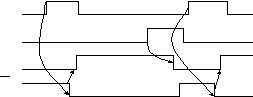

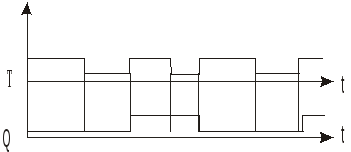

Временная диаграмма работы Т-триггера приведена на рис.11.

Рисунок 11

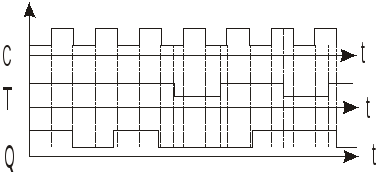

1.3.2 Синхронный Т-триггер двухтактный.

Обозначение и временная диаграмма:

а) б)

Рисунок 12

Из временной диаграммы видно, что при наличии на входе Т сигнала высокого уровня каждый синхронизирующий сигнал на входе С будет переключать триггер из единичного состояния в другое (при переходе С из 1 в 0).