экзаменационные вопросы и ответы / 44 АЦП / АНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ

.docxАНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ

Под аналого-цифровыми преобразователями (ЦАП) понимают устройства, позволяющие осуществить переход от информации в аналоговой форме к информации в цифровой форме. Эти преобразователи широко используются для ввода в ЭВМ аналоговых данных, при цифровом изменении аналоговых сигналов, для перехода к цифровым сигналам, в системах автоматического регулирования и управления. Вместе с ЦАП рассматриваемые преобразователи используются в микропроцессорных устройствах.

Основными характеристиками АЦП являются: разрешающая способность, точность и быстродействие. Разрешающая способность определяется разрядностью и максимальным диапазоном входного аналогового напряжения (полной шкалой). Точность определяется абсолютной погрешностью полной шкалы δпш , нелинейностью и дифференциальной нелинейностью, которые определяются, как у ЦАП, но только по отношению к входному сигналу. Быстродействие АЦП характеризуется временем преобразования tпрб, т. е. интервалом времени от момента заданного измерения сигнала на входе до появления на выходе установившегося кода.

По структуре построения АЦП можно классифицировать на АЦП с применением ЦАП и без них. К первому типу относятся АЦП, структурные схемы которых приведены на (рис. 6) . В настоящее время в интегральном исполнении реализованы АЦП развертывающего типа. Развертывающий АЦП переводит аналоговый сигнал в цифровой последовательно, начиная с самого младшего значения до уровня, пока выходное аналоговое напряжение ЦАП не уравняется с входным аналоговым напряжением АЦП. К этому типу АЦП можно отнести АЦП последовательного приближения со счетчиком.

На рис. 7 дана упрощенная схема АЦП последовательного счета. На многоразрядный счетчик поступает тактовая частота от генератора, который запускается в момент захвата входного аналогового сигнала. Выход счетчика управляет схемой ЦАП, вырабатывающей ступенчато-нарастающее напряжение. В момент, когда выходное напряжение схемы ЦАП сравняется с входным напряжением, компаратор переключается и останавливает счетчик, код в котором в этот момент будет соответствовать входному аналоговому сигналу. Время преобразования здесь наибольшее: Тпр= τ2N, где τ -время элементарной ступени; N—- число разрядов. Большая потребность в АЦП этого типа Послужила причиной разработки специализированной ИС К572ПВ1 (рис. 6.86,а), представляющей собой ЦАП со схемой управления и логическим устройством. При подключении компаратора микросхема К572ПВ1 может выполнять функции АЦП последовательного приближения с параллельным двоичным кодом на выходах (рис. 8,6).

Рис. 6. Типы АЦП:

а — следящий; б — развертывающий;

в — поразрядного уравновешивания. Выводы: 1 — реверсивный счетчик; 2- счетчик; 3 — триггер; 4 — схема управления; 5 — запоминающий регистр; 6 — аналоговый вход; 7 — цифровой параллельный выход; 8 — цифровой последовательный выход; S — синхроимпульсы; 10 — пусковой импульс; 11 — сброc

Наличие схем входной и выходной логики обеспечивает побайтовый вывод и ввод цифровой информации для согласования с 8-разрядной шиной данных.

С целью уменьшения числа вспомогательных элементов разработан функционально законченный, совместный с МП серии K.58Q и другими, работающими с ТТЛ уровнями АЦП последовательного приближения.

Рис. 7. АЦП последовательного счета:

I — ЦАП; 2 — счетчик о логическим управлением; 3 — аналоговый вход; 4 — цифровой параллельный выход; S — пуск; S — сброс; 7 — тактовые импульсы; t — «сигнал «Стоп»

него приближения К1ИЗПВ1 (А, Б, В). БИС АЦП имеет внутренний источник опорного напряжения, тактовый генератор и компаратор напряжения. Для включения АЦП необходимы только источники питания и

формирователь преобразования.

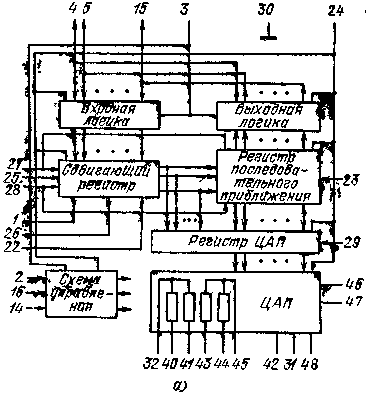

Рис. 8. АЦП К572ПВ1:

а — функциональная схема; б — схема включения.

Выводы: 1 — цифровой последовательный вход; 2 — вход управления выходами старших разрядов; 3 – Uип1; 4 (СЗР) ... 15 (МЗР) — цифровые входы (выходы); 16 — вход управления входами-выходами младших разрядов; 17 — вход управления режимом ЦАП-АЦП; 22 — выход «Цикл»; 23 — вход сравнения; 24 - Uип2; 25 — вход тактовых импульсов; 26 — выход «Конец преобразования»; 27 — вход «Запуск»; 28 — вход «Цикл»; 29 — стробирование ЦАП; 36 — цифровая земля; 31 — конечный вывод матрицы R—2R; 32 — общий вывод резисторов R1 и R2; 40 и 41 — выводы резисторов R1 и R2; 42 — опорное напряжение; 43 к 44 — аналоговые входы / и 2; 4S — общий вывод резисторов аналоговых входов; 46 и 47 — аналоговые выходы 1 и 2; 48 — аналоговая «земля».

Схема построения АЦП приведена на рис.7. АЦП имеет выходные устройства с тремя устойчивыми состояниями, что упрощает его сопряжение с шинами данных МП: несколько АЦП могут обслуживать один МП, и наоборот.

Рис. 9. АЦП K1l1ЗПВ1:

а — функциональная схема [1 — ЦАП; 2 — регистр последовательного приближения (РПП; 3 — буферный усилитель; 4 — компаратрр: 5 — схема управления сдвигом нуля; б — генератор; 7 — источник опорного напряжения; 8 — делитель; S — схема формирования сигнала «готовность данных»; 10 — схема управления преобразованием и выводом данных]; б— схема включения. Выводы: 1 (9- й разряд) ... 9 (СЗР) — цифровые выходы; 10 – Uип1; 11 - вход управления выводом и вводом данных; 12 — Uип2; 13 — аналоговый вход; 14 — аналоговая «земля»; 15 — управление сдвигом нуля; 16 — цифровая «земля»; 17 — выход готовности данных; 18 — МЗР; в — схема включения в МП систему.

Режим работы ИС в микропроцессорной системе определяется управляющими импульсами от МП. При поступлении на вход «гашение и преобразование» ИС К1НЗПВ1 уровня логического нуля АЦП начинает преобразование входной информации. Через время, необходимое для преобразования на выходе АЦП «Готовность данных», появляется сигнал с уровнем логической единицы» запрашивающий вывод данных с АЦП на шину данных системы. МП, приняв данные в системную магистраль, устанавливает на входе «Гашение и преобразование» АЦП уровень логической единицы, который «гасит» информацию, содержащуюся в регистре последовательного приближения, и АЦП снова готов к приему и обработке входных данных.

АЦП может обрабатывать входную информацию в виде однополярного аналогового напряжения до 10,24 В и двухполярного ±5,12 В. При включении АЦП в двухполярном режиме вывод 15 (управление сдвигом нуля) должен быть открыт, а в однополярном режиме его необходимо соединить с выводом цифровая «земля». ИС КШЗПВ1 допускает предварительную установку смещения нуля входного напряжения. В зависимости от точности регулирования и диапазона необходимой шкалы входного напряжения применяются различные варианты схем регулирования смещения. Так, при работе с максимальным диапазоном входного сигнала 10,24 В регулирование можно проводить переменным резистором 100... 200 Ом, подключенным между источником сигнала и аналоговым входом (13).

Регулировку смещения нуля в диапазоне ± 1/2 единицы МЗР можно проводить переменным резистором 5... 50 Ом, подключенным с вывода 14 (аналоговая «земля») на «землю», а для устранения влияния смещения в диапазоне ±3 единицы МЗР применяется более сложная схема, состоящая из четырех резисторов.

Еще одним примером законченного АЦП последовательного приближения может служить 10-разрядный быстродействующий АЦП ИС КН08ПВ1 (рис. 10), работающий совместно с ТТЛ ЦИС и имеющий время преобразования не более 0,9 мкс .

Рис. 10. АЦП последовательного приближения КП08ПВ1:

1— ЦАП; 2 — регистр последовательного приближения; 3 - выходной регистр на три состоя; 4 — тактовый генератор; 5 — источник опорного напряжения; 6 — компаратор; 7 - ОУ. Выводы: 1(СЗР) ... 10 (МЗР) — цифровые выходы; ;1 — готовность данных; 12, 15, 16. 21 — частотная компенсация узлов схемы АЦП; 14 — цифровая «земля»; 13 — управление разрядностью выходных данных: 17 — аналоговый вход; I8 — опорное напряжение; 20 — общий; 19 — компенсация схемы опорного напряжения; 22 — вход запуска; 23 — вход внешних тактовых импульсов; 24 — вход разрешения считывания

Схема АЦП включает ЦАП, источник опорного напряжения, тактовый генератор, регистр последовательного приближения и выходной регистр на три состояния с хранением информации в течение последующего цикла преобразования. ИС КН08ПВ1 предусматривает работу в 10- и 8-разрядных режимах. Время преобразования аналоговой информации в 8-разрядный код не более 0,5 мкс. Десятиразрядный режим устанавливается подключением вывода 13 (укороченный цикл) к выводу 14 (цифровая «земля»), при 8-разрядном режиме вывод 13 соединяется с выводам 15.

ИС предусматривает работу в режимах с внутренним и внешним источниками опорного напряжения. При работе с внутренним источником опорного напряжения необходимо вывод 19 (компенсация источника опорного напряжения) через резистор 1 кОм подключить на «землю». Внешнее опорное напряжение может быть подано на вывод 18, при этом вывод 19 подключается на «землю» через конденсатор 0,47 мкФ.

Работа микросхемы во времени определяется тактовыми импульсами (см. рис. 10). При работе с внутренним тактированием выввд 23 (тактовый вход) необходимо через конденсатор емкостью 25 пФ подключить на «землю». При внешнем тактировании на этот вывод подаются тактовые импульсы системы (уровень ЭСЛ). Выборка АЦП производится по переднему фронту тактового импульса и длится 12 периодов. Преобразование информации заканчивается выдачей сигнала АЦП в систему о готовности данных (уровень логического нуля на выводе, готовность данных). Вывод информации из АЦП на шину данных осуществляется по сигналу «Разрешение считывания» (уровень логического нуля ТТЛ), поступающего на вывод 24 от МП. ИС предусматривает высокоимпедансное состояние выходного регистра, для чего на вывод 24 необходимо подать напряжение 2,4 В. К схемам АЦП без применения ЦАП относятся АЦП двойного интегрирования и параллельного действия. Способ двойного интегрирования позволяет хорошо подавлять сетевые помехи, кроме того, для построения схемы АЦП не требуется схем ЦАП с высокоточными резистивными матрицами. Функциональная схема АЦП двойного интегрирования показана на рис. 11 и напоминает схему АЦП последовательного счета, в которой вместо ЦАП применен интегратор. Счетчик запускается от генератора в момент поступления на интегратор входного сигнала UBX, из которого за время интеграции делается выборка.

Рис. 11. Метод АЦП двойного интегрирования:

а- функциональная схема (1 — ключ; 2 — пороговая схема; 3 — логическое устройство; 4 — делитель; 5 — генератор); б — эпюры напряжений

За время выборки напряжение на выходе интегратора Uи увеличивается. В момент tи прямая интеграции заканчивается, входной сигнал от интегратора отключается и к его суммирующей точке подключается эталонный резистор. От времени tи до моментов t1 ... t2 продолжается разряд интегратора (обратная, вторая интеграция) с постоянной скоростью. Интервалы времени от tи до нулевых отметок (t1,t2,,t3) пропорциональны уровню входного сигнала. Существенным преимуществом преобразователя считается простота синхронизации с напряжением сети, а значит, и простота компенсации сетевых наводок. Примером ИС, предназначенной для построения АЦП двойного интегрирования, может служить БИС АЦП КР572ПВ2, включающая аналоговые КМ ОП схемы компаратора и ОУ, а также цифровые КМОП схемы. На рис. 6.90 приведена основная схема включения этого АЦП. При подключении трех внешних резисторов и пяти конденсаторов БИС КР572ПВ2 выполняет функцию АЦП, работающего по принципу двойного интегрирования с автоматической коррекцией нуля и автоматическим определением полярности входного сигнала. Таким образом, эта ИС представляет собой электронную часть цифрового вольтметра. Шкалы измеряемого входного сигнала — до ±1,999 В и до ±199,9 мВ. Цифровая информация на выходе АЦП представляется в семисегментном коде.

Рис. 12. АЦП двойного интегрирования К572ПВ2.

Выводы: I — 1/„ П1; 2 ... S — цифровые выходы младшей цифры dl, cl,b1, a1 ,fI, g[, el соответственно; 9 ... 14 — цифровые выходы dlO, с]0, b10. a10, f10, e10; 15 ... 18 — цифровые выходы d100,b100, f1ОО, e100; 19, 20 — цифровые выходы dc10ОО, g1000; 21 — общий; 22 ... 24— цифровые выходы glOO, a100, с10О; 25 — g10; 26 —Uип2; 27 — конденсатор интегратора; 28 — резистор интегратора; 29— конденсатор автокоррекции; 30— аналоговый вход / ( + ); 31— аналоговый вход 2; 32 — аналоговый выход; 33, 34 — опорный конденсатор; 35, 36 — опорное напряжение ( + ) и (—); 37 — контрольный вход; 38 — конденсатор генератора; 39 — резистор генератора; 40 — вход генератора ТИ

Цифровой отсчет производится на 3,5-декадном индикаторе. В табл. 6.17 приведены значения номиналов навесных элементов для fтакт = 50 кГц При необходимости использовать другое значение fтакт номинал С5 можно определить по формуле С5=0,45/(fтакт R 3). Для повышения стабильности тактовой частоты может быть использован кварцевый резонатор, подключаемый между выводами 39 и 40, при этом элементы С5 и R3 не используют. При работе от внешнего генератора тактовые импульсы подают на вывод 40, а выводы 38 и 39 не используют.