- •1.Общая структура эвм

- •2.Общая архитектура микропроцессора

- •3.Работа микроЭвм.

- •4.Полупроводниковая память и её использование в микропроцессорной технике.

- •5.Эксплуатационные параметры зу.

- •6.Режимные параметры зу

- •7.Структура 2d.

- •8.Структура 3d

- •11.Статическая память (sram)

- •12.Зэ динамические зу

- •14.Внешняя организация и временные диаграммы динамических зу.

- •15.Постоянные Запоминающие Устройства пзу.

- •16.Однократно (электрически) программируемые пзу.

- •17.Репрограммируемые пзу.

- •22.Структура элементарного микропроцессора.

- •24.Функционирование микропроцессорной системы

- •26.Микропроцессор

- •27.Обработка микропроцессором требования прерывания.

- •28.Прерывание с программным опросом.

- •29.Векторная система прерываний.

- •30.Структура приоритетов.

- •31.Синхронизация микропроцессорной системы.

- •32.Программирование микропроцессоров.

- •33.Архитектурные особенности современных микропроцессоров.

- •34.Иерархическая структура памяти.

- •36. Архитектурно независимая спецификация программ.

- •38.Универсальные микропроцессоры.

- •39.Микропроцессор с архитектурой х86.

- •45.Структурная схема базовой модели микропроцессора семейства х86

- •46.Однокристальные микро эвм (микроконтроллеры).

12.Зэ динамические зу

В качестве ёмкостных конденсаторов в ЗЭ чаще всего используют однотранзисторные элементы, так как на них можно получить предельно компактные ЗЭ. Рассмотрим схему и конструкцию однотранзисторного запоминающего элемента: (полевой транзистор с изолированным затвором с индуцированным каналом р – типа).

Рис.14 Полевой транзистор

Основа ЗЭ –

запоминающий конденсатор

![]() .

Транзистор

.

Транзистор

![]() выполняет роль ключа. Он отключает или

подключает конденсатор к Линия

Записи Считывания ЛЗС.

Одну из обкладок конденсатора образует

не имеющий вывода сток транзистора.

Другой обкладкой служит подложка (основа

полупроводника). Роль диэлектрика

выполняет тончайший слой

выполняет роль ключа. Он отключает или

подключает конденсатор к Линия

Записи Считывания ЛЗС.

Одну из обкладок конденсатора образует

не имеющий вывода сток транзистора.

Другой обкладкой служит подложка (основа

полупроводника). Роль диэлектрика

выполняет тончайший слой

![]() толщиной 1,5 нм.

толщиной 1,5 нм.

В режиме хранения

данных транзистор

![]() заперт. При выборке конкретного ЗЭ на

затвор З

ключевого транзистора подаётся

положительное отпирающее напряжение.

Канал полевого транзистора становится

проводящим. Через него

заперт. При выборке конкретного ЗЭ на

затвор З

ключевого транзистора подаётся

положительное отпирающее напряжение.

Канал полевого транзистора становится

проводящим. Через него

![]() подключается к ЛЗС. Если ёмкость была

заряжена, её высокий потенциал передаётся

на ЛЗС, то есть устанавливается состояние

логической единицы "1".

Если ёмкость разряжена, на ЛЗС передаётся

потенциал, близкий к нолю, т.е. логический

ноль "0".

подключается к ЛЗС. Если ёмкость была

заряжена, её высокий потенциал передаётся

на ЛЗС, то есть устанавливается состояние

логической единицы "1".

Если ёмкость разряжена, на ЛЗС передаётся

потенциал, близкий к нолю, т.е. логический

ноль "0".

При записи данных

– наоборот, потенциал ЛЗС передаётся

на

![]() ,

определяя его состояние. Высокий

потенциал – логическая единица, низкий

– логический ноль.

,

определяя его состояние. Высокий

потенциал – логическая единица, низкий

– логический ноль.

Конструкция ЗЭ.

Рис.15 Конструкция запоминающего элемента

Процесс чтения состояния ЗЭ.

Рассмотрим фрагмент схемы ЗУ:

Рис.16 Фрагмент схемы запоминающего устройства

Фрагмент включает

ЗЭ.

![]() и т.д. и предназначен для записи/считывания

одного байта информации. Усилитель

считывания УС

считывает

и т.д. и предназначен для записи/считывания

одного байта информации. Усилитель

считывания УС

считывает![]() соответственно для записи «1» и «0». К

ЛЗС подключается столько ЗЭ, сколько

строк имеется в запоминающей матрице.

В нашем случае это

соответственно для записи «1» и «0». К

ЛЗС подключается столько ЗЭ, сколько

строк имеется в запоминающей матрице.

В нашем случае это

![]() .

В силу большой протяжённости ЛЗС и

большого количества подключаемых к ней

транзисторов, появляется паразитная

ёмкость

.

В силу большой протяжённости ЛЗС и

большого количества подключаемых к ней

транзисторов, появляется паразитная

ёмкость

![]() которая во много раз превышающая

которая во много раз превышающая

![]() .

Поэтому перед считыванием информации

производится предварительная зарядка

ёмкости

.

Поэтому перед считыванием информации

производится предварительная зарядка

ёмкости

![]() чаще всего до уровня

чаще всего до уровня

![]() питания. При считывании логического

ноля (

питания. При считывании логического

ноля (![]() разряжен), часть заряда заряжена до

уровня

разряжен), часть заряда заряжена до

уровня

![]() питания

ёмкости.

питания

ёмкости.

![]()

![]() перетекает

в

перетекает

в

![]() .

Напряжения на них уравниваются.

.

Напряжения на них уравниваются.

Потенциал ЛЗС

уменьшается на величину

![]() ,

который является сигналом, поступающим

на УС. Понижающая потенциала

,

который является сигналом, поступающим

на УС. Понижающая потенциала

![]() – логический ноль.

– логический ноль.

При считывании

логической единицы

![]() на

на

![]() ,

напротив, уменьшается, так как часть

заряда стекает на

,

напротив, уменьшается, так как часть

заряда стекает на

![]() ,

тем самым увеличивая потенциал на нём,

что является сигналом считывания

логической единицы для УС.

,

тем самым увеличивая потенциал на нём,

что является сигналом считывания

логической единицы для УС.

Рис.17 График зависимости U от t

В силу неравенства

ёмкостей

![]() сигнал

сигнал

![]() оказывается слабым. Поэтому используется

УС. Считывание оказывается разрушающим,

так как подключение

оказывается слабым. Поэтому используется

УС. Считывание оказывается разрушающим,

так как подключение

![]() изменяет её заряд.

изменяет её заряд.

Методы преодоления этих недостатков:

Увеличение ёмкости

![]() ,

уменьшение ёмкости

,

уменьшение ёмкости

![]() применение для считывания усилителей

– регенераторов, которые производят

перезапись после считывания.

применение для считывания усилителей

– регенераторов, которые производят

перезапись после считывания.

Ёмкость

![]() повышается, используя вместо

повышается, используя вместо

![]() двуокись титана. У двуокиси титана

диэлектрическая проницаемость в 20 раз

выше. Уменьшение ёмкости

двуокись титана. У двуокиси титана

диэлектрическая проницаемость в 20 раз

выше. Уменьшение ёмкости

![]() достигается разделением ЛЗС на две

части и включается в разрыв с ними УС.

достигается разделением ЛЗС на две

части и включается в разрыв с ними УС.

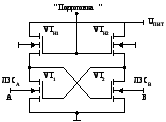

13.Усилители – регенераторы УР. Их строят на основе триггерных схем, введением в схему данного сигнала "Подготовка" для управления нагрузочными транзисторами.

Рис.18 График зависимости U от t

В начале сигнал

"Подготовка" имеет низкий уровень

и

![]() и

и

![]() (заперты). В этом состоянии УР воспринимает

слабые сигналы считываний с

(заперты). В этом состоянии УР воспринимает

слабые сигналы считываний с

![]() и

и

![]() .

Одна из половин ЛЗС, к которой не

подключена запоминающая ёмкость,

сохраняет напряжение предзаряда

.

Одна из половин ЛЗС, к которой не

подключена запоминающая ёмкость,

сохраняет напряжение предзаряда

![]() питания.

Напряжение на другой половине, к которой

подключается ЗЭ отклоняется от напряжения

предзаряда на

питания.

Напряжение на другой половине, к которой

подключается ЗЭ отклоняется от напряжения

предзаряда на

![]() в ту или иную сторону. Единица –

увеличивается, ноль – уменьшается.

Неравенство напряжений в точках А

и В

вносит несимметрию проводимости

транзисторов

в ту или иную сторону. Единица –

увеличивается, ноль – уменьшается.

Неравенство напряжений в точках А

и В

вносит несимметрию проводимости

транзисторов

![]() и

и

![]() .

.

Для считывания

и регенерации данных сигнал "Подготовка"

переводится на высокий уровень, в котором

транзисторы

![]() и

и

![]() открываются, возникает схема триггера,

находящегося в неустойчивом состоянии.

Такой триггер в силу своих триггерных

свойств быстро перейдёт в устойчивое

состояние, которое предопределяется

указанной ранее несимметрией режима.

А на выходах сформируются полные

напряжения высокого и низкого уровней.

Так как одни и те же точки А

и В

одновременно

являются и входами, и выходами усилителя

регенератора после своего срабатывания

он восстанавливает на ёмкости

открываются, возникает схема триггера,

находящегося в неустойчивом состоянии.

Такой триггер в силу своих триггерных

свойств быстро перейдёт в устойчивое

состояние, которое предопределяется

указанной ранее несимметрией режима.

А на выходах сформируются полные

напряжения высокого и низкого уровней.

Так как одни и те же точки А

и В

одновременно

являются и входами, и выходами усилителя

регенератора после своего срабатывания

он восстанавливает на ёмкости

![]() полное значение считанного сигнала,

чем и осуществляется регенерация данных.

полное значение считанного сигнала,

чем и осуществляется регенерация данных.

Мультиплексирование шины адреса

Особенностью

динамических ЗУ является мультиплексорные

шины адреса. Адрес делят на 2 полуадреса,

первый из которых является адресом

строки

(линии), другой является адресом

столбца матрицы

ЗЭ. Полуадреса подаются на одни и те же

выводы корпуса микросхем поочерёдно.

Подача адреса строки сопровождается

стробом RAS,

адреса столбца сопровождаются стробами

CAS.

Цель мультиплексирования – уменьшить

число выводов корпуса микросхемной

памяти, так как динамически ЗУ имеют

максимальную ёмкость, а, следовательно,

и большую разрядность адресов. Например,

ЗУ

![]() без мультиплексированной шины адреса

должно иметь 24 адресных вывода.

Мультиплексирование сокращает их число

до 12.

без мультиплексированной шины адреса

должно иметь 24 адресных вывода.

Мультиплексирование сокращает их число

до 12.