- •1.Общая структура эвм

- •2.Общая архитектура микропроцессора

- •3.Работа микроЭвм.

- •4.Полупроводниковая память и её использование в микропроцессорной технике.

- •5.Эксплуатационные параметры зу.

- •6.Режимные параметры зу

- •7.Структура 2d.

- •8.Структура 3d

- •11.Статическая память (sram)

- •12.Зэ динамические зу

- •14.Внешняя организация и временные диаграммы динамических зу.

- •15.Постоянные Запоминающие Устройства пзу.

- •16.Однократно (электрически) программируемые пзу.

- •17.Репрограммируемые пзу.

- •22.Структура элементарного микропроцессора.

- •24.Функционирование микропроцессорной системы

- •26.Микропроцессор

- •27.Обработка микропроцессором требования прерывания.

- •28.Прерывание с программным опросом.

- •29.Векторная система прерываний.

- •30.Структура приоритетов.

- •31.Синхронизация микропроцессорной системы.

- •32.Программирование микропроцессоров.

- •33.Архитектурные особенности современных микропроцессоров.

- •34.Иерархическая структура памяти.

- •36. Архитектурно независимая спецификация программ.

- •38.Универсальные микропроцессоры.

- •39.Микропроцессор с архитектурой х86.

- •45.Структурная схема базовой модели микропроцессора семейства х86

- •46.Однокристальные микро эвм (микроконтроллеры).

7.Структура 2d.

В ней запоминающие

элементы организованы в прямоугольной

матрице размерности

![]() ,

,

где М – обозначает информационную ёмкость памяти в битах;

Рис.7 Структура 2D

Дешифратор ДШ

адресного кода, при наличии разрешающего

сигнала

![]() –

сигнала выбора микросхемы активизирует

одну из выходных линий выборки строки,

разрешая одновременный доступ ко всем

элементам выбранной строки, хранящее

слово, адрес которого соответствует

номеру строки.

–

сигнала выбора микросхемы активизирует

одну из выходных линий выборки строки,

разрешая одновременный доступ ко всем

элементам выбранной строки, хранящее

слово, адрес которого соответствует

номеру строки.

Элементы одного столбца соединены вертикальной линией данных – это разрядная линия или линия записи/считывания. Элементы столбца, таким образом, хранят одноименные биты всех слов. Направление обмена в общем случае определяется усилителями записи/чтения под воздействием сигнала W/R.

Структура 2D применяется в микропроцессорных системах с малой информационной ёмкостью, так как при увеличении ёмкости дешифратор адреса существенно усложняется.

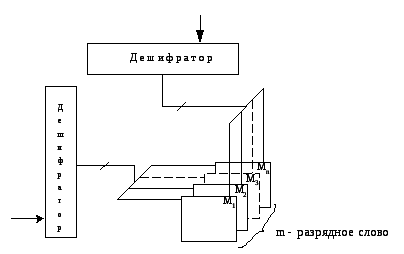

8.Структура 3d

Структура 3D (одноразрядная организация) позволяет упростить ДШ адреса с помощью двухкоординатной выборки ЗЭ. Принцип двухкоординатной выборки рассматривается на примере ПЗУ, которая реализует только оперативное чтение данных. Здесь, в 3D, код разряда n делится на две половины, которые декодируются отдельно и выбирается ЗЭ, находящийся на пересечении активных линий выходов обоих дешифраторов.

Рис.8 Структура 3D

На пересечении

DCx

и DCy

выбирают

ЗЭ

![]() .

Суммарное число выходов обоих ДШ будет

.

Суммарное число выходов обоих ДШ будет

![]() ,

что меньше

,

что меньше

![]() .

Например, для ЗУ небольшой ёмкости: 1К

слов структура 2D потребовала бы ДШ с

1024 выходами, а структура 3D нужны всего

два ДШ с 32 выходами каждый.

.

Например, для ЗУ небольшой ёмкости: 1К

слов структура 2D потребовала бы ДШ с

1024 выходами, а структура 3D нужны всего

два ДШ с 32 выходами каждый.

При многоразрядной организации ЗУ со структурой типа 3D она приобретает трёхмерный характер.

Рис.9 Трёхмерный характер структуры 3D

В этом случае несколько матриц управляются от двух ДШ, относительно которых они включены параллельно и каждая матрица выдаёт 1 бит или 1 разряд адресного слова. Число матриц должно быть равно числу разрядов хранимых слов.

9.В структурах типа 2DM сочетаются достоинства структур 2D и 3D, т.е. упрощается дешифрация адреса и не требуются ЗЭ с двухкоординатной выборкой.

Рис.10 Структура типа 2DM

Структура 2DM для матрицы ЗЭ с адресацией от дешифратора DCx имеет характер структур 2D, т.е. возбуждённый выход ДШ DCx выбирает целую строку. Однако, в отличии от структуры 2D длина строки не равна разрядности хранимых слов, а многократно её превышает. При этом число строк уменьшается, т.е. уменьшается число выходов ДШ.

Для выбора одной

из строк служат не все разряды адресного

кода, а их часть А1

, остальные

разряды от

используются, чтобы выбрать необходимое

слово из того множества слов, которое

содержится в строке. Это выполняется с

помощью мультиплексоров на адресные

входы которых подаются коды А2.

используются, чтобы выбрать необходимое

слово из того множества слов, которое

содержится в строке. Это выполняется с

помощью мультиплексоров на адресные

входы которых подаются коды А2.

Длина строки равна

![]() ,

где m –

разрядность хранимых слов. Из каждого

отрезка строки длиной 2k

максимально

выбирается 1 бит. На выходах MUX формируется

слово. По разрешению сигнала CS, поступающего

на выходы ОЕ,

(управляемых буферов с тремя состояниями)

выходное слово передаётся на внешнюю

шину данной микропроцессорной системы.

,

где m –

разрядность хранимых слов. Из каждого

отрезка строки длиной 2k

максимально

выбирается 1 бит. На выходах MUX формируется

слово. По разрешению сигнала CS, поступающего

на выходы ОЕ,

(управляемых буферов с тремя состояниями)

выходное слово передаётся на внешнюю

шину данной микропроцессорной системы.

Структура 2DM для ОЗУ с операциями чтения/запись, в общем виде, может быть представлена следующим рисунком:

Рис.11 Структура 2DM

10.Использование ОЗУ

В общем случае организация ОЗУ может быть представлена таблицей, содержащей адреса и содержимое

|

Адрес |

Содержимое |

|||||||

|

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

Слово 0 |

|

|

|

|

|

|

|

|

|

Слово 1 |

|

|

|

|

|

|

|

|

|

Слово 2 |

|

|

|

|

|

|

|

|

|

Слово 3 |

|

|

|

|

|

|

|

|

|

Слово 4 |

|

|

|

|

|

|

|

|

|

Слово 5 |

|

|

|

|

|

|

|

|

|

Слово 6 |

|

|

|

|

|

|

|

|

|

Слово 7 |

|

|

|

|

|

|

|

|

|

Слово 8 |

|

|

|

|

|

|

|

|

|

Слово 9 |

|

|

|

|

|

|

|

|

|

Слово 10 |

|

|

|

|

|

|

|

|

|

Слово 11 |

|

|

|

|

|

|

|

|

|

Слово 12 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

Слово 13 |

|

|

|

|

|

|

|

|

|

Слово 14 |

|

|

|

|

|

|

|

|

|

Слово 15 |

|

|

|

|

|

|

|

|

Рассмотрим логическую схему ОЗУ, организация которой представляется этой схемой:

Рис.12 Логическая схема ОЗУ

Изображена схема ОЗУ с объёмом памяти 128 бит, которая выполняет операцию записи поступающих данных.

На входе данных

поступает слово 01010101 для записи в память.

Положение слова определяется кодом

1100 (12), поступающим на адресные входы.

Затем две команды управления![]() CS

и WE (активизация записи) должны быть

установлены в состояние 0 (ноль), чтобы

выполнить операцию записи.

CS

и WE (активизация записи) должны быть

установлены в состояние 0 (ноль), чтобы

выполнить операцию записи.

ОЗУ находится в

состоянии записи, когда обе линии

управления CS и WE находятся в нулевом

состоянии. В ходе операции записи 8 бит

данных на выходе D0

– D7

записывается

в восьмиразрядную ячейку, на которую

указывает адрес и в течении этого времени

выхода Q0

– Q7

держится

в высоком состоянии. Когда выходы

находятся в состоянии

![]() ,

а

,

а

![]() ,

ОЗУ переходит в состояние считывания

из него данных.

,

ОЗУ переходит в состояние считывания

из него данных.

В ходе считывания инверсное значение слова данных, на которое указывают адресные входы, появляется на выходе Q0 – Q7. Операция считывание не разрушает данных, расположенных в ОЗУ.

В состоянии

ожидания все выходы переходят к высокому

уровню и никакие данные не проходят

через входы![]() .

Это можно проиллюстрировать таблицей

истинности.

.

Это можно проиллюстрировать таблицей

истинности.

|

Состояние |

Входы управления |

Выходы |

|

|

|

|

||

|

Запись |

0 |

0 |

Состояние "1" |

|

Считывание |

0 |

1 |

Инверсия размещённых данных |

|

Режим ожидания |

1 |

* – не меняет знак |

Состояние "1" |

Оперативные ЗУ

По принципу хранения информации в ЗУ и способу управления ими все большие интегральные схема БИС ОЗУ подразделяются на статические и динамические.

В статических ОЗУ хранение информации в ЗЭ (триггерах) осуществляется постоянным источником питания и требует в общей сложности от 4–х до 6–ти транзисторов для хранения одного бита информации.

В динамических ОЗУ информация хранится в виде накопленных электрических зарядов на паразитных ёмкостях диодов или транзисторов, а регенерация зарядов (восстановление информации) происходит периодически во время действия периодических синхронизированных сигналов. За то объём оборудования (число транзисторов на 1 бит) в данном ОЗУ уменьшается в 4 раза по сравнению со статическим ОЗУ.