- •1.Общая структура эвм

- •2.Общая архитектура микропроцессора

- •3.Работа микроЭвм.

- •4.Полупроводниковая память и её использование в микропроцессорной технике.

- •5.Эксплуатационные параметры зу.

- •6.Режимные параметры зу

- •7.Структура 2d.

- •8.Структура 3d

- •11.Статическая память (sram)

- •12.Зэ динамические зу

- •14.Внешняя организация и временные диаграммы динамических зу.

- •15.Постоянные Запоминающие Устройства пзу.

- •16.Однократно (электрически) программируемые пзу.

- •17.Репрограммируемые пзу.

- •22.Структура элементарного микропроцессора.

- •24.Функционирование микропроцессорной системы

- •26.Микропроцессор

- •27.Обработка микропроцессором требования прерывания.

- •28.Прерывание с программным опросом.

- •29.Векторная система прерываний.

- •30.Структура приоритетов.

- •31.Синхронизация микропроцессорной системы.

- •32.Программирование микропроцессоров.

- •33.Архитектурные особенности современных микропроцессоров.

- •34.Иерархическая структура памяти.

- •36. Архитектурно независимая спецификация программ.

- •38.Универсальные микропроцессоры.

- •39.Микропроцессор с архитектурой х86.

- •45.Структурная схема базовой модели микропроцессора семейства х86

- •46.Однокристальные микро эвм (микроконтроллеры).

45.Структурная схема базовой модели микропроцессора семейства х86

и его клонов.

Рис.39.

Условно структурную схему базовой модели можно разделить на две части:

– исполнительный блок (нижняя часть)

– устройство сопряжения с системной магистралью.

В исполнительный блок входят:

Регистры общего назначения и арифметический блок, включающий нижнее арифметико-логическое устройство, регистры промежуточного хранения и регистр флагов.

Восемь регистров исполнительного блока:

![]() имеют длину машинного слова (16 или 32

разряда) и делятся на две группы:

имеют длину машинного слова (16 или 32

разряда) и делятся на две группы:

![]() регистры

общего назначения

регистры

общего назначения

![]() адресные

регистры.

адресные

регистры.

Регистры общего назначения передают регистровые пары по половине машинного слова.

Регистр А (АХ) – аккумулятор (накапливающий регистр)

Регистр B – это регистр базы, от которого может отсчитываться адрес

Регистр C – это счётчик

В регистре D хранятся данные длинной в одно машинное слово.

Деление регистров общего назначения пополам (Hi, Low) позволяет использовать каждую из них (половин) самостоятельно, в виде короткого регистра, т.е. к каждой половинке этого регистра можно адресоваться отдельно, что не исключает адресации к каждой паре. Названия этих регистров не ограничивают их применение, что и указывается в их названии, они говорят лишь об наиболее частом их использовании, тем не менее, их применяют и для других целей (адресов).

Регистры адресной группы

![]() ,

число которых в последних моделях Х86

возросло, используется по их прямому

функциональному назначению (для

адресации) и в других целях эти регистры

не применяются.

,

число которых в последних моделях Х86

возросло, используется по их прямому

функциональному назначению (для

адресации) и в других целях эти регистры

не применяются.

Основное назначение адресного регистра – хранить числовые значения, реализованные при формировании адресов операндов.

Устройство сопряжения с системной магистралью содержит:

Управляющие регистры, конвейер команд, арифметико-логические устройства команд (верхнее), устройство управления исполнительным блоком микропроцессора, интерфейс памяти, назначение которого соединить внешнюю магистраль микропроцессора с системной магистралью вычислительной системы.

Управляющие регистры

![]() содержат информацию, определяющую

физические адреса операндов и команд.

содержат информацию, определяющую

физические адреса операндов и команд.

Регистр IP является указателем адреса команды, который будет выбираться в конвейер команд в качестве очередной команды. Конвейер команд микропроцессора хранит несколько команд, что позволяет совместить подготовку очередной команды с выполнением команды текущей.

Регистр флагов можно отнести к управляющим регистрам. Каждый его разряд имеет строго определённое назначение, и в зависимости от полученного в нижнем арифметико-логическом устройстве результата, разряды регистров флагов устанавливаются аппаратно (независимо от программиста, выполняемой программы). Например, нулевой результат, отрицательное число, перенос, переполнение разрядной сетки арифметико-логического устройства, попытка деления на нуль и т.д. Некоторые разряды регистров флагов могут устанавливаться специальными командами.

Основные тенденции развития управления микропроцессоров.

Общие современные тенденции развития универсальных микропроцессоров следующие:

– повышение тактовой частоты;

– увеличение объёма хранимой информации и пропускной способности устройств памяти;

– увеличение количества параллельно функционирующих исполнительных устройств.

Совокупная реализация в одном кристалле микропроцессора рекордных значений по всем трём тенденциям невозможна из-за фундаментальных физических ограничений, ограничений технического характера, ограничений на стоимость, как микропроцессорного производства, так и ограничений на стоимость микропроцессорных систем в целом. Поэтому сегодня каждый тип микропроцессора является результатом многих компромиссов, принимаемых его создателями.

Рассмотрим все три основные тенденции и суть принципиальных компромиссов.

– Повышение тактовой частоты – его добиваются, прежде всего, за счёт использования более современного и более дорогого технологического процесса – это использование современных транзисторов (более быстродействующих); увеличение числа слоёв металлизации; более совершенная схемотехника (меньшей каскадности); более плотная компоновка функциональных блоков в кристалле, в частности, почти все производители микропроцессоров перешли на технологию КМОП.

Биполярные схемы (транзисторно-транзисторной логики) на сегодня имеют одинаковые показатели по энерговыделению, однако, схемы КМОП оказались более технологичными, по сравнению со схемами транзисторно-транзисторной логики.

Увеличивает быстродействие микропроцессоров и снижает выделяемую ими тепловую энергию, снижение питания с 5 до 3-х, 2-х и ниже вольт.

Использующиеся в настоящее время технологии простираются от 0,35, 0,25, 0,18, 0,13, 0,09, 0,07 мкм технологии.

Увеличение числа слоёв металлизации уменьшает длину между соединениями на кристалле, что позволяет увеличить частоту на кристалле и снизить выделяемую мощность.

Увеличение пропускной способности памяти включают создание КЭШ памяти нескольких уровней, от 1-го до 3-х и 4-х; увеличение пропускной способности между КЭШ памятью и процессором (увеличение частоты работы шины и её ширины); введение дополнительных шин, расшивающих конфликты между процессором, основной и КЭШ памятью. При введении дополнительных шин одна работает на частоте процессора с КЭШ памятью процессора, вторая на наиболее низкой частоте работы основной памяти.

Тенденция увеличения КЭШ памяти реализуется по-разному:

-

Использование внешних КЭШ памяти команд и данных объёмом 2 Мбайта и более с временем доступа в 2 такта микропроцессора;

-

Использование отдельного кристалла (микросхемы) КЭШ памяти второго уровня, который размещается непосредственно в одном корпусе с микропроцессором.

-

Размещение в кристалле микропроцессора отдельных КЭШ памяти команд и данных первого уровня, объёмом в несколько Кбайт и общей КЭШ памятью для команд и данных второго уровня, объёмом в сотни Кбайт. Наиболее реализуемым решением является размещение на кристалле отдельных КЭШ памяти первого уровня для команд и данных с возможным созданием в некристалльной КЭШ памяти второго уровня. КЭШ память первого уровня работает на тактовой частоте микропроцессора, а КЭШ память второго уровня работает на половине этой частоты. Микропроцессоры P-VII имеют внутреннюю КЭШ память от 1,5 Мбайт и выше.

-

Повышение степени внутреннего параллелизма. Каждое новое поколение микропроцессоров имеет увеличенное количество функциональных исполнительных устройств и улучшение их функциональных и временных характеристик. В настоящее время микропроцессоры выполняют не менее шести операций за такт.

Следует отметить, что количество операций с плавающей точкой, одновременно выполняемых конвейером, не превышает четырёх, а чаще двух.

Для загрузки функциональных исполнительных устройств микропроцессора используются такие процедуры, как переименование регистров и предсказание переходов.

В архитектурах современных микропроцессоров разной производительности много общего, что ставит вопрос об унификации архитектур микропроцессоров. Возможность формирования большого числа транзисторов в одном кристалле позволяет использовать все известные приёмы повышения его производительности. Наибольшие шансы на дальнейшее развитие имеют Х86 и Alpha корпорации DEC. Это объясняется тем, что процессоры с архитектурой Х86 выпускаются несколькими независимыми производителями. За счёт введения в эту архитектуру ядра с сокращённым набором команд, архитектура Х86 преодолела отставание в производительности от чистых RISC процессоров. Такой подход позволил перейти к процессорам со многими системами команд, каждая из которых транслируется внутрикристальным (аппаратным) транслятором в набор операций RISC ядра процессора. Возможно введение программной логики, настроенной на требуемую систему команд, но выполняемой аппаратно. Микропроцессоры серии Alpha корпорации DEC, архитектуру которых имеют и другие фирмы, отличаются решением проблемы переносимости программного обеспечения для архитектур Х86. Это делается посредством оптимизирующего транслятора, который преобразовывает используемый код архитектуры Х86 в оптимизированный исполняемый код архитектуры Alpha. Такой подход пытаются применять и другие фирмы, с целью совместимости своих архитектур с другими архитектурами.

Система команд универсального микропроцессора.

Основной принцип построения компьютера, сформированный Джоном Фон Нейманом, заключается в том, что работой ЭВМ управляет программа, состоящая из отдельных команд или инструкций. Программа вместе с данными хранится в основной памяти компьютера, причём каждая команда программы хранится в отдельной ячейке или группе смежных ячеек и имеет свой адрес.

Все команды имеют одинаковую структуру, т.е. состоят из двух частей:

– операционной (код операции)

– адресной (код операнда)

Код операции – определяет, какую команду надо выполнить;

Адресная часть – указывает, где хранятся операнды (обработанные данные) и куда поместить результат выполнения операции.

По количеству используемых в команде операндов различают одно, двух, трёх, четырёх адресные и безадресные команды.

В одноадресной команде указывается, где находится один из двух обрабатываемых операндов. Второй операнд должен быть помещён в арифметико-логическое устройство заранее (в аккумулятор).

В двухадресной команде оба операнда находятся в памяти, поэтому в команде указываются оба их адреса. Результат выполнения команды засылается в один из этих адресов, старый операнд теряется.

В трёхадресной команде два адреса указывают на исходные данные, а третий указывает, куда необходимо поместить результат.

В четырёхадресной команде три адреса используются для указания исходных операндов и места размещения операндов, четвёртый указывает адрес следующей команды.

В безадресных командах обрабатывается один операнд, который и до и после выполнения команды находится в арифметико-логическом устройстве, т.е. не пересылается в основную память.

Безадресные команды используются для выполнения служебных операций, например: очистка экрана, блокировка клавиатуры, снятие блокировки и т.д.

Все команды программы выполняются последовательно, в порядке их хранения в основной памяти компьютера (естественный порядок следования команд) такой порядок характерен для линейных программ.

Для организации ветвлений, цикличного выполнения отдельных участков программы, имеются специальные команды, нарушающие естественный порядок, безусловная передача управления, условная передача управления.

Условная передача – переход, выполняющийся в случае определённого условия. Обращение к подпрограмме (переход с возвратом) и циклические операции. При использовании 4-х адресных команд, как следствие из логики их организации, также естественный порядок следования команд не соблюдается. Явное указание адреса следующей команды при использовании 4-х адресных команд возможно только в случае, если программа размещается в доступной процессору области памяти. Так как с точки зрения процессора команды ничем не отличаются от данных, поэтому в процессе выполнения команды могут микропроцессором изменяться (модифицироваться), что повышает гибкость программирования и вычислительных машин. Семейство Х86 потому так и называется, что от микропроцессора Intel 8086 до последних модификаций обязательно содержит базовую систему команд, которая является ничем иным, как существенно расширяемая система команд Intel 8086 и Intel 80286.

Расширение системы команд касается увеличения разрядности адресов и операндов, более гибкой системой адресации, появление принципиально новых типов данных, например, битовые строки и поля и появление новых команд.

Команды содержат одно- или двухбайтовый код инструкций, за которыми могут следовать несколько байт, определяющих режим использования команды, и операнда. Последних может быть до трёх или не одного. Результат выполнения команды записывается в место, предопределённое инструкцией или в место, заданное операндом назначения.

В базовую систему команд семейства Х86 входят следующие группы команд:

1. Команды пересылки данных (в том числе внутри микропроцессора) и команды ввода/вывода.

2. Арифметические

команды – основные (![]() )

и дополнительные: инкремент (увеличение

на 1), декремент (уменьшение на 1).

)

и дополнительные: инкремент (увеличение

на 1), декремент (уменьшение на 1).

3. Логические

команды: конъюнкция (![]() ),

дизъюнкция (

),

дизъюнкция (![]() ),

отрицание, сдвиг и другие.

),

отрицание, сдвиг и другие.

4. Команды обработки строковых данных: пересылка, сравнение, сканирование, слияние и разделение строк.

5. Команды передачи управления: безусловный переход (go to), условный переход (в случае выполнения или невыполнения условия), прерывание и переход с возвратом.

6. Команды управления: нет операций; внешняя синхронизация.

Каждая команда из системы команд микропроцессора имеет большое число модификаций, которые определяются чаще всего режимом адресации операндов. Операнды могут быть трёх типов: регистровый, непосредственный, операнд в памяти.

Регистровые операнды указываются именами используемых регистров микропроцессора.

Непосредственные операнды всегда числовые, представляются различными системами счисления. Микропроцессор различает систему счисления по последнему символу/букве, сопровождающей число:

Операнды в памяти

могут указываться также с помощью

регистров, символичными именами и

константами (![]() ).

Комбинации этих элементов команде

называются способами адресации. Например,

команда MOV

может иметь следующие способы адресации:

).

Комбинации этих элементов команде

называются способами адресации. Например,

команда MOV

может иметь следующие способы адресации:

|

mov |

r, r |

|

mov |

m, r |

|

mov |

r, imed |

|

mov |

m, sr |

r – регистр общего назначения микропроцессора;

m – адрес ячейки памяти;

imed – число, использующееся в качестве объекта (операнд);

sr – сегментный регистр.

При использовании

операндов памяти указание на физический

адрес ОЗУ может производиться

непосредственно, косвенно или со

смещением. При неполной адресации

исполнительный адрес указывается в

виде 16-тиричного числа, однозначно

определяющего ячейку внутри заданного

сегмента памяти или в виде символьного

имени. Если адресуется ячейка текущего

сегмента, то имя сегмента в адресной

части команды не указывается. Это связано

с режимом умолчания. Текущим по умолчанию

для адреса команды является регистр

![]() .

Для адресации ячейки в стековом сегменте

служит регистр

.

Для адресации ячейки в стековом сегменте

служит регистр

![]() .

Для адресации данных служит регистр

.

Для адресации данных служит регистр

![]() .

.

Только если адрес ОЗУ не указывается в

сегментных регистрах или относится к

сегменту, указанному в адресном регистре,

его имя необходимо указывать в другой

команде. При косвенной адресации

используемый адрес ОЗУ хранится в одном

из регистров микропроцессора, а в команде

указывается имя этого регистра. При

этом имя регистра заключается в квадратные

скобки. Например,

![]()

![]() .

.

В зависимости от используемых регистров и способов их использования косвенная адресация имеет несколько разновидностей: базовую, индексную, базово-индексную.

Базовая адресация.

Программу можно писать в абсолютных адресах кода. Сам программист определяет, в каких ячейках памяти она должна размещаться для использования; а в относительных адресах, когда заранее неизвестно, в какую часть памяти попадёт программа при загрузке.

В первом случае (абсолютных адресах) программа готова к использованию, но она не является перемещаемой.

Во втором случае (относительная адресация) программа перед выполнением должна быть привязана к своему месту в памяти, поскольку она пишется так, как будто обязательно попадает в область памяти, начиная с ячейки ноль. Перед загрузкой такой программы операционная система ищет свободную область в памяти, и адрес первой ячейки этой области заполняется, как общая добавка ко всем адресам в программе. Этот адрес называется базовым или базой. Абсолютные же адреса определяются сложением с базовым адресов относительных. В семействах микропроцессоров Х86 базовая адресация реализуется использованием регистров BX (регистр базы) или регистра BP (указатель точки).

Индексная адресация.

Применяется, когда надо осуществлять

перебор элементов какого-либо набора

данных (массива). Например, если элемент

данных имеет длину 1 байт, то при переходе

от первого элемента к другому, адрес

должен меняться на единицу. Если же

длина элемента данных набора данных

(массива) равна 3 байтам, то при переходе

от одного элемента к другому адрес

должен меняться на три. Начальный адрес

массива является его константой, а адрес

конкретного элемента массива вычисляется

суммированием начального адреса и

индекса i: (начальный

адрес + i). Для хранения

индексов микропроцессор имеет 2 индексных

регистра

![]() и

и

![]() .

Используются также комбинационные

системы адресации: базово-индексная,

базовая со смещением, индексная со

смещением.

.

Используются также комбинационные

системы адресации: базово-индексная,

базовая со смещением, индексная со

смещением.

Например, базово-индексная адресация

в команде будет иметь следующий вид:

![]() .

.

Взаимодействие элементов при работе микропроцессора.

История 32-хразрядных микропроцессоров началась с Intel 80386, который вобрал в себя все свойства 16-тиразрядных предшественников, в частности, Intel 8086 и Intel 8088, а также микропроцессора Intel 80286. Целью этого было обеспечение совместимости новых микропроцессоров с уже существовавшем программным обеспечением для предшественников. Процессоры стали иметь поддержку виртуальной памяти объёмом до 64 Тбайт. Встроенный блок управления памятью обладал способностью поддерживать механизм сегментации и страничной трансляции адресов (средство организации виртуальной памяти с подкачкой страниц по запросу).

В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация оперирует с памятью, как с набором страниц одинакового размера.

В первых 32-хразрядных микропроцессорах Intel 80386 размер страницы составлял 4 Кбайт. Начиная с микропроцессоров класса Pentium, появляется возможность увеличения размера страниц до 4 Мбайт. При этом сохраняется возможность одновременной работы с использованием страниц размером 4 Кбайт.

Система команд, выпускавшихся позднее микропроцессоров, хотя и расширялась, на расширение шло при сохранении всех команд микропроцессоров Intel 8086 и Intel 80286.

Процессоры семейства Х86 могут работать в одном из двух основных режимах, при этом быстро переключаться из одного в другой: это реальный и защитный режимы.

Реальный получил своё название от Real Address Mode (режим реальной адресации) полностью совместим с режимом работы микропроцессоров Intel 8086. В этом режиме возможна адресация физической памяти до 1 Мбайт.

Защищённый режим (защищённый режим виртуальной адресации) является основным режимом работы 32-хразрядных микропроцессоров. В этом режиме процессор позволяет адресовать до 4 Гбайт физической памяти. В процессор Pentium – VI – до 64 Гбайт, через которую при использовании механизма страничной адресации могут отображаться до 64 Тбайт виртуальной памяти.

Защищённый режим виртуальной адресации предназначен для обеспечения независимости выполнения нескольких задач, т.е. сущность его – защита ресурсов одной задачи от возможного возникновения другой. Основной защищённый ресурс – память, а защита основана на сегментации.

Отметим существование в современных микропроцессорах 2 дополнительных режима:

-

Режим виртуального процессора Intel 8086. Это особое состояние, в котором процессор функционирует, как процессор Intel 8086. Смысл этого режима заключается в том, что на одном реальном процессоре в одном режиме могут как бы параллельно исполняться несколько задач с изолированными друг от друга ресурсами. При этом использование физического адресного пространства памяти управляется механизмами сегментации и трансляции (подкачки) страниц.

-

Режим был реализован, начиная с процессоров Pentium. Его имели также некоторые процессоры Intel 80486. Его называют особым режимом системы управления (SMМ). При этом режиме микропроцессор выходит в иное, изолированное от остальных режимов, пространство памяти. Этот режим используют в целях отладки программ.

32-хразрядные микропроцессоры поддерживают (используют в качестве операндов) знаковые и беззнаковые числа, строки байтов, цифры символов, битовые поля и битовые строки, указатели и числа с плавающей точкой.

Бит – единица информации. В памяти микропроцессорной системы задаётся базой и смещением. При этом:

– база – адрес слова;

– смещение – номер бита в слове;

– битовое поле – группа до 32-х смежных битов, располагающихся не более, чем в 4-х байтах;

– битовая строка – набор смежных битов, длиной до 4 Гбит.

Байт – группа из 8-ми бит числа без знака:

![]()

Целые числа со знаком: байт, слово, двойное слово, учетверённое слово отличаются от целых чисел без знака тем, что единичное значение (уровень логической единицы) самого старшего бита является признаком отрицательного числа, которое хранится в памяти в дополнительном коде.

Действительные числа в формате с плавающей точкой. В современных микропроцессорах такие числа обрабатываются для ускорения процесса обработки специальными аппаратными сопроцессорами (FPU) чисел с плавающей точкой. Они делятся на:

Числа одинаковой точности (32 бита), из которых 8 бит – порядок, остальные под мантиссу.

Числа двоичной точности (64 бита), из которых 11 бит – порядок, остальные под мантиссу.

Числа повышенной точности (80 бит), из которых 15 бит – порядок, остальные под мантиссу.

Двоично-десятеричные числа (BCD) могут быть 8-миразрядными упакованными, содержат два десятичных разряда в одном байте.

8-миразрядные, неупакованные содержат один десятичный разряд в байте.

80-тиразрядные, упакованные (двоичные) могут обрабатываться только сопроцессором.

Строки байт, слов и двоичных слов.

Указатели подразделяются на виды:

Длинный указатель состоит из 48 бит, из которых 16 бит селектор сегмента, 32 бита – смещение.

Короткий указатель (32 бита) 32-хбитное смещение.

Указатель (32 бита) содержит 16-бит селектор сегмента и 16-тибитное смещение. Является единственным типом указателя для микропроцессоров Intel 8086 и Intel 80286.

Процессоры типа ММХ могут обрабатывать и другие типы упакованных 64-хбитных данных.

16-тиразрядные процессоры не поддерживают учетверённые слова всех типов, битовые поля и строки, строки двойных слов, короткие и длинные указатели.

В семействе микропроцессоров Х86 принято, что слова записываются в двоичных смежных байтах памяти, начиная с младшего. Таким образом, адресом слова является адрес его младшего байта. Двоичные слова записываются в четырёх смежных байтах. При этом адрес младшего байта – есть адрес вторичного слова.

Работой

микропроцессора управляет находящаяся

в ОЗУ программа. Адрес же очередной

команды хранится в счётчике команд (![]() )

и в одном из сегментных регистров, чаще

всего в регистре

)

и в одном из сегментных регистров, чаще

всего в регистре

![]() .

Каждый из них в реальном режиме имеет

длину 16 разрядов, тогда как физический

адрес ОЗУ должен иметь длину 20 бит.

Несогласованность длины машинного

адреса (16 бит) и длины физической памяти

(20 бит) приводит к тому, что физический

адрес необходимо формировать из данных

разных регистров микропроцессора в

процессе работы. В реальном режиме вся

память ОЗУ делится на сегменты длиной

64 Кбайт. Адрес состоит из двух частей:

(номер) база сегмента памяти; номер

ячейки внутри данного сегмента. Номер

сегмента, как и смещение, имеет длину

16 разрядов. При вычислении физического

адреса памяти сегмент и смещение

суммируются, но сегмент перед суммированием

смещается влево на 4 разряда. В результате

суммирования образуется физический

адрес памяти длиной 20 бит. В защищённом

режиме базовые адреса сегментов хранятся

в дескрипторных таблицах и имеют длину

24 или 32 бита, в зависимости от типа

микропроцессора. В сегментных же

регистрах хранится селектор, содержащий

номер дескрипторной таблицы и дескрипторное

смещение, т.е. порядковый номер дескриптора,

в котором и хранится базовый номер

дескриптора.

.

Каждый из них в реальном режиме имеет

длину 16 разрядов, тогда как физический

адрес ОЗУ должен иметь длину 20 бит.

Несогласованность длины машинного

адреса (16 бит) и длины физической памяти

(20 бит) приводит к тому, что физический

адрес необходимо формировать из данных

разных регистров микропроцессора в

процессе работы. В реальном режиме вся

память ОЗУ делится на сегменты длиной

64 Кбайт. Адрес состоит из двух частей:

(номер) база сегмента памяти; номер

ячейки внутри данного сегмента. Номер

сегмента, как и смещение, имеет длину

16 разрядов. При вычислении физического

адреса памяти сегмент и смещение

суммируются, но сегмент перед суммированием

смещается влево на 4 разряда. В результате

суммирования образуется физический

адрес памяти длиной 20 бит. В защищённом

режиме базовые адреса сегментов хранятся

в дескрипторных таблицах и имеют длину

24 или 32 бита, в зависимости от типа

микропроцессора. В сегментных же

регистрах хранится селектор, содержащий

номер дескрипторной таблицы и дескрипторное

смещение, т.е. порядковый номер дескриптора,

в котором и хранится базовый номер

дескриптора.

Рис.40

Физический адрес очередной команды через внутреннюю магистраль микропроцессора и интерфейс памяти поступает на шину адреса системной магистрали микропроцессорной системы. Одновременно из устройства управления исполнительного блока на шину управления выдаётся управляющий сигнал в память, который заставляет выбрать содержимое, находящееся по адресу, указанному на адресной шине системной магистрали. Это содержимое и есть очередная команда программы, которая поступает через шину данных системной магистрали, интерфейс памяти и внутреннюю магистраль микропроцессора на регистр команд. В регистре команд (INST) из команды выделяется код операции, который поступает в устройство управления исполнительного блока микропроцессора для выработки управляющих сигналов, настраивающих микропроцессор на выполнение требуемой операции. В зависимости от используемого, в команде режима адресации организуется выборка исходных данных.

Управление внешними устройствами микропроцессорных систем.

Принцип управления внешним устройством.

Микропроцессоры и основная память образуют ядро микропроцессорной системы, но для выполнения своих функций ядро дополняется внешними устройствами: внешними запоминающими устройствами ВЗУ и устройствами ввода/вывода информации УВВ. Передача информации из внешнего устройства в микропроцессорную систему называется операцией ввода, а передача из микропроцессорного устройства во внешние – операция вывода.

Эффективность системы определяется не только возможностями процессора и характеристиками запоминающего устройства, но и составом внешних устройств, их технологическими данными, способами организации их совместной работы с микропроцессорами.

Первый шаг в совершенствовании структуры вычислительных систем с целью повышения производительности был сделан при разработке II-го поколения ЭВМ. В них была обеспечена автономность работы внешних устройств. Она потребовала согласия работы внешних устройств и ЭВМ, проверок исправности устройств, при каждом обращении к ним. Появилась и определённая технология обращения к автономным внешним устройствам под названием интерфейс.

Когда эта технология была унифицирована, появилось понятие стандартного интерфейса, затем появилась концепция виртуальных устройств, позволяющая совмещать различные типы микропроцессоров и операционные системы, т.е. стало возможно использовать соответствующее программное обеспечение при физическом отсутствии необходимых устройств.

При разработке ЭВМ V-го поколения, в ЭВМ закладывается интеллектуализация общения, в частности: речевой ввод и вывод, графический ввод текстовой информации без клавиатуры и общение на различных естественных языках.

В общем случае для организации и проведения обмена данными между цифровыми устройствами, требуются специальные средства, их выделяют в отдельный класс:

-

Управляющие сигналы

-

Устройства сопряжения

-

Линии связи

-

Программы, реализующие обмен (драйверы)

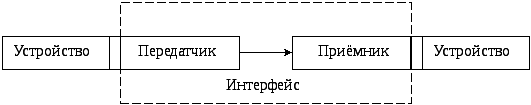

Комплекс линий и шин электрических сигналов электронных схем, алгоритмов и программ, предназначенных для обмена информацией, называется интерфейсом. В зависимости от типа соединяемых устройств различают:

-

Внутренний интерфейс микропроцессорной системы, например, интерфейс системной шины или интерфейс с накоплением на магнитном носителе. Они предназначены для сопряжения устройств с системным блоком.

-

Интерфейс межмашинного обмена преобразования сетей ЭВМ.

-

Человеко-машинный интерфейс (MMI).

Каждый интерфейс характеризуется наличием специальной аппаратной части

Рис.41

Использование аппаратной части определяется технологией обмена, установленным церемониалом, идеологией интеллекта, протоколом общения.

Особое место среди интерфейсов занимает человеко-машинный интерфейс, появился даже термин "дружественный пользователь", который обеспечивается, как техническими программными средствами, так и технологией общения.

Интерфейсы по технологии обмена подразделяют на параллельные и последовательные.

Параллельным называется интерфейс, обеспечивающий обмен одновременно всеми разрядами передаваемой информационной единицы. Чаще всего бита или машинного слова.

Параллельным и последовательно-параллельным всегда делается внутренний интерфейс микропроцессорной системы. При последовательно-параллельном интерфейсе одновременно передаётся только часть информации, например, 1 байт 4-хбайтного слова, а все её части передаются последовательно.

Последовательным называется интерфейс, обеспечивающий обмен информацией последовательно по 1 биту. Такой обмен обычно осуществляется между микропроцессорными системами (межмашинный обмен).

При параллельном и последовательно-параллельном интерфейсе участники обмена информацией связываются друг с другом многожильным кабелем, число жил которого должно быть не меньше числа одновременно передаваемых битов.

При последовательном интерфейсе участники обмена связываются друг с другом одно или двухпроводной линией связи (вторая линия – общий провод). Как правило, это кабель на витой паре, коаксиальной (радиочастотной), световодный, инфракрасный канал и радиоканал.

Интерфейсы ввода/вывода принято делить на 2 уровня: физический и логический.

Рис.42

Физический уровень интерфейса – нижний (аппаратный), определяющий физические и электрические характеристики соединений, включая потери ввода/вывода, разъёма, кабелей, повторители электрических сигналов, усилителей и т.п. При необходимости, на этом уровне обеспечивается кодирование и модуляция сигналов, передаваемых по линии связи.

На логическом (программном) уровне используются символические имена внешних устройств (A, B, C, D), которые могут быть отображены пользователем на любое физическое устройство.

В зависимости от степени участия микропроцессора в обмене данными используются 3 способа управления обменом:

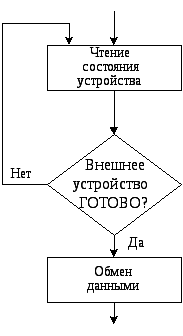

1. Асинхронный обмен, его называют режимом сканирования.

2. Синхронный обмен.

3. Прямой доступ к памяти.

Режим сканирования или асинхронный обмен используется для внутреннего интерфейса микропроцессорной системы, при этом микропроцессор опрашивает устройство, готово ли оно к обмену, если нет – продолжается опрос.

Рис.43

Режим сканирования управляет подготовкой к обмену, но имеет ряд недостатков:

-

В процедуре опроса микропроцессор не может выполнять другую работу.

-

Если внешнее устройство быстродействующее, микропроцессор, как программно - управляемое устройство, может не успевать организовывать обмен данными.

В синхронном режиме основную роль по организации обменом играет микропроцессор, однако, он не ждёт готовности устройства, а выполняет другую работу, когда возникает нужда в обмене, внешнее устройство, с помощью соответствующего прерывания, обращает на себя внимание микропроцессора.

Прямой доступ к памяти используется для очень быстрого обмена блоками данных (DMA). При этом микропроцессор освобождается от управления операциями ввода/вывода данных. В режиме прямого доступа к памяти используется специальное устройство, управляющее обменом – это контроллер прямого доступа к памяти, который перед началом обмена программируется с помощью центрального процессора микропроцессорной системы. При этом программируются в него передаваемые адреса основной памяти и количество передаваемых данных. Затем микропроцессор предоставляет возможность работать контроллеру прямого доступа к памяти и до окончания процедуры обмена не вмешивается в работу контроллера, а сам может выполнять другую работу.

Контроллер прямого доступа к памяти об окончании обмена по каналу прямого доступа сообщает микропроцессору, и микропроцессор подключается к шине данных, адресной шине, шине управления.

Таким образом, прямой доступ к памяти:

-

Освобождает процессор от управления операциями ввода/вывода.

-

Позволяет параллельно осуществлять обмен данными между внешним устройством и основной памятью.

-

Производить обмен данными со скоростью, ограниченной только пропускными способностями основной памяти и внешнего устройства.

Всё это увеличивает общую производительность микропроцессорной системы, даёт ей возможность более гибко приспосабливаться к работе в системах реального времени.

Организация прямого доступа к памяти.

При работе в режиме прямого доступа к памяти контроллер прямого доступа выполняет следующие функции:

-

принимает запрос от внешнего устройства на прямой доступ к памяти

-

формирует запрос микропроцессору на захват шин системной магистрали

-

принимает сигнал подтверждения микропроцессора о входе в состояние захвата (состояние z – третье состояние – высокоимпедансное состояние – ключи выходные полностью отключены от соответствующих шин), т.е. состояние отключения микропроцессора от системной магистрали

-

формирует сигнал сообщения внешнему устройству о начале выполнения циклов прямого доступа к памяти

-

выдаёт на адресную шину системной магистрали адрес ячейки памяти, предназначенной для обмена

-

вырабатывает сигналы управления обменом данными

-

по окончании прямого доступа к памяти, либо организует повторение цикла прямого доступа к памяти, либо прекращает режим прямого доступа, снимая запросы на него к микропроцессору.

Циклы прямого доступа к памяти выполняются с последовательно расположенными ячейками памяти, поэтому контроллер прямого доступа в память имеет счётчик числа переданных байт. Взаимодействие устройств микропроцессорной системы в режиме прямого доступа к памяти можно проиллюстрировать следующим рисунком.

Рис.44

Контроллеры прямого доступа микропроцессоров компании Intel совместимы снизу вверх, т.е. программы, использовавшие каналы прямого доступа более ранних микропроцессоров работают и на моделях более поздних.

Структурная схема контроллера прямого доступа к памяти.

Рис.45

Каждый канал состоит из четырёх 16-тиразрядных регистров (со 2-го по 5-й) и одного 6-тиразрядного регистра режима. Регистр текущего адреса хранит текущий адрес в ячейке памяти при выполнении цикла прямого доступа в память. После выполнения каждого цикла содержимое этого регистра увеличивается или уменьшается на единицу. Оно должно быть прочитано, т.е. введено в микропроцессор или загружено микропроцессором с помощью команд In или Out.

В режиме автоинициализации содержимое регистра текущего адреса при обновлении принимает базовый адрес из регистра хранения базового адреса. Регистр циклов прямого доступа к памяти хранит число слов, предназначенных для передачи. При выполнении циклов регистр работает в режиме вычитающего счётчика. Так как регистр 16-тиразрядный, при переходе из нулевого состояния, т.е. состояния 0000H в состояние FFFFH вырабатывается управляющий сигнал для блока управления контроллером. Регистр может быть прочитан командой In и в него можно осуществить запись командами Out или из микропроцессора или в режиме инициализации из регистра хранения базового числа циклов прямого доступа к памяти.

Регистры хранения базового адреса и хранения базового числа циклов предназначены для хранения постоянных базового адреса и базового числа циклов. Они загружаются в режиме программирования контроллера прямого доступа к памяти одновременно с регистрами текущего адреса и регистрами циклов. В процессе выполнения циклов прямого доступа к памяти их содержимое не изменяется, однако, прочитать состояние этих регистров невозможно.

Регистр режима (6-тиразрядный) определяет режим работы канала, он содержит информацию о номере канала, типе цикла прямого доступа к памяти, т.е. чтение, запись, необходимости автоинициализации, режиме изменения регистра текущего адреса и режиме работы канала. Режим может быть:

-

передача по запросу

-

блочная передача

-

одиночная передача

Блок управления режимом содержит два основных регистра:

-

регистр команд определяет основные параметры работы канала, он загружается при программировании контроллера прямого доступа к памяти микропроцессором

-

регистр условий хранит программно – устанавливаемые разрешения на прямой доступ в память каждому и запоминает факт перехода через ноль регистра хранения базового числа циклов каждого канала.

Контроллер прямого доступа к памяти может работать в двух режимах:

-

режиме программирования

-

режиме выполнения циклов прямого доступа к памяти

В режиме программирования микропроцессор работает с контроллером прямого доступа в память как с внешним устройством. После загрузки микропроцессором в регистре контроллера управляющих слов контроллер переходит в пассивное состояние, в котором будет находиться, пока не поступит запрос на прямой доступ к памяти от внешнего устройства или от микропроцессора. Обнаружив запрос прямого доступа к памяти от внешнего устройства, контроллер выставляет микропроцессору запрос на захват системной магистрали и ждёт от него подтверждение захвата, т.е. отключение микропроцессора от системной магистрали. Получив сигнал подтверждения захвата, контроллер начинает выполнять циклы прямого доступа к памяти. Системная магистраль микропроцессорной системы в режиме прямого доступа к памяти используется контроллером и микропроцессором мультиплексно (коммутируется по очереди), но основное управление системной магистралью выполняет в режиме прямого доступа контроллер прямого доступа. Микропроцессор же получает доступ к магистрали на очень короткие промежутки времени для обмена информацией с основной памятью. Таким образом, несмотря на большую самостоятельность контроллера прямого доступа в память за микропроцессором остаётся всё-таки ведущее положение, так как он, запустив обмен информацией в режиме прямого доступа к памяти, продолжает выполнять свою работу.

Интерфейс системной магистрали.

Системная магистраль является узким местом микропроцессорной системы с так называемой общей шиной, так как все подключённые к ней устройства используют её для передачи своих данных и, таким образом, конкурируют за возможность этой передачи. Системная магистраль – это среда для передачи сигналов управления, адресов и данных к которой параллельно и одновременно могут подключаться несколько устройств микропроцессорной системы. Физически системная магистраль представляет собой систему параллельных печатных проводников на плате. Системные магистрали характеризуются также алгоритмами, по которым передаются сигналы, правилами интерпретации сигналов, порядок обслуживания запросов. Имеются также специальные микросхемы, обеспечивающие работу системной магистрали. Всё это образует понятие интерфейса системной магистрали или стандарта обмена информацией.

Первые системные магистрали микропроцессорных систем имели довольно простую структуру. Со временем системную магистраль стали делить на системную и локальные, графические, периферийные. Исторически все интерфейсы системной магистрали идут стандарта IBM Multibus, для которых фирма IBM разработала комплекс управляющих микросхем. Стандарт Multibus мог обеспечивать передачу 8-ми и 16-тиразрядных данных, работать в мультипроцессорном режиме с несколькими устройствами. Имел 20 линий адреса, 16 линий данных, 50 управляющих и служебных линий. Конфигурация шины системной магистрали технически осуществлялась перемычками и переключателями.

В 1978 году для IBM PS/2 был разработан, так называемый, микроканал МСА. Он имел 20-тиразрядную шину адреса и 32-хразрядную шину данных. Здесь ввели специальную память, которая хранила информацию о конфигурации технических устройств и после отключения питания. Появилась возможность конфигурировать систему программным путём. Затем появился стандарт ISA EISA VISA PCI USB PCMCIA

Стандарт PCMCIA

Этот интерфейс используется, как интерфейс блокнотных компьютеров для подключения расширителей памяти, моделирование (симулирование) контроллеров дисководов, сетевых адаптеров и других устройств. Выполненная по этому стандарту системная магистраль имеет минимальное энергопотребление, шина данных 16-тиразрядная, шина адреса – 24-хразрядная. Этот же стандарт активно используется производителями программируемых логических контроллеров для систем промышленной автоматизации с целью расширения их памяти.