- •1.Общая структура эвм

- •2.Общая архитектура микропроцессора

- •3.Работа микроЭвм.

- •4.Полупроводниковая память и её использование в микропроцессорной технике.

- •5.Эксплуатационные параметры зу.

- •6.Режимные параметры зу

- •7.Структура 2d.

- •8.Структура 3d

- •11.Статическая память (sram)

- •12.Зэ динамические зу

- •14.Внешняя организация и временные диаграммы динамических зу.

- •15.Постоянные Запоминающие Устройства пзу.

- •16.Однократно (электрически) программируемые пзу.

- •17.Репрограммируемые пзу.

- •22.Структура элементарного микропроцессора.

- •24.Функционирование микропроцессорной системы

- •26.Микропроцессор

- •27.Обработка микропроцессором требования прерывания.

- •28.Прерывание с программным опросом.

- •29.Векторная система прерываний.

- •30.Структура приоритетов.

- •31.Синхронизация микропроцессорной системы.

- •32.Программирование микропроцессоров.

- •33.Архитектурные особенности современных микропроцессоров.

- •34.Иерархическая структура памяти.

- •36. Архитектурно независимая спецификация программ.

- •38.Универсальные микропроцессоры.

- •39.Микропроцессор с архитектурой х86.

- •45.Структурная схема базовой модели микропроцессора семейства х86

- •46.Однокристальные микро эвм (микроконтроллеры).

30.Структура приоритетов.

Для обработки одновременно поступающих запросов их упорядочивают по приоритетам. Структура приоритетов может быть программной и схемной. Рассмотрим структуру приоритетов по так называемой дейзи–цепочке.

Рис.31

Структура приоритетов

Рис.31

Структура приоритетов

Наивысшим приоритетом обладает крайнее слева устройство, подключаемое ко входу 0 (ноль). Если это устройство выдаёт запрос на прерывание по линии входа 0 (ноль), т.е. подаёт логическую единицу, то в микропроцессор через логический элемент DD7 в микропроцессоре наступит сигнал о наличии запроса на прерывание и осуществится блокировка устройства 1 и всех устройств с менее высоким приоритетом. При наступлении запроса на прерывание от устройства 1 сигнал на линии входа 1 заблокирует устройство 2 и все устройства с более низким приоритетом, кроме устройства 0 (ноль).

Системы прерываний могут быть как с программным опросом, так и с векторным с использованием приоритетов, с сохранением в стеке векторов состояний с индивидуально сбалансированными триггерами предыдущих устройств и с подпрограммами обработки прерываний.

31.Синхронизация микропроцессорной системы.

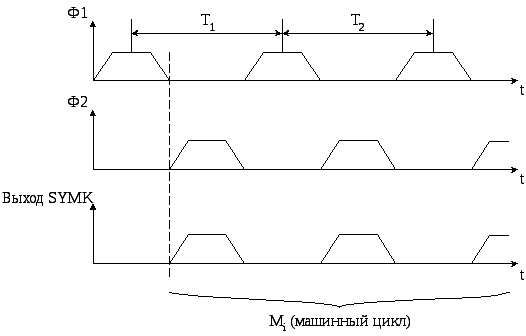

Выполнение каждой команды микропроцессором производится в строго определённой последовательности, определяемой кодом машинной команды и синхронизируется во времени не перекрывающихся сигналами Ф1 и Ф2 генератора тактовых импульсов. При анализе процессов в микропроцессорных системах используются следующие понятия:

Машинный такт Т

Машинный цикл М

Время выполнения команд.

Машинным тактом Т называется период поступления сигналов синхронизации Ф1 или Ф2. длительность машинного такта может быть от нескольких микросекунд до наносекунд.

Машинный цикл М – время, необходимое для извлечения одного байта информации из памяти или выполнения команды, определяемой одним машинным словом. Машинный цикл может состоять из 3 – 5 машинных тактов.

Время выполнения команды (цикл команды) – время получения, декодирования и выполнения команды. В зависимости от вида команды время выполнения команды может состоять из 1 – 5 машинных циклов.

Генератор тактовых импульсов может быть как внешним, так и внутренним по отношению к микропроцессору. При внутреннем – кристалл кварца, определяющий величину и стабильность вырабатываемой частоты, подключается непосредственно к микропроцессору.

Рис.32

Таким образом выход SYNC микропроцессора имеет сигнал, аналогичный сигналу фазы Ф2 тактовых импульсов и служит для синхронизации событий во всей вычислительной системе.

Сигналы ГТИ разделяются на периоды длительностью Т, определённое число которых (3 – 5) и формирует машинный цикл. Период Т всегда имеет постоянную длительность. Длительность же машинного цикла может изменяться.

Машинные циклы определяют функционирование микропроцессора. Например, для рассматриваемого нами типа микропроцессора (Intel 8080) существует 10 типов машинных циклов:

-

Извлечение кода операции.

-

Чтение данных из памяти.

-

Запись данных в память.

-

Извлечение из стека.

-

Запись в стек.

-

ввод данных из внешнего устройства.

-

Запись данных во внешнее устройство.

-

Цикл обслуживания прерывания.

-

Останов.

-

Обслуживание прерывания при работе микропроцессора в режиме останова.

В то время, как слово данных всегда состоит из 1 байта, команда может состоять из 1, 2 и 3 байт. Первый байт любой команды (код операции) поступает из памяти по ШД в регистр команд, из которого подаётся на вход дешифратора команд, который определяет смысл команды. В частности, дешифратор может определить, является ли команда однобайтовой, или она состоит из большего числа байтов. В последнем случае дополнительные байты так же передаются по ШД из памяти и принимаются или одним из регистров общего назначения (ВиС, ДиЕ), или регистром HиL может выполнять роль регистра адреса данных.

Регистр адреса данных (HиL) содержит адрес операнда для команд, обращающихся к памяти, адрес порта для команд ввода/вывода или адрес следующей команды для команд перехода.

Регистры общего назначения содержат операнды для всех команд, работающих с данными. Для указания этих регистров используются 4–хразрядные коды (двоичные). Например, код 0000Н указывает на регистр–аккумулятор. Регистр–аккумулятор участвует во всех логических и арифметических операциях. Он содержит один из операндов перед выполнением операции и получает результат после её выполнения.

Например, команда STORE (разместить данные) разделена на 4 машинных цикла.

Рис.33

М1 – цикл извлечения кода операции

М2 – считывание из программной памяти (адрес, откуда данные)

М3 – считывание из программной памяти (адрес, куда размещать)

М4 – запись данных по адресу

Первичным циклом при выполнении любой команды всегда является М1 – извлечение кода операции. На первом такте Т1 каждого машинного цикла М микропроцессор указывает тип выполняемого цикла с помощью 8–миразрядного слова состояния, выдаваемого на шину данных.

Циклы М2 и М3 (для данной команды) являются циклами считывания из программной памяти.

Цикл М4 – цикл записи в память.

Сочетание этих 4–х действий: извлечение – считывание – считывание – запись и составляет цикл команды. Видно, что машинные циклы выполняются неодинаковое время, таким образом полный цикл команды занимает 13 периодов Т.

Рассмотрим пример выполнения во времени команды непосредственного сложения.

Её цикл будет иметь вид:

Рис.34 Выполнение команды напосредственного сложения

М1 – извлечение кода операции

М2 – считывание из программной памяти числа (операнда)

М3 – сложение

Команда сложить содержимое аккумулятора с содержимым, следующим непосредственно за кодом операции байта программной памяти сумму сохранить в аккумуляторе.

Первым машинным циклом М1 является считывание (извлечение кода операнда), микропроцессор декодирует программу, определяет, что это сложение и определяет также, что для её завершения необходимо 2 дополнительных цикла.

Во втором цикле М2 считывается следующий байт программной памяти, которым является операнд, и в течение цикла М3 выполняется операция сложения в АЛУ аккумулятора. Так как результат (сумма) остаётся в аккумуляторе, то машинный цикл М4 (запись в память) данной команде не нужен и весь цикл команды занимает 9 периодов Т.