- •1.Общая структура эвм

- •2.Общая архитектура микропроцессора

- •3.Работа микроЭвм.

- •4.Полупроводниковая память и её использование в микропроцессорной технике.

- •5.Эксплуатационные параметры зу.

- •6.Режимные параметры зу

- •7.Структура 2d.

- •8.Структура 3d

- •11.Статическая память (sram)

- •12.Зэ динамические зу

- •14.Внешняя организация и временные диаграммы динамических зу.

- •15.Постоянные Запоминающие Устройства пзу.

- •16.Однократно (электрически) программируемые пзу.

- •17.Репрограммируемые пзу.

- •22.Структура элементарного микропроцессора.

- •24.Функционирование микропроцессорной системы

- •26.Микропроцессор

- •27.Обработка микропроцессором требования прерывания.

- •28.Прерывание с программным опросом.

- •29.Векторная система прерываний.

- •30.Структура приоритетов.

- •31.Синхронизация микропроцессорной системы.

- •32.Программирование микропроцессоров.

- •33.Архитектурные особенности современных микропроцессоров.

- •34.Иерархическая структура памяти.

- •36. Архитектурно независимая спецификация программ.

- •38.Универсальные микропроцессоры.

- •39.Микропроцессор с архитектурой х86.

- •45.Структурная схема базовой модели микропроцессора семейства х86

- •46.Однокристальные микро эвм (микроконтроллеры).

26.Микропроцессор

Микропроцессор – это программно управляемое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, выполненное в виде одной интегральной схемы с высокой степенью интеграции электронных элементов.

Кристалл микропроцессора помещается в корпус с большим количеством выводов (от 40 до сотен). Число этих элементов от нескольких тысяч до десятков и сотен миллионов. Например, в 8–миразрядный микропроцессор Intel 8080 (КМ580 ВР80) имел 6000 транзисторов, 40 выводов в корпусе типа DIP.

Рис.27 Микропроцессор (внешний вид)

Один

из выводов GND

(ground). Питание у него было

![]() ,

,

![]()

![]() .

16 выводов

.

16 выводов

![]() образуют канал адреса, подключаются к

адресной шине. 8 выводов

образуют канал адреса, подключаются к

адресной шине. 8 выводов

![]() это входы–выходы, образуют канал данных

и подключаются к шине данных. Они

используют схемы с 3–мя состояниями

(включено, выключено, отключено).

это входы–выходы, образуют канал данных

и подключаются к шине данных. Они

используют схемы с 3–мя состояниями

(включено, выключено, отключено).

SYNG – выход. Синхронизация работы внешних устройств.

DBIN – выход. Выход стробов входных данных, т.е. осуществляет приём информации в микропроцессор.

WAIT – выход. Ожидание.

![]() – выход.

Строб записи.

– выход.

Строб записи.

HOLD – вход. Запрос "захвата" внешним устройством (канала прямого доступа).

HLDA – выход. Подтверждение "захвата".

INT – вход. Требование пребывания внешним устройством.

INTE – выход. Разрешение прерывания.

READY– вход. Готовность ввода данных.

RESET – вход. Сброс.

Входы

![]() и

и

![]() – выходы тактовых импульсов тактового

внешнего генератора. Импульсы сдвинуты

по фазе.

– выходы тактовых импульсов тактового

внешнего генератора. Импульсы сдвинуты

по фазе.

Рис.28 Тактовые импульсы внешнего генератора

Выходы

![]() – двунаправленные, т.е. могут быть как

входами, так и выходами данных. Выходы

– двунаправленные, т.е. могут быть как

входами, так и выходами данных. Выходы

![]() соединяются с 16–тью линиями адресной

шины, обеспечивая адресацию любой из

ячеек памяти или внешнего устройства.

6 выходов: SYNG,

DBIN, WAIT,

соединяются с 16–тью линиями адресной

шины, обеспечивая адресацию любой из

ячеек памяти или внешнего устройства.

6 выходов: SYNG,

DBIN, WAIT,

![]() ,

HLDA

и INTE

– являются сигналами управления и

синхронизации других элементов

микропроцессорной системы.

,

HLDA

и INTE

– являются сигналами управления и

синхронизации других элементов

микропроцессорной системы.

Выход SYNG формирует сигнал синхронизации в начале каждого машинного цикла.

Выход DBIN – можно назвать "приём данных". Его наличие на выходе показывает внешнему устройству на готовность микропроцессора к приёму данных.

Выход WAIT – ожидание, указывает внешним устройствам, что микропроцессор находится в состоянии ожидания.

Выход

![]() указывает, что микропроцессор установил

на шину данные, которые могут быть

записаны в устройство.

указывает, что микропроцессор установил

на шину данные, которые могут быть

записаны в устройство.

Выход HLDA – на этом выходе сигнал появляется в ответ на сигнал HOLD (запрос захвата) и указывает, что АШ и ШД находятся в состоянии высокого сопротивления, т.е. отключены от микропроцессора.

Выход INTE – разрешение прерывания, его сигнал указывает на состояние внутреннего триггера разрешения прерывания. Его состояние в свою очередь устанавливается программно. С помощью специальных команд "разрешение прерывания" и "запрещение прерывания". При уровне 0 (ноль) на выходе INTE приём запросов на прерывание микропроцессором невозможен.

Четыре входа: READY, HOLD, INT, RESET – являются входами управления, воспринимающие поступающие из других устройств микропроцессорной системы информацию.

Вход READY – сигнал "готов", информирует микропроцессор о готовности внешнего устройства к обмену информацией с микропроцессором. При уровне 0 (ноль) на этом входе микропроцессор будет находиться в состоянии ожидания.

Вход HOLD – принимает сигнал на перевод микропроцессора в состояние "захват", при котором АШ и ШД переводятся в состояние высокого сопротивления. Сигнал используется для организации обмена информацией с внешним устройством по каналу прямого доступа в память.

Вход INT – запрос прерывания, сигнал на него поступает от внешнего устройства на прерывание основной программы выполняемой микропроцессором и переход на выполнение подпрограммы обслуживания прерывания. Сигнал INT не воспринимается микропроцессором при работе его в режимах: "захват", "ожидание" или при нулевом состоянии внутреннего триггера "разрешения прерывания микропроцессора", т.е. когда прерывания запрещены.

Вход RESET – сброс, сюда поступает сигнал начальной установки микропроцессора, по которому обнуляются: счётчик команд и внутренние триггеры, в том числе формируются сигналы разрешения прерывания INTЕ и подтверждение захвата HLDA.

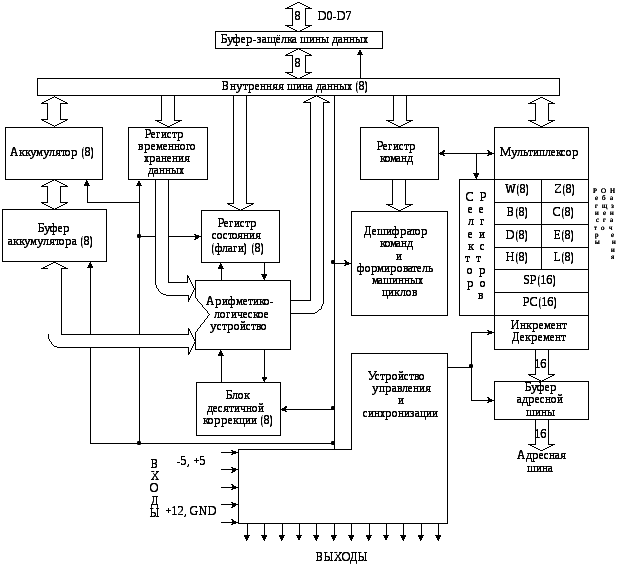

Структура БИС микропроцессора состоит из следующих функциональных блоков:

-

блок регистров и логических цепей их выбора

-

блок арифметико–логического устройства

-

блок АШ и ШД

-

блок "устройство управления"

Рассмотрим структурную схему микропроцессора Intel 8080:

Рис.29 Структурная схема микропроцессора Intel 8080

Одни компоненты структуры (стек, счётчик команд, регистр команд) служат для обработки команд, другие (АЛУ, регистр состояния, регистры общего назначения) служат для обработки данных. Остальные компоненты (дешифратор команд, устройство управления и синхронизации) управляют работой других компонентов. Взаимодействие компонентов осуществляется по внутренним каналам передачи данных микропроцессора.

Связь микропроцессора с другими блоками микропроцессорной системы: ЗУ, устройствами ввода/вывода, происходит по АШ, ШД и шине управления. Информация к микропроцессору от него передаётся по шинам. У данного микропроцессора АШ – 16 линий, ШД – 8 линий и ШУ состоит из 5 линий ведущих к блоку управления и 8 выходящих из него (итого 13).

Схема содержит внутренние регистры: аккумулятор, регистр состояния (индикатор), регистр временного хранения данных, и пар регистров ВиС, ДиЕ, HиL, а также указатель стека SP и счётчик команд РС (program counter).

В состав схемы входят также регистр команд, дешифратор команд, устройство управления и синхронизации, АЛУ и блок десятичной коррекции. Все 8 линий ШД, как и 16тиразрядные адресные выходы снабжены буферами. Микропроцессор содержит также несколько внутренних линий управления, а также питание – это одиночные линии. Используемые программистом (т.е. доступные) регистры можно выделить в отдельную группу.

|

Регистр состояния |

Аккумулятор |

|

B (8) |

C (8) |

|

C (8) |

E (8) |

|

H (8) |

L (8) |

|

SP (16) |

|

|

PC (16) |

|

Основным является регистр А. Регистры ВиС, LиЕ, HиL являются универсальными. Регистры SP и РС – специальные регистры.

Пара регистров HиL может использоваться в качестве одного адреса регистра. В документации на микропроцессорные комплекты содержатся также временные диаграммы, показывающие соотношение между входами тактовых импульсов и внешними сигналами (импульсы синхронизации, записи, ввода/вывода данных и т. д.), а также внутренними операциями. Документы содержат также указания по использованию микропроцессора в случае минимальной вычислительной системы. Такая система должна содержать микропроцессор, генератор тактовых импульсов, устройство управления системы, ПЗУ, ОЗУ и интерфейс портов ввода/вывода информации. В документы входит и подробная информация о системе команд.

Часто таблицы, содержащие состав команд, задаются для двух типов микропроцессора, например, Intel 8086/8088, т.к., имея определённые различия в схематехнике, эти процессоры имеют практически одинаковый состав команд. Часто состав команд имеет вид:

|

Команда

|

Код (Н – код) |

Число байт |

Число тактов |

Машинный цикл |

|

|

8080 |

8085 |

||||

|

ACI DATA |

СЕ |

2 |

7 |

7 |

FR |

Команда в первой колонке – сложения с непосредственным переносом.

Во второй колонке – код операции (в 16тиричном виде).

В третьей – необходимый объём памяти для команды. 2 байта. Первый будет содержать код операции СЕ, а второй – складываемое число.

В четвёртой и пятой колонке приводятся данные о продолжительности выполнения команд в числе тактов для разных типов микропроцессоров.

В шестой – основные внешние операции, выполняемые микропроцессором, где F – извлечение команды (4 периода тактовых импульсов), а R – считывание данных из памяти.

Кроме того, указания пользователю содержат дополнительные детали исполнения каждой команды.

Результатом активизации входа RESET (сброс) микропроцессора является остановка работы микропроцессора по текущей программе и переход к подпрограмме сброса, в результате выполнения которой микропроцессор сбрасывает счётчик команд до заранее предопределённого адреса, например, 0000Н.

Другие внутренние регистры микропроцессора также сбрасываются, или их содержимое, в течение операции сброса изменяется. По окончании команды RESET микропроцессор начинает выполнение команд программы с адреса 0000Н. Этот адрес соответствует началу подпрограммы инициализации системы, содержащейся обычно в ПЗУ.

Вход RESET микропроцессора является асинхронным. Появление сигнала сброса на нём может остановить даже на половину выполненную команду. Большинство других входов микропроцессора синхронные, т.е. их сигналы находятся в определенных фазовых соотношениях с сигналами генератора тактовых импульсов.