- •Память Архитектура памяти.

- •Классификация и физическая организация микросхем памяти, области их применения.

- •Постоянная память

- •Р исунок 4. Пример масочной пзу.

- •Оперативная память

- •Технологии системной памяти. Классическая память dram.

- •Р исунок 6. Структурная схема динамической памяти.

- •Память fpm.

- •Память edo dram.

- •Многобанковая организация памяти

- •Технологии синхронной памяти.

- •Память sdram.

- •Память ddr sdram

- •Память Direct Rambus dram.

- •Р исунок 13. Структура подсистемы памяти Direct Rambus dram.

- •Конструктивные исполнения памяти dram (модули памяти)

- •Адресация памяти в реальном режиме. Логический и физический адреса.

- •Сегментная адресация в реальном режиме.

- •Р исунок 18. Вычисление физического адреса в реальном режиме.

- •Область верхней памяти (hma)

- •Логическое распределение оперативной памяти в реальном режиме.

- •Р исунок 20. Логическая организация памяти. Стандартная память

- •Верхний блок памяти

- •Дополнительная память (ems)

- •Расширенная память (Extended память, xms)

- •Адресация памяти в защищенном режиме работы процессора

- •Разделение адресного пространства на сегменты (сегментация)

- •Механизм страничной памяти.

- •Кэширование данных. Иерархия запоминающих устройств.

- •Р исунок 27. Иерархия запоминающих устройств

- •Р исунок 28. Схема функционирования кэш-памяти

- •Способы отображения основной памяти на кэш (архитектура кэш-памяти).

- •Полностью ассоциативная кэш - память.

- •Р исунок 29. Полностью ассоциативный кэш.

- •Наборно - ассоциативная кэш - память.

- •Р исунок 30. Наборно ассоциативный кэш.

- •Проблема выбора блока кэш-памяти для замещения при промахе

- •Проблема согласования данных

- •Р исунок 31. Сквозная запись.

- •Р исунок 31. Модифицированная сквозная запись

- •Р исунок 32. Обратная запись. Список терминов.

Адресация памяти в реальном режиме. Логический и физический адреса.

Адреса бывают логические и физические. Разберем, что это значит.

Адреса в основной памяти, характеризующие реальное расположение данных в физической памяти, называются физическими адресами. Набор физических адресов, с которым работает программа, называют физическим адресным пространством. Иными словами физический адрес это адрес, по которому процессор (или другое устройство) обращаются к RAM, используя шину адреса. Совсем просто можно сказать, что физический адрес это номер байта, к которому мы обращаемся, в адресном пространстве.

Пользовательская программа, которая загружается в память для исполнения, не видит реальных физических адресов, а имеет дело с, так называемыми, логическими адресами. Это нужно, потому что одна и та же программа может быть загружена в разные области памяти, в зависимости от того какие другие программы к этому моменту уже загружены в память. Логические адреса обычно образуются на этапе создания загрузочного модуля программы. Т.е. логический адрес это адрес, который «знает» программа. Набор адресов, используемый программой, называют логическим адресным пространством

В процессоре должен быть особый узел – блок преобразования адреса (БПА). Программа указывает свой (логический) адрес, он попадает в этот блок, блок что-то с ним делает такое, чтобы из этого адреса сделать физический, и лишь затем такой преобразованный адрес попадает на шину адреса. Это называется отображение логического адреса на физический, или трансляция логического адреса в физический. Способ отображения зависит от режима работы процессора отдельно для реального и отдельно для защищенного режима работы.

Сегментная адресация в реальном режиме.

Реальный режим работы процессора это режим, в котором работало первое поколение процессоров (i8086, i8088), любой современный процессор после включения питания начинает работать в реальном режиме и только потом программно переводится в защищенный режим.

Для работы с памятью используются две шины - шина адреса и шина данных. Физически память устроена таким образом, что возможна адресация как 16-битовых слов, так и отдельных байтов памяти. Кроме того, процессоры начиная с i80386 могут адресовать 32-битовые слова памяти.

В любом случае так называемый физический адрес передаётся из процессора в память по шине адреса. Ширина шины адреса определяет максимальный объём физической памяти, непосредственно адресуемой процессором. Для 20-разрядной адресной шины процессора i8086 используется двадцать двоичных (или пять шестнадцатеричных) разрядов. Однако все регистры этого процессора являются 16-разрядными. Возникает проблема представления 20-разрядного физического адреса памяти при помощи содержимого 16-разрядных регистров. Максимальное число (данное или адрес), которое можно записать в 16-разрядный регистр, составляет всего 216 - 1 = 65535, или 64Кб-1 из нужного нам одного мегабайта.

Для разрешения этой проблемы используется двухкомпонентный логический адрес. Логический адрес состоит из двух 16-разрядных компонент. Такой способ называется сегментной адресацией памяти.

Суть сегментной адресации заключается в следующем. Обращение к памяти осуществляется исключительно с помощью сегментов. Сегментом называется условно выделенная область адресного пространства определённого размера. В реальном режиме процессора всё адресное пространство делится на одинаковые сегменты размером 64Кб.

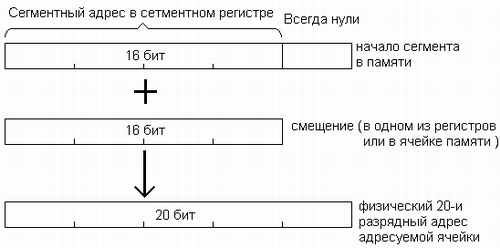

Физический адрес любой ячейки памяти вычисляется процессором путем сложения начального адреса сегмента (базы сегмента), в котором располагается эта ячейка, со смещением к ней (в байтах) от начала сегмента (рис. 17). Это смещение иногда называют относительным адресом.

Рисунок 17 Образование физического адреса из сегментного адреса и смещения.

Покажем как вычисляется физический адрес – для получения 20-разрядного физического адреса к сегментной компоненте (заносящейся в сегментный регистр) приписывается справа четыре нулевых бита (для расширения до 20 разрядов), затем полученное число складывается с компонентой смещения. Перед сложением к компоненте смещения слева дописывается четыре нулевых бита (также для расширения до 20 разрядов). Эту процедуру иллюстрирует рисунок 18