- •История развития архитектуры эвм

- •Нулевое поколение (1492 – 1945)

- •Первое поколение (1937-1953)

- •Второе поколение (1954 - 1962)

- •Третье поколение (1963-1972)

- •Четвертое поколение (1972-1984)

- •Пятое поколение (1984-1990)

- •Шестое поколение (1990-)

- •Концепция машины с хранимой в памяти программой

- •Принцип двоичного кодирования

- •Принцип программного управления

- •Принцип однородности памяти

- •Принцип адресности

- •Типы структур вычислительных машин и систем

- •Структуры вычислительных машин

- •Структуры вычислительных систем

- •Процессор. Структурная схема процессора. Понятие о микропрограммном управлении Структурная схема процессора

- •Алгоритмы выполнения операций. Микропрограммы

- •Синтез микропрограммного автомата. Синтез устройства управления

- •Обратная структурная таблица

- •Управляющие автоматы с программируемой логикой

- •Адресная структура памяти

- •Принципы построения устройств памяти

- •Адресная, ассоциативная и стековая организация памяти

- •Адресная память

- •Ассоциативная память

- •Стековая память

- •Команды процессора

- •Методы повышения производительности работы процессора

- •1.Конвейеризация (конвейер операций)

- •2. Процессоры с risc – архитектурой

- •3. Организация кэш-памяти

- •3.1. Техническая идея кэш-памяти

- •3.2. Архитектура кэш-памяти

- •3.2.1. Кэш память с прямым отображением

- •3.2.2. Полностью ассоциативная кэш память

- •3.2.3. Частично ассоциативная кэш память

- •3.3 Алгоритм замещения строк в кэш памяти

- •3.4 Методы записи в кэш память

- •Микропроцессор Intel 80i86

- •Страничная организация памяти

- •Буфер ассоциативной трансляции

- •Организация виртуальной памяти

- •Встроенные средства защиты информации в микропроцессорах фирмы intel

- •1. Концепции и компоненты защищенного режима

- •Независимость подготовки пользовательских программ и их защита от взаимных помех.

- •Защита программ операционной системы от помех при сбоях в программах пользователей.

- •Защита программ ос верхнего уровня от помех при сбоях в программах ос нижнего уровня.

- •Защита программ от отрицательных последствий при программных сбоях.

- •Защита целостности функционирования вычислительной системы.

- •2. Информационная основа работы механизма защиты

- •3. Уровни привилегий

- •Концепция уровней привилегий.

- •Задание уровней привилегий.

- •Проверка корректности использования отдельных команд.

- •Защита данных.

- •4.3 Защита программ.

- •Принципы организации системы прерывания

- •Программируемый контроллер прямого доступа к памяти

- •Лабораторная работа №1

- •Размещение байт и слов в памяти.

- •Лабораторная работа №2

- •Список операций

Принципы организации системы прерывания

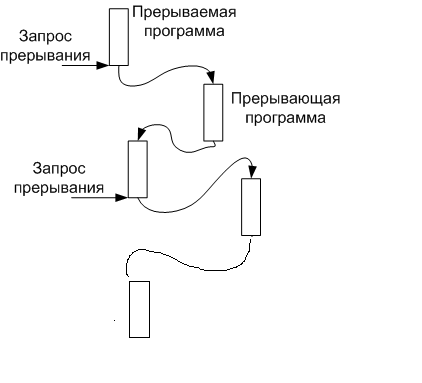

Во время выполнения ЭВМ текущей программы внутри машины в связанной с ней внешней среде могут возникать события , требующие немедленной реакции на них со стороны машины. Реакция состоит в том, что машина прерывает выполнение текущей программы и переходит к выполнению некоторой другой программы, специально предназначенной для данного события. По завершению прерывающей программы ЭВМ возвращается к выполнению прерванной программы к той точке, где произошло прерывание.

Каждое событие, требующее прерывания, сопровождается сигналом, который называется запросом прерывания.

Моменты возникновения запросов прерывания заранее неизвестны и поэтому не могут быть учтены при программировании. Запросы на прерывание могут возникать как в самой машине, так и в ее внешней среде.

Внутренние запросы – сбой в работе аппаратуры, переполнение разрядной сетки, деление на 0, нарушение защиты памяти, различные ситуации при выполнении операции ввода/вывода.

Запросы из внешней среды – от других ЭВМ и от различных датчиков, которые подключены к машине. Возможность прерывания программы важное архитектурное свойство ЭВМ, позволяющее эффективно использовать производительность процессора при наличии несколько одновременно протекающих во времени процессов, требующих управление и обслуживание со стороны процессора.

Для реализации прерывания программ в состав ЭВМ вводят специальные аппаратные и программные средства. Совокупность аппаратных и программных средств, необходимых для реализации прерываний, называется системой прерывания программ.

Основными функциями системы прерывания программ являются:

1.Запоминание состояния прерываемой программы и осуществление перехода к прерывающей программе.

2.Восстановление состояния прерванной программы и возврат к ней.

Основной характеристикой систем прерываний является глубина прерываний. Глубина прерываний - это максимальное число программ, которые могут прерывать друг друга. Если при выполнении прерывающей программы другие запросы на прерывание не обслуживаются, то система имеет единичную глубину. Глубина прерывания равна n, если допускаются последовательные прерывания до n программ.

Поскольку прерывающая программа может быть в свою очередь прерванной только в случае поступления запроса с более высоким приоритетом, то глубина прерывания обычно совпадает с числом уровней приоритета в системе прерывания. В ЭВМ число различных запросов прерывания может достигать нескольких десятков и сотен. В таких случаях запросы разделяют на несколько классов или уровней.

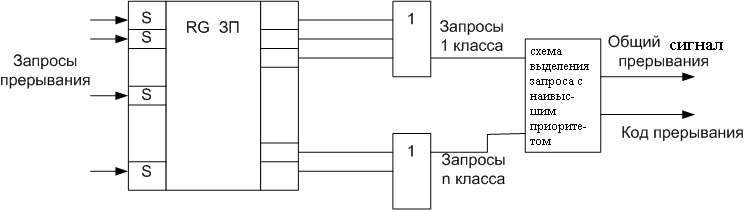

З апросы

одного уровня имеют одинаковый приоритет.

Обычно запросы от всех источников

прерывания поступают на специальный

регистр запросов прерывания RG

ЗП. Поступивший

запрос устанавливает соответствующий

разряд регистра в единичное состояние.

Наличие 1 в данном разряде указывает на

наличие запроса на прерывание от

определенного источника, поскольку

каждому запросу соответствует свой

разряд регистра.

апросы

одного уровня имеют одинаковый приоритет.

Обычно запросы от всех источников

прерывания поступают на специальный

регистр запросов прерывания RG

ЗП. Поступивший

запрос устанавливает соответствующий

разряд регистра в единичное состояние.

Наличие 1 в данном разряде указывает на

наличие запроса на прерывание от

определенного источника, поскольку

каждому запросу соответствует свой

разряд регистра.

Запросы одного уровня (класса) объединяются с помощью дизъюнкторов. Далее стоит схема, которая выделяет запросы с наивысшим приоритетом. Информация о действительной причине прерывания содержится в коде прерывания. После принятия запроса прерывания на обслуживание и передачи управления прерывающей программе, соответствующий разряд RG ЗП сбрасывается в ноль.

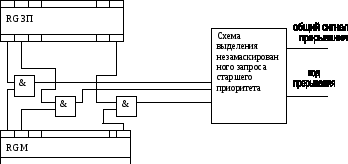

Очень часто встречается ситуация, когда приоритет за каждым классом прерывания не может быть закреплен жестко и может меняться в процессе решения задачи. В этом случае применяется программное управление приоритетом на основе маски прерывания.

Маска прерывания представляет собой двоичный код, разряды которого поставлены в соответствие запросам или классам прерывания. Маска загружается в специальный регистр маски RGM. Единичное состояние в данном разряде маски разрешает, а нулевое – запрещает (маскирует) прерывание текущей программы по соответствующему запросу, то есть каждая прерывающая программа может устанавливать свою маску и устанавливать произвольные приоритетные соотношения между запросами прерываний.

При формировании маски единицы устанавливаются в разряды соответствующие запросам с более высоким приоритетом, чем у данной программы, а в остальные разряды записываются нули, запрещая тем самым выполнение программ с меньшим приоритетом.

Конъюнкторы выделяют не замаскированные запросы прерывания, из которых специальная схема выделяет наиболее приоритетный запрос и формирует его код. С замаскированными запросами в зависимости от причин прерываний поступают двумя образами: либо они игнорируются, либо запоминается с тем, чтобы осуществить прерывание, когда запрет на прерывание будет снят.

В ЭВМ часто используются так называемые векторные прерывания. Прерывание называется векторным, если источник прерывания посылают в процессор адрес ячейки памяти, в которой находится его вектор прерывания. Он обычно состоит из нескольких слов и содержит следующую информацию:

1. начальный адрес прерывающей программы(начальный адрес программы обработки прерывания от данного источника)

2.слово состояния процессора(ССП)

Формат вектора прерываний

Получив адрес вектора прерывания процессор читает из ОЗУ сам вектор и передает управление прерывающей программы, чей адрес находится в первом слове этого вектора прерывания. Таким образом при векторном прерывании каждый источник прерывания, например ПУ, имеет свою прерывающую программу, переход к которой происходит по адресу, содержащемуся в векторе.

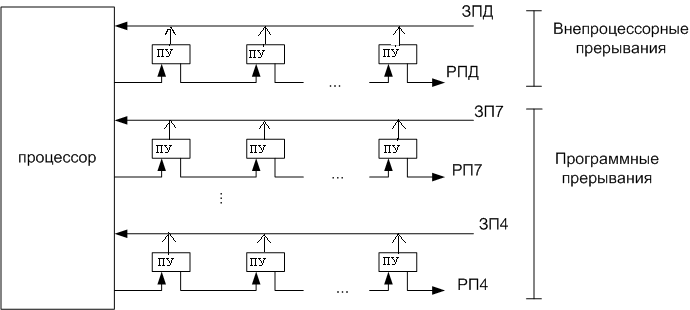

Система прерывания PDP-11

В PDP-11 возможно два вида прерываний от внешних устройств.

1.Внепроцессорное прерывание, при котором ПУ осуществляет обмен данными непосредственно с ОЗУ или другими ПУ, минуя процессор. Это внепроцессорная передача данных. Такой режим работы называется прямой доступ в память (ПДП).

2.Программное прерывание, при котором управление передается специальной программе обработки прерывания. Это программная передача данных под управлением процессора.

Всего в PDP-11 имеется 4 уровня программных прерываний и 1 уровень внепроцессорных прерываний.

Устройства, поставляющие запросы на линию ЗПД, имеют наивысший абсолютный приоритет. В этом случае управление передачей данных происходит под управлением того ПУ, которое выставило сигнал ЗПД (запрос прямого доступа). В этом случае обмен данными идет без участия процессора.

Устройства, которые получают управление интерфейсом по одной из линий запросов передачи ЗП, могут использовать возможности процессора для обработки запросов прерывания.

При получении запроса на одной из линий ЗП4 – ЗП7 процессор сравнивает приоритет, то есть номер линии со своим приоритетом. Если приоритет линии выше, то процессор выдает соответствующий сигнал по РП. При равенстве приоритетов линии ЗП и процессора прерывание не происходит. Поэтому, если приоритет процессора равен 7, то ни одно из ПУ не может прервать текущую программу процессора.

Линии РПД и РП проходят последовательно через все устройства, находящиеся на их уровне.

Если несколько устройств одного уровня выставили запрос, то удовлетворяется запрос того ПУ, которое первым подключено к соответствующей линии РП.

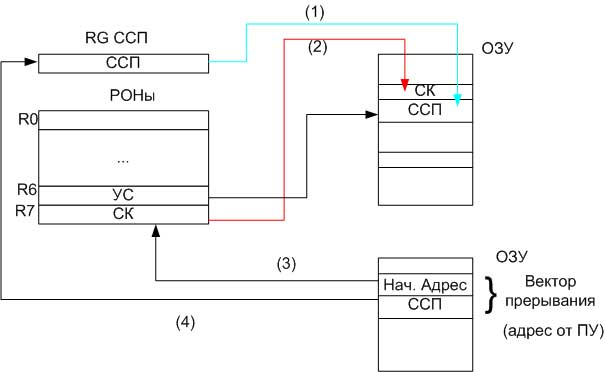

Рассмотрим процедуру обслуживания прерывания для ПУ , пославшего запрос по одной из линий ЗП 4 – ЗП 7.

1.Если приоритеты позволяют, то процессор предоставляет интерфейс запрашивающему ПУ.

2.Получив управление интерфейсом (сигнал РП), устройство посылает в процессор сигнал прерывания и адрес ячейки памяти, которая содержит вектор прерывания. Каждая ПУ имеет свой вектор прерывания. В векторе прерывания – 2 слова. Первое слово содержит начальный адрес программы обслуживания прерывания от данного устройства. Второе слово – содержит слово состояние процессора – ССП. После получения адреса вектора прерывания начинается процедура обслуживания прерывания.

3.Процессор вводит текущее значение ССП, а затем текущее значение счетчика команд ( СК ) – в стек.

В качестве аппаратного указателя стека (УС) используется РОН R6. Таким образом, происходит сохранение параметров прерываемой программы (сохраняется ССП и адрес точки возврата в прерванную программу).

4.Новое значение СК и ССП выбираются из ОЗУ по адресу, указанному запрашивающим ПУ. После этого запускается программа обслуживания устройства.

5.По окончании работы программы обслуживания устройства происходит возврат к прерванной программе, для чего два верхних слова из стека загружаются обратно в СК и RG ССП. Возобновляется выполнение прерванной программы с точки, где произошло прерывание.

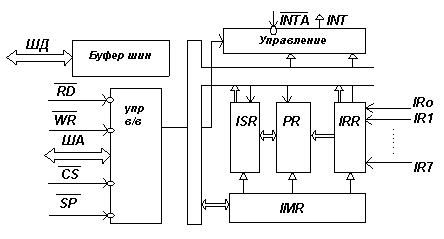

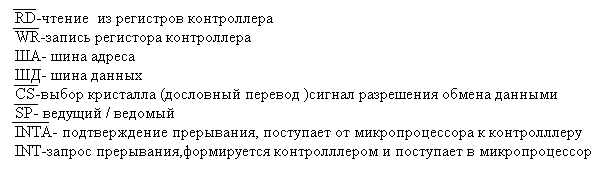

Программируемый контроллер прерываний фирмы Intel

Программируемый контроллер прерываний обеспечивает управление восьми уровневыми векторными приоритетными прерываниями, то есть один контроллер прерываний обеспечивает приемную обработку до восьми сигналов прерывания.

Структурная схема контроллера прерываний имеет следующий вид. (Рис.1.)

Рис.1.

Рис.1.

![]() -запрос

прерывания

-запрос

прерывания

Запросы прерывания обрабатываются тремя взаимосвязанными регистрами. Регистр запросов (IRR) фиксирует все запросы прерываний, а регистр обслуживания (ISR) хранит только те прерывания, которые приняты на обслуживание .

Регистр масок-IMR идентифицирует маскируемые коды прерывания.

Шифратор приоритетов (арбитр приоритетов)-PR анализирует содержимое этих трех регистров и определяет нужно или нет генерировать сигнал запроса прерывания INT.

Контроллер прерываний может работать в одном из двух режимов:

1)контроллер является ведущим.

2)контроллер является ведомым.

Если на вход контроллера поступает сигнал SP с отриц.=1, то в этом случае контроллер является ведущим, в противном случае ведомым. Когда контроллер ведомый, то микропроцессор загружает в его регистры специальную управляющую информацию. Когда контроллер ведущий, то он управляет процессом передачи данных.

Рассмотрим алгоритм работы контроллера:

1)ПУ посылает по одной из линий единичный сигнал.

2)в регистре IRR происходит установка соответствующих разрядов в единицу под действием сигналов, поступающих от ПУ.

3)незамаскированные запросы, то есть те, для которых соответствующие разряды регистров IMR содержат 1, передаются в арбитр PR ,замаскированные запросы при этом блокируются.

4)арбитр PR выделяет наиболее приоритетный запрос и передает его в регистр обслуживания ISR.

5)приоритет запроса сравнивается с текущим приоритетом программы, выполняемой в микропроцессоре. Если приоритет запроса выше приоритета программы, то контроллер формирует сигнал прерывания INT, в противном случае обработка запроса откладывается.

6)Микропроцессор принимает запросы прерываний INT и начинает реализовывать последовательности прерываний, выполняя два цикла подтверждения прерывания, с формированием сигнала в каждом из этих циклов.

7)В первом цикле подтверждение прерывания происходит установка соответствующего разряда ISR и сброса аналогичного сигнала в регистре IRR.

8)Во втором цикле подтверждение прерывания текущее содержимое адреса вектора прерывания передается в микропроцессор по шине данных.

9)Микропроцессор принимает этот адрес и использует его для обращения к таблице векторов прерывания, где хранятся сами вектора прерывания.

10)Текущее значение вектора прерывания , прерванное программой, запоминается в стеке, а вместо него в микропроцессор загружается вектор прерывания , выбранный из таблицы векторов прерывания. Управление передается прерывающей программе по адресу, содержащемуся в первом слове вектора прерывания.

11)По завершению прерывающей программы происходит восстановление сохраненного в стеке вектора прерывания прерванной программы, после этого управление возвращается к прерванной программе с той точки, где произошло прерывание.

Контроллер может быть запрограммирован на один из следующих режимов работы:

1)вложенные прерывания.

Каждому

из восьми входов запросов прерывания

![]() назначается

фиксированный приоритет , при этом

наивысший приоритет будет у запроса

назначается

фиксированный приоритет , при этом

наивысший приоритет будет у запроса

![]() и

далее в порядке убывания приоритетов

до

и

далее в порядке убывания приоритетов

до

![]() .Запрос

с большим приоритетом прерывает

обслуживание того ПУ , у которого меньший

приоритет.

.Запрос

с большим приоритетом прерывает

обслуживание того ПУ , у которого меньший

приоритет.

2)круговой (циклический) приоритет

В

этом режиме также каждому входу

![]() назначается приоритет, однако, после

запроса и обслуживания прерывания

приоритеты изменяются в круговом порядке

таким образом, что последний обслуженный

вход будет иметь самый маленький

приоритет.

назначается приоритет, однако, после

запроса и обслуживания прерывания

приоритеты изменяются в круговом порядке

таким образом, что последний обслуженный

вход будет иметь самый маленький

приоритет.

Организация прямого доступа к памяти

Одним из способов обмена данными с ПУ является обмен в режиме прямого доступа к памяти (ПДП). В этом режиме обмен данными между ПУ и основной памятью микроЭВМ происходит без участия процессора. Обменом в режиме ПДП управляет не программа, выполняемая процессором, а электронные схемы, внешние по отношению к процессору. Обычно эти схемы размещаются в специальном контроллере, который называется контроллером прямого доступа к памяти.

Режим ПДП обычно используется при начальной загрузке программ в основную память микроЭВМ из устройств ввода и для организации обмена данными с быстродействующими внешними запоминающими устройствами (дисковыми накопителями).

Контроллер ПДП подключается к основной памяти посредством системного интерфейса. При этом возникает проблема совместного использования шин системного интерфейса процессором и контроллером ПДП. Существует два основных способа решения этой проблемы:

1. Реализация обмена в режиме ПДП с захватом цикла.

2. Реализация обмена в режиме ПДП с блокировкой процессора.

Наиболее простой способ организации ПДП с захватом цикла состоит в использовании контроллером ПДП тех машинных циклов процессора, когда процессор не обменивается данными с памятью. В такие циклы контроллер ПДП может обмениваться данными с памятью, не мешая работе процессора и не снижая его производительности. Однако при использовании такого способа организации ПДП обмен возможен только в случайные моменты времени и одиночными байтами, что не всегда является удобно.

Поэтому на практике чаще используется режим ПДП с захватом цикла и принудительным отключением процессора от шин системного интерфейса. Для реализации такого режима системные интерфейс дополняется двумя линиями для передачи управляющих сигналов: «Запрос прямого доступа к памяти» (ЗПДП) и «Подтверждение прямого доступа к памяти» (ППДП).

Управляющий сигнал ЗПДП формируется контроллером ПДП. Процессор, получив этот сигнал, приостанавливает выполнение очередной команды, не дожидаясь ее завершения, выдает в системный интерфейс управляющий сигнал ППДП и отключается от шин системного интерфейса. С этого момента управление шинами системного интерфейса передается контроллеру ПДП. Контроллер по шинам системного интерфейса осуществляет обмен одним байтом или словом данных с памятью микроЭВМ, а затем, сняв сигнал ЗПДП, возвращает управление системным интерфейсом процессору.

Как только контроллер ПДП будет готов к обмену следующим байтом, он вновь захватывает цикл процессора. Эта процедура будет продолжаться до тех пор, пока не будут переданы все данные. В промежутках между сигналами ЗПДП процессор продолжает выполнять команды программы. Тем самым выполнение программы процессора замедляется, но в меньшей степени, чем при обмене в режиме прерывания.

Прямой доступ в память с блокировкой процессора отличается от ПДП с захватом цикла тем, что управление системным интерфейсом передается контроллеру ПДП на все время обмена блоком данных. Такой режим ПДП необходим в тех случаях, когда процессор не успевает выполнить хотя бы одну команду между очередными операциями обмена в режиме ПДП, и поэтому режим захвата цикла не имеет смысла. Такая ситуация возникает тогда, когда время обмена одним байтом между ПУ и памятью сопоставима с циклом процессора из-за малой производительности последнего.

Для организации обмена данными между памятью и ПУ контроллер должен иметь в своем составе регистр адреса для обращения к памяти и счетчик байт для подсчета числа переданных байт. Перед началом обмена процессор должен загрузить в регистр начальный адрес выделенной ПУ области памяти, а в счетчик байт – размер этой области. Таким образом, контроллер подготавливается к выполнению операции ввода данных в режиме ПДП. Далее в процессе передачи данных содержимое регистра адреса и счетчика байт изменяется. После передачи очередного байта в память содержимое регистра адреса увеличивается на единицу, а из содержимого счетчика байт вычитается единица. Как только содержимое счетчика станет равно нулю, контроллер прекратит передачу данных от ПУ в память, поскольку нужное количество байт уже передано и выделенная область памяти заполнена.

К одному контроллеру ПДП можно подключать несколько ПУ , которые получают право обмена данными с памятью в соответствии с их приоритетами.

Контроллеры ПДП обычно реализуются в виде одной микросхемы, к которой подключаются несколько ПУ.