- •История развития архитектуры эвм

- •Нулевое поколение (1492 – 1945)

- •Первое поколение (1937-1953)

- •Второе поколение (1954 - 1962)

- •Третье поколение (1963-1972)

- •Четвертое поколение (1972-1984)

- •Пятое поколение (1984-1990)

- •Шестое поколение (1990-)

- •Концепция машины с хранимой в памяти программой

- •Принцип двоичного кодирования

- •Принцип программного управления

- •Принцип однородности памяти

- •Принцип адресности

- •Типы структур вычислительных машин и систем

- •Структуры вычислительных машин

- •Структуры вычислительных систем

- •Процессор. Структурная схема процессора. Понятие о микропрограммном управлении Структурная схема процессора

- •Алгоритмы выполнения операций. Микропрограммы

- •Синтез микропрограммного автомата. Синтез устройства управления

- •Обратная структурная таблица

- •Управляющие автоматы с программируемой логикой

- •Адресная структура памяти

- •Принципы построения устройств памяти

- •Адресная, ассоциативная и стековая организация памяти

- •Адресная память

- •Ассоциативная память

- •Стековая память

- •Команды процессора

- •Методы повышения производительности работы процессора

- •1.Конвейеризация (конвейер операций)

- •2. Процессоры с risc – архитектурой

- •3. Организация кэш-памяти

- •3.1. Техническая идея кэш-памяти

- •3.2. Архитектура кэш-памяти

- •3.2.1. Кэш память с прямым отображением

- •3.2.2. Полностью ассоциативная кэш память

- •3.2.3. Частично ассоциативная кэш память

- •3.3 Алгоритм замещения строк в кэш памяти

- •3.4 Методы записи в кэш память

- •Микропроцессор Intel 80i86

- •Страничная организация памяти

- •Буфер ассоциативной трансляции

- •Организация виртуальной памяти

- •Встроенные средства защиты информации в микропроцессорах фирмы intel

- •1. Концепции и компоненты защищенного режима

- •Независимость подготовки пользовательских программ и их защита от взаимных помех.

- •Защита программ операционной системы от помех при сбоях в программах пользователей.

- •Защита программ ос верхнего уровня от помех при сбоях в программах ос нижнего уровня.

- •Защита программ от отрицательных последствий при программных сбоях.

- •Защита целостности функционирования вычислительной системы.

- •2. Информационная основа работы механизма защиты

- •3. Уровни привилегий

- •Концепция уровней привилегий.

- •Задание уровней привилегий.

- •Проверка корректности использования отдельных команд.

- •Защита данных.

- •4.3 Защита программ.

- •Принципы организации системы прерывания

- •Программируемый контроллер прямого доступа к памяти

- •Лабораторная работа №1

- •Размещение байт и слов в памяти.

- •Лабораторная работа №2

- •Список операций

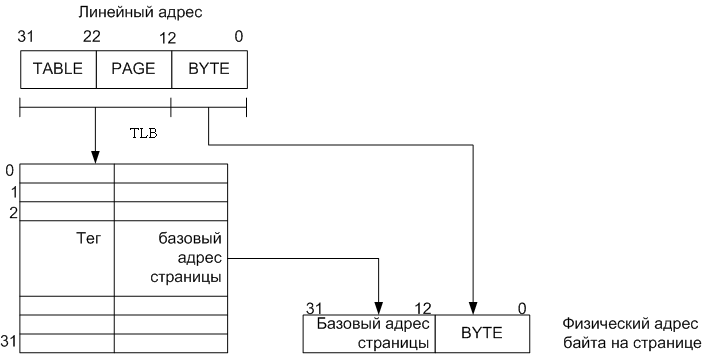

Буфер ассоциативной трансляции

TLB представляет собой память с ассоциативной выборкой, которая содержит 20-тиразрядные базовые адреса 32-х страниц, то есть, старшие 20 разрядов физического адреса страницы. Каждый из базовых адресов имеет свой признак (тег). В качестве тега используются старшие 20 разрядов линейного адреса, то есть поля TABLE и PAGE. Формирование физического адреса с использованием TLB производится следующим образом:

При поступлении в блок управления страницами линейного адреса его старшие 20 разрядов сравниваются с тегами физических адресов, хранящихся в TLB. Если обнаруживается совпадение этих разрядов с каким-либо из тегов, то из TLB выбирается соответствующий этому тегу базовый адрес. Страничный диспетчер формирует 32-хразрядный физический адрес, в котором выбранный из TLB базовый адрес задает 20 старших разрядов, а поле BYTE линейного адреса – 12 младших разрядов.

Случай, когда базовый адрес страницы находится в TLB, называется КЭШ-попаданием. При этом не требуется обращаться к ОЗУ для выборки указателя входа в таблицу страниц и в саму страницу.

Если базовый адрес нужной страницы отсутствует в TLB, то такое обращение называется КЭШ-промахом. При этом микропроцессор выполняет описанную выше процедуру формирования физического адреса с помощью каталога разделов и таблиц страниц. Полученный при этом из таблицы страниц 20 - разрядный базовый адрес вместе с соответствующими 20 разрядами старшей части адреса (тегом) записывается в свободную или дольше других занимаемую ячейку TLB. Таким образом, обеспечивается непрерывное обновление содержимого TLB.

Помимо тега для каждого базового адреса страницы в TLB хранится дополнительная информация, позволяющая определить, какую страницу можно заменить на вновь вводимую. Поскольку TLB хранит адреса только 32 страниц объема 4 кб каждая, то микропроцессор может непосредственно формировать физические адреса для 128 кб памяти (4 х 32). При этом по статистике вероятность КЭШ попадания равна 0,98 и, следовательно, только 2% обращений вызывают КЭШ промах и требуют двухступенчатого преобразования адресов.

Организация виртуальной памяти

Механизм страничной организации памяти может быть легко использован для организации виртуальной памяти.

Страничную виртуальную организацию памяти поддерживает бит Р – бит присутствия. В системах с виртуальной памятью бит Р должен точно отображать место нахождения виртуальной страницы, которая может находиться в ОЗУ, либо на внешнем диске. Если страница находится в ОЗУ, то бит Р устанавливается в единичное состояние, а если на внешнем диске, то бит Р=0.

Операционная система и микропроцессор следят за состоянием бита Р. Микропроцессор автоматически проверяет состояние бита Р в каталоге разделов и таблице страниц при каждом обращении к памяти. Если Р=1, то страница находится в оперативной памяти и производится стандартная трансляция адресов с помощью либо универсального алгоритма формирования физического адреса, либо с помощью ТЛБ. Если Р=0, то обращение к памяти не выполняется , так как нужной страницы в ОЗУ нет. Такая ситуация квалифицируется как ошибка страниц и микропроцессор генерирует исключительную ситуацию. Происходит прерывание программы, вызвавшей исключительную ситуацию, и управление передается операционной системе. Операционная система находит нужную страницу на внешнем диске, загружает ее в ОЗУ, устанавливает бит Р в единичное состояние и возвращает управление прерванной программы. Прерванная программа возобновляет свою работу с той точки, где произошло прерывание.

При необходимости, когда оперативная память заполнена полностью, операционная система удаляет на внешний диск те разделы и страницы, к которым долгое время не было обращений, освобождая тем самым место для вновь вводимых страниц в оперативную память. Таким образом, происходит непрерывное обновление содержимого ОЗУ. ОЗУ содержит только те программы и данные, которые нужны в данный момент времени. Те же программные средства, к которым долгое время не было обращения, постепенно выводятся на внешний диск. Вот так работает виртуальная память.

Объем

виртуальной памяти равен максимальному

объему одного сегмента (4Гбайта)

умноженного на количество сегментов.

Количество сегментов определяется

объемом глобальной и локальной таблиц

дескрипторов. В каждой из этих таблиц

до

![]() дескрипторов, что позволяет адресовать

дескрипторов, что позволяет адресовать

![]() сегментов. Число 13 – разрядность поля

“INDEX”. Таким образом максимальное

количество сегментов, которое может

адресовать микропроцессор равняется:

сегментов. Число 13 – разрядность поля

“INDEX”. Таким образом максимальное

количество сегментов, которое может

адресовать микропроцессор равняется:

![]()

Максимальный

объем одного сегмента равен

![]() =4 Гбайта

=4 Гбайта

Таким образом, максимальный объем виртуальной памяти равен: