- •История развития архитектуры эвм

- •Нулевое поколение (1492 – 1945)

- •Первое поколение (1937-1953)

- •Второе поколение (1954 - 1962)

- •Третье поколение (1963-1972)

- •Четвертое поколение (1972-1984)

- •Пятое поколение (1984-1990)

- •Шестое поколение (1990-)

- •Концепция машины с хранимой в памяти программой

- •Принцип двоичного кодирования

- •Принцип программного управления

- •Принцип однородности памяти

- •Принцип адресности

- •Типы структур вычислительных машин и систем

- •Структуры вычислительных машин

- •Структуры вычислительных систем

- •Процессор. Структурная схема процессора. Понятие о микропрограммном управлении Структурная схема процессора

- •Алгоритмы выполнения операций. Микропрограммы

- •Синтез микропрограммного автомата. Синтез устройства управления

- •Обратная структурная таблица

- •Управляющие автоматы с программируемой логикой

- •Адресная структура памяти

- •Принципы построения устройств памяти

- •Адресная, ассоциативная и стековая организация памяти

- •Адресная память

- •Ассоциативная память

- •Стековая память

- •Команды процессора

- •Методы повышения производительности работы процессора

- •1.Конвейеризация (конвейер операций)

- •2. Процессоры с risc – архитектурой

- •3. Организация кэш-памяти

- •3.1. Техническая идея кэш-памяти

- •3.2. Архитектура кэш-памяти

- •3.2.1. Кэш память с прямым отображением

- •3.2.2. Полностью ассоциативная кэш память

- •3.2.3. Частично ассоциативная кэш память

- •3.3 Алгоритм замещения строк в кэш памяти

- •3.4 Методы записи в кэш память

- •Микропроцессор Intel 80i86

- •Страничная организация памяти

- •Буфер ассоциативной трансляции

- •Организация виртуальной памяти

- •Встроенные средства защиты информации в микропроцессорах фирмы intel

- •1. Концепции и компоненты защищенного режима

- •Независимость подготовки пользовательских программ и их защита от взаимных помех.

- •Защита программ операционной системы от помех при сбоях в программах пользователей.

- •Защита программ ос верхнего уровня от помех при сбоях в программах ос нижнего уровня.

- •Защита программ от отрицательных последствий при программных сбоях.

- •Защита целостности функционирования вычислительной системы.

- •2. Информационная основа работы механизма защиты

- •3. Уровни привилегий

- •Концепция уровней привилегий.

- •Задание уровней привилегий.

- •Проверка корректности использования отдельных команд.

- •Защита данных.

- •4.3 Защита программ.

- •Принципы организации системы прерывания

- •Программируемый контроллер прямого доступа к памяти

- •Лабораторная работа №1

- •Размещение байт и слов в памяти.

- •Лабораторная работа №2

- •Список операций

3.4 Методы записи в кэш память

При работе с КЭШ памятью преобладают операции чтения, а операции записи составляют меньше 10% трафика памяти. Операция чтения происходит за меньшее время, чем операция записи, поскольку строка из КЭШ памяти может быть прочитана в то же самое время, когда читаются и сравниваются теги строки и адреса. При КЭШ попадании прочитанная строка или ее часть немедленно передаются процессору. При КЭШ промахе от заранее прочитанной строки нет никакой пользы.

При записи новой информации в КЭШ операция сравнения тегов должна предшествовать всем остальным действиям, поскольку проверка тегов не может выполняться параллельно с другой работой, то операция записи занимает больше времени, чем операция чтения.

Возможны два способа записи в КЭШ память:

1)метод сквозной записи;

2)метод обратной записи.

Первый метод предполагает наличие двух копий данных: одной в КЭШ памяти, а другой в ОЗУ. Запись выполняется одновременно и в КЭШ и в ОЗУ. В результате системная шина и процессор работают с большой нагрузкой, поскольку на каждую операцию изменения данных приходится две операции записи. Метод сквозной записи имеет преимущество в том, что ОЗУ всегда имеет свежую копию данных, что важно в мультипроцессорных системах и при организации ввода-вывода данных. Кроме того сквозная запись имеет простую схемную реализацию. Такой метод записи использовался в 80486 микропроцессоре фирмы Intel.

При использовании метода обратной записи цикл записи происходит только в КЭШ памяти, если в КЭШе находится строка, к которой идет обращение (КЭШ попадание). Если адресуемой строки в КЭШ нет, то информация записывается сразу в ОЗУ. При КЭШ попадании запись в ОЗУ происходит только при замещении строки КЭШа. Для сокращения частоты копирования строк запись в ОЗУ происходит только в том случае, если замещаемая строка КЭШа была модифицирована, то есть изменена. Для определения факта изменения строки с каждой строкой КЭШа связывают так называемый «бит модификации». Этот бит показывает, была ли изменена строка в КЭШ памяти или нет. Если строка в КЭШ не модифицирована, то обратное копирование отменяется, поскольку ОЗУ содержит туже самую информацию, что и КЭШ память.

Преимущество данного метода заключается в том, что запись выполняется со скоростью КЭШ памяти. А несколько записей на одну и туже строку КЭШа требует только одной записи – в ОЗУ, что снижает загрузку системной шины. Запись с обратным копированием используется в Pentium.

Микропроцессор Intel 80i86

Архитектура микропроцессора 80i86 (i>3)

Высокопроизводительный 32-х разрядный микропроцессор 80i86 ориентирован на эффективное выполнение программ в среде многозадачных ОС (типа Windows). Микропроцессор имеет 32-разрядные регистры и 32-х разрядные раздельные шины адреса и данных.

Физическое адресное пространство равно 4 Гб (232)

Виртуальное адресное пространство равно 64Тб (246).

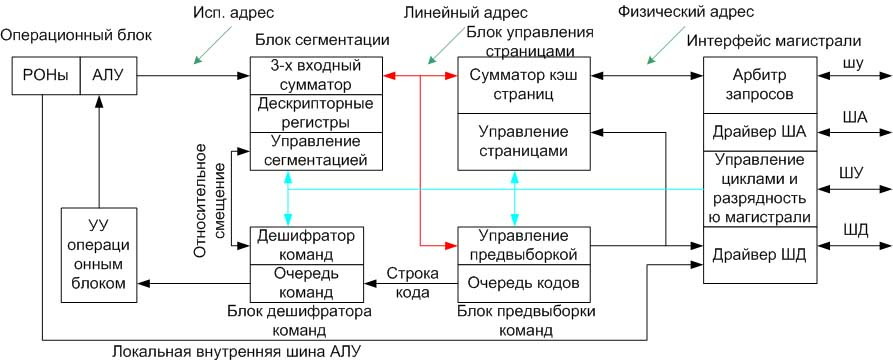

Структурная схема микропроцессора

В состав микропроцессора входят:

-операционный блок;

-блок выборки команд;

-диспетчер памяти;

-устройство управления;

-интерфейс магистрали.

Операционный блок вместе с устройством управления составляют центральный процессор микропроцессора, который предназначен для выполнения всех логических и математических операций. Операционный блок включает в свой состав АЛУ и восемь 32-хразрядных регистров (РОНов). Подсистема выборки команд реализует двухступенчатый алгоритм конвейеризации и состоит из блоков предвыборки команд и дешифрации команд. Блок предвыборки команд принимает команды из интерфейса магистрали, выстраивая их в очередь кодов.

Блок дешифрации команд производит преддешифрацию, то есть, определяет тип и формат команд, определяет номера используемых регистров, выделяет поле относительного смещения и передает его в блок сегментации для вычисления линейного адреса.

Диспетчер памяти состоит из блока сегментации и блока управления страницами, и осуществляет двухступенчатое формирование физического адреса ячейки памяти.

Имеется два режима работы микропроцессора:

а)режим реальных адресов (реальный режим);

б)режим защищенных виртуальных адресов (виртуальный режим).

В реальном режиме микропроцессор 80i86 работает как быстрый микропроцессор 8086. В реальном режиме страничная организация памяти не используется.

В защищенном режиме используются все возможности микропроцессора. При этом возможен многозадачный режим работы микропроцессора, причем каждая задача защищена и изолирована от других задач и от ОС. В защищенном режиме может быть реализована страничная организация виртуальной памяти объемом до 64 Тб для каждой задачи.

Оперативная память состоит из сегментов, каждый из которых может быть разбит на страницы. Каждая страница имеет фиксирующий размер по 4кб каждая страница, причем разбиение памяти на страницы возможно только в защищенном режиме.

Диспетчер памяти (и сегментный, и страничный) служат для вычисления физических адресов при обращении микропроцессора к памяти.

Интерфейс магистрали позволяет осуществить обмен микропроцессора информацией с ОЗУ и ПУ с помощью 32-хразрядной двунаправленной ШД, 34-хразрядной ША и 16-разрядной ШУ. Особенностью ШД является возможность динамического изменения ее разрядности. За один цикл шины может быть переданы 1,2 или 4 байта. По ША передаются 32-х адреса. ША состоит из 30 адресных линий, обозначенных как А31-А2 и 4-х линий выбора байт, обозначенных как ВЕ3-ВЕ0. Сигналы выбора байт определяют какие байты 32-хразрядной шины данных участвуют в текущем цикле обмена. Это позволяет легко согласовать ШД с байтной организацией памяти:

-

При ВЕ0=0

Адресуется младший байт

(т.е.D0-D7 ШД)

При ВЕ1=0

Адресуется следующий байт

(т.е.D8-D15 ШД)

При ВЕ2=0

Адресуется следующий байт

(т.е.D16-D23 ШД)

При ВЕ3=0

Адресуется старший байт

(т.е.D24-D31 ШД)

Регистры

Набор регистров микропроцессора включает:

-РОНы;

-сегментные регистры;

-указатели команд и регистр флагов;

-регистры управления;

-регистры адреса системы;

-регистры отладки;

-регистры тестирования.

Всего микропроцессор содержит 32 регистра, из которых 15 регистров могут адресоваться пользователем, кроме этого имеется указатель команд и 16 системных регистров недоступных пользователю. Все 16-тиразрядные регистры микропроцессоров 8086, 80186, 80286 содержатся в 32-разрядных регистрах микропроцессора 80i386.

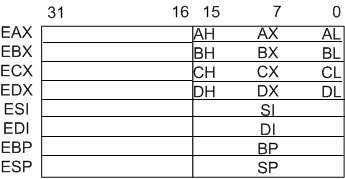

РОНы

Восемь 32-хразрядных РОНов предназначены для хранения операндов и адресов, и располагаются в операционном блоке.

Младшие разряды РОНов (с 0 по 15) доступны отдельно при использовании имен AX, BX, CX, DX, SI, DI, BP, SP. При операциях с байтами для 4-х верхних регистров можно отдельно обращаться к младшему байту по, именам AL, BL, CL, DL и к старшим байтам по именам АН, ВН, СН, DH.

Верхние 4 регистра используются для хранения операндов и позволяют выполнять операции над отдельными байтами, 16-разрядными словами и 32-разрядными двойными словами. Остальные четыре нижних регистра используются как адресные регистры для хранения 16-разрядных и 32-разрядных адресов.

Регистр ESP используется как указатель вершины стека.

EBP – используется как базовый регистр.

А регистры EDI и ESI используются как индексные регистры (для хранения индексов). В качестве базового и индексного регистров в некоторых случаях может использоваться и регистр данных EBX.

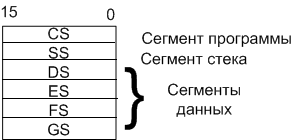

Регистры сегментов и дескрипторов сегментов

А рхитектура

микропроцессора поддерживает организацию

памяти в виде сегментов. Всего имеется

6 сегментных регистров.

рхитектура

микропроцессора поддерживает организацию

памяти в виде сегментов. Всего имеется

6 сегментных регистров.

В реальном режиме: для хранения адресов начала соответствующих сегментов используется 16-хразрядные регистры CS, SS, DS, ES, FS, GS. Они выполняют те же функции, что и в микропроцессоре 8086. то есть, используются при вычислении физических адресов путем суммирования базового адреса, находящегося в сегментном регистре, со смещением. Такое суммирование выполняет блок сегментации, где располагаются и сами сегментные регистры. Максимальный размер сегмента в реальном режиме 64 Кбайт.

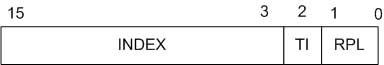

В защищенном режиме содержимое сегментного регистра используется как селектор сегмента. С каждым из сегментных регистров связан регистр дескриптора сегмента. Обращение к дескриптору осуществляется с помощью селектора, который представляет собой 16-хразрядный указатель, имеющий 3 поля.

Биты 0 и1 - это поле RPL, которое определяет уровень привилегий запроса и используется в механизме защиты памяти.

Бит 2 – Это поле TI, которое служит индикатором таблицы. При TI=0 используется глобальная таблица дескрипторов GDT. При TI=1 используется локальная таблица дескрипторов LDT.

Поле INDEX – служит индексом для выбора одного из 8192 дескрипторов (213), содержащихся в таблицах GDT или LDT. Сами 8-мибайтовые дескрипторы хранятся в памяти в составе массивов данных, сформированных в виде таблиц. В микропроцессоре используется 3 таблицы дескрипторов: GDT, LDT и таблица дескрипторов прерывания IDT.

С каждой из таблиц связан соответствующий регистр, который находится в микропроцессоре. Это регистры: GDTR, LDTR и IDTR.

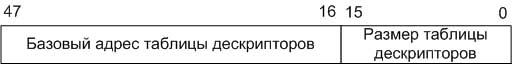

В качестве примера приведем формат регистра GDTR. Регистр GDTR 48-разрядный. 32-разряда задают базовый адрес таблицы дескрипторов, а 16 разрядов указывают размер этой таблицы в байтах.

При обращении селектора к таблице GDT сдвинутый на 3 разряда влево (умноженный на 8) селектор служит в качестве смещения для формирования адреса дескриптора. Это смещение сравнивается с границей (с размером) таблицы дескрипторов, находящейся в разрядах с 0 по 15 регистра GDTR. Если смещение превышает границу, то вырабатывается соответствующее прерывание. Если нарушения границы нет, то смещения суммируются с базовым адресом таблицы дескрипторов. В результате суммирования получается логический адрес младшего байта, выбираемого дескриптора.

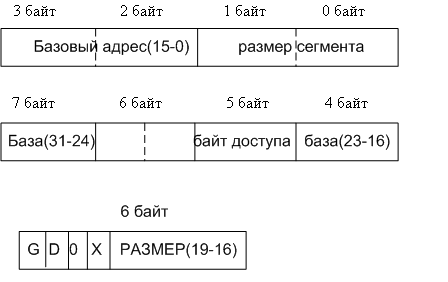

Выбираемый дескриптор имеет следующий формат

32-хразрядный базовый адрес сегмента (база) и 20-тиразрядный размер сегмента размещены по частям в различных байтах дескриптора. Четыре бита 6-го байта определяют следующие атрибуты сегмента:

G – бит дробности, который указывает, в каких единицах задан размер сегмента;

При G = 0 – размер задан в байтах и максимальный объем сегмента в этом случае равен 220 = 1 Мб;

При G = 1 – размер задан в страницах, объемом 4 кб каждая страница. Максимальный объем сегмента в этом случае равен 212 х 220 = 232 = 4 Гб;

D – бит разрядности, который определяет разрядность формируемого относительного адреса или операнда.

При D = 0 – адрес или операнд – 16-тиразрядный;

При D = 1 – адрес или операнд – 32-хразрядный.

53-ий разряд – всегда = 0.

52-ой – имеет произвольное значение Х.

Байт доступа (5-ый) дескриптора определяет право доступа к выбираемому сегменту.

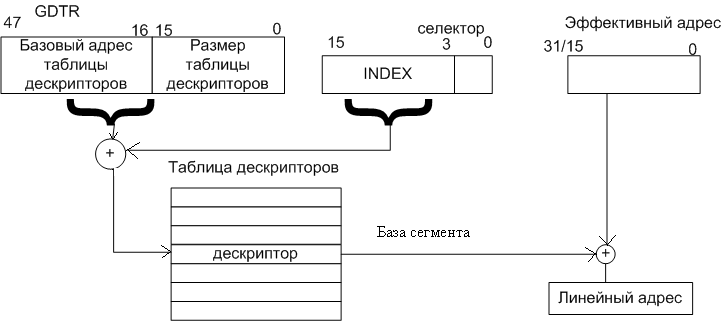

Сегментная организация памяти

В защищенном режиме для формирования линейного адреса используется две компоненты:

1)16-тиразрядный селектор для определения базового адреса сегмента, который содержится в дескрипторе.

2)16 или 32-хразрядный эффективный адрес, который зависит от режима работы и способа адресации.

Проиллюстрируем процесс вычисления линейного адреса с помощью следующей схемы:

Для получения линейного адреса базовый адрес сегмента, содержащийся в дескрипторе, суммируется с эффективным адресом.

При отсутствии страничной организации памяти линейный адрес является физическим адресом для обращения к элементу памяти.