- •История развития архитектуры эвм

- •Нулевое поколение (1492 – 1945)

- •Первое поколение (1937-1953)

- •Второе поколение (1954 - 1962)

- •Третье поколение (1963-1972)

- •Четвертое поколение (1972-1984)

- •Пятое поколение (1984-1990)

- •Шестое поколение (1990-)

- •Концепция машины с хранимой в памяти программой

- •Принцип двоичного кодирования

- •Принцип программного управления

- •Принцип однородности памяти

- •Принцип адресности

- •Типы структур вычислительных машин и систем

- •Структуры вычислительных машин

- •Структуры вычислительных систем

- •Процессор. Структурная схема процессора. Понятие о микропрограммном управлении Структурная схема процессора

- •Алгоритмы выполнения операций. Микропрограммы

- •Синтез микропрограммного автомата. Синтез устройства управления

- •Обратная структурная таблица

- •Управляющие автоматы с программируемой логикой

- •Адресная структура памяти

- •Принципы построения устройств памяти

- •Адресная, ассоциативная и стековая организация памяти

- •Адресная память

- •Ассоциативная память

- •Стековая память

- •Команды процессора

- •Методы повышения производительности работы процессора

- •1.Конвейеризация (конвейер операций)

- •2. Процессоры с risc – архитектурой

- •3. Организация кэш-памяти

- •3.1. Техническая идея кэш-памяти

- •3.2. Архитектура кэш-памяти

- •3.2.1. Кэш память с прямым отображением

- •3.2.2. Полностью ассоциативная кэш память

- •3.2.3. Частично ассоциативная кэш память

- •3.3 Алгоритм замещения строк в кэш памяти

- •3.4 Методы записи в кэш память

- •Микропроцессор Intel 80i86

- •Страничная организация памяти

- •Буфер ассоциативной трансляции

- •Организация виртуальной памяти

- •Встроенные средства защиты информации в микропроцессорах фирмы intel

- •1. Концепции и компоненты защищенного режима

- •Независимость подготовки пользовательских программ и их защита от взаимных помех.

- •Защита программ операционной системы от помех при сбоях в программах пользователей.

- •Защита программ ос верхнего уровня от помех при сбоях в программах ос нижнего уровня.

- •Защита программ от отрицательных последствий при программных сбоях.

- •Защита целостности функционирования вычислительной системы.

- •2. Информационная основа работы механизма защиты

- •3. Уровни привилегий

- •Концепция уровней привилегий.

- •Задание уровней привилегий.

- •Проверка корректности использования отдельных команд.

- •Защита данных.

- •4.3 Защита программ.

- •Принципы организации системы прерывания

- •Программируемый контроллер прямого доступа к памяти

- •Лабораторная работа №1

- •Размещение байт и слов в памяти.

- •Лабораторная работа №2

- •Список операций

Синтез микропрограммного автомата. Синтез устройства управления

В

процессе синтеза микропрограмм автомата

(МПА) первоначально по графу микропрограммы

(МП) определяются множества состояний

А, входных Х и выходных У сигналов

автомата. Для МПА входными являются

сигналы, анализируемые в условных

вершинах графа МП. Т е в нашем примере

множество Х={f,

α, X3}.

Выходными сигналами являются сигналы

микроопераций. В примере: У={У1,…,У10}. Для

определения множества состояний А={![]() }

строится отмеченный граф МП, т е граф,

помеченный символами состояний автомата.

Для МПА отметками состояний помечаются

входы вершин, следующие за операторными

вершинами. При этом символом начального

состояния

}

строится отмеченный граф МП, т е граф,

помеченный символами состояний автомата.

Для МПА отметками состояний помечаются

входы вершин, следующие за операторными

вершинами. При этом символом начального

состояния

![]() помечается выход начальной и вход

конечной вершины графа МП. (В примере

А={

помечается выход начальной и вход

конечной вершины графа МП. (В примере

А={![]() }).

}).

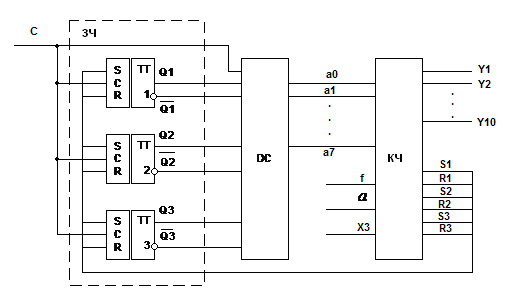

Структурная схема МПА включает запоминающую часть (ЗЧ), дешифратор состояний(ДС) и комбинационную часть(КЧ).

ЗЧ

представляет собой набор двоичных

элементов памяти, в качестве которых

используются триггера различных типов.

В рассматриваемом примере используются

синхронные двухступенчатые RS-триггера.

Минимально необходимое число триггеров

определяется из отношения R=]![]() [, где m+1

– число состояний автомата, ][ - операция

округления до ближайшего большего

целого. В нашем случае количество

состояний МПА=8, R=3.

Таким образом ЗЧ состоит из 3х триггеров,

состояния которых обозначим через Q1,

Q2,

Q3.

При синтезе МПА каждое состояние из

множества А кодируется определенным

набором состояний триггеров. Вариант

кодирования представлен в следующей

таблице:

[, где m+1

– число состояний автомата, ][ - операция

округления до ближайшего большего

целого. В нашем случае количество

состояний МПА=8, R=3.

Таким образом ЗЧ состоит из 3х триггеров,

состояния которых обозначим через Q1,

Q2,

Q3.

При синтезе МПА каждое состояние из

множества А кодируется определенным

набором состояний триггеров. Вариант

кодирования представлен в следующей

таблице:

|

Qr ai |

Q1 |

Q2 |

Q3 |

|

|

a0 |

0 |

0 |

0 |

|

|

a1 |

0 |

0 |

1 |

|

|

a2 |

0 |

1 |

0 |

|

|

a3 |

0 |

1 |

1 |

|

|

a4 |

1 |

0 |

0 |

|

|

a5 |

1 |

0 |

1 |

|

|

a6 |

1 |

1 |

0 |

|

|

a7 |

1 |

1 |

1 |

|

|

|

|

|

|

|

Сигналы

с выхода триггеров ЗЧ поступают на входы

ДС, формирующего сигналы состояний

![]() автомата.

автомата.

КЧ

в зависимости от состояния автомата и

входных сигналов вырабатывает управляющие

сигналы микроопераций

![]() и сигналы возбуждения триггеров

и сигналы возбуждения триггеров

![]() .

На синхровходы триггеров и ДС поступают

синхронизирующие сигналы С, период

следования которых определяет такт

работы автомата. В каждом такте по

сигналу С формируются выходные сигналы

КЧ, а по окончании сигнала С триггера

переключаются в новое состояние. При

построении КЧ удобно задавать работу

автомата с помощью обратной структурной

таблицы, представляющей собой список,

в котором для каждого возможного перехода

в автомате отводится одна строка. Такая

таблица строится по отмеченному графу

МП в виде массивов путей переходов в

отдельное состояние.

.

На синхровходы триггеров и ДС поступают

синхронизирующие сигналы С, период

следования которых определяет такт

работы автомата. В каждом такте по

сигналу С формируются выходные сигналы

КЧ, а по окончании сигнала С триггера

переключаются в новое состояние. При

построении КЧ удобно задавать работу

автомата с помощью обратной структурной

таблицы, представляющей собой список,

в котором для каждого возможного перехода

в автомате отводится одна строка. Такая

таблица строится по отмеченному графу

МП в виде массивов путей переходов в

отдельное состояние.