- •Комбинационные логические схемы

- •Общие сведения

- •Операцию вычитания можно представить в виде

- •Предварительное задание к эксперименту

- •Порядок выполнения эксперимента

- •Содержание отчета

- •Контрольные вопросы

- •Исследование триггерных схем

- •Общие сведения

- •Предварительное задание к эксперименту

- •Порядок выполнения эксперимента

- •Содержание отчета

- •Контрольные вопросы

- •Счетчики импульсов и регистры

- •Общие сведения

- •Предварительное задание к эксперименту

- •Порядок выполнения эксперимента

- •Содержание отчета

- •Контрольные вопросы

- •Общие сведения

- •Предварительное задание к эксперименту

- •Порядок выполнения эксперимента

- •Содержание отчета

- •Контрольные вопросы

Содержание отчета

1. Цель работы.

2. Таблицы истинности дешифратора и мультиплексора.

3. Составленные в предварительном задании схемы включения дешифратора с временными диаграммами.

4. Результаты сложения вычитания и сравнения заданных чисел А и В.

5. Схема сигнализации нулевого результата сумматора.

Контрольные вопросы

1. Чем отличаются КЛС от ЛЭ? Дайте сравнительный анализ на конкретных примерах.

2. Объясните назначение и области применения дешифратора.

3. Каков принцип работы исследуемого дешифратора?

4. Каким образом с помощью мультиплексора можно обеспечить постоянный обегающий контроль 6 различных каналов или выходов ЛЭ?

5. Равноценны ли по своему функциональному назначению управляющие входы дешифратора и адресные входы мультиплексора?

6. Объясните принцип действия сумматора.

7. Как реализуется вычитание двоичных чисел?

Л а б о р а т о р н а я р а б о т а № 8

Исследование триггерных схем

Цель работы: изучение схем и функциональных возможностей основных типов триггеров; экспериментальное изучение триггеров и схем управления.

Общие сведения

Триггерами называют электронные устройства, обладающие двумя состояниями устойчивого равновесия и способные под воздействием управляющего сигнала переходить скачком из одного состояния в другое. Каждому состоянию триггера соответствует определенный (высокий или низкий) уровень выходного напряжения, который может сохраняться как угодно долго. Поэтому триггеры относятся к цифровым автоматам с памятью. В настоящее время триггеры выполняются на основе логических элементов в виде интегральных микросхем (ИМС). Они включены почти во все серии ИМС.

Триггеры применяются как переключающие элементы самостоятельно или входят в состав более сложных цифровых устройств, таких как счетчики, делители частоты, регистры и др.

В

общем случае триггер имеет два выхода:

прямой Q

и инверсный

![]() ,

сигналы на которых противоположны по

уровню. Количество входов триггера

зависит от его типа. Входы делятся на

информационные и командные.

,

сигналы на которых противоположны по

уровню. Количество входов триггера

зависит от его типа. Входы делятся на

информационные и командные.

По способу записи информации триггеры делятся на асинхронные, у которых информационные и командные входы совмещены, и синхронные или тактируемые. Последние срабатывают только при поступлении на один из командных входов (синхровход) разрешающего импульса.

По числу ступеней триггеры делятся на однотактные и двухтактные. В однотактных информация на выходах появляется практически одновременно с приходом информационного или синхроимпульса. Такие схемы срабатывают по перепаду сигнала 0-1 (по фронту синхроимпульса). В двухтактных триггерах переключение элементов происходит в два приема и сигнал на выходе появляется с задержкой. Они срабатывают по перепаду сигнала 1-0 (по спаду импульса).

В зависимости от логической структуры схемы управления различают RS-, D-, T-, JK-триггеры и др.

Работа триггера может быть описана логическим уравнением, связывающим состояние входов и выходов триггера до его срабатывания (t) и после срабатывания (t + 1). Состояние триггера можно задать таблицей переходов или временной диаграммой его работы.

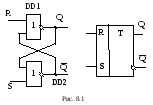

Асинхронный

RS-триггер

имеет два установочных входа R

и S.

Схема триггера на ЛЭ 2ИЛИ-НЕ и его условное

обозначение показаны на рис. 8.1. При S

= R = 0 схема

устойчива. Это режим хранения информации.

Если Q =

1, то на входах DD2

оказываются 1 и 0, при которых

![]() = 0.

= 0.

R

На

входах DD1–0,

0, что сохраняет этот элемент в состоянии

Q

= 1.

Для изменения состояния триггера на

его входы надо подать комбинацию сигналов

R

=

1, S

=

0. Тогда на входе DD1

появится высокий уровень и этот элемент

перейдет в состояние Q

=

0. На входах DD2

установятся сигналы 0, 0, и логический

элемент перейдет в состояние Q

=

1. Комбинация S

=

1, R

=

0 возвратит триггер в состояние Q

=

1,

![]() = 0. При комбинации S

=

1, R

=

1 состояние триггера неопределенно, эта

комбинация запрещена. Работа триггера

иллюстрируется таблицей переключений

(табл. 8.1). Триггер с таким же законом

работы можно выполнить на логических

элементах 2И-НЕ.

= 0. При комбинации S

=

1, R

=

1 состояние триггера неопределенно, эта

комбинация запрещена. Работа триггера

иллюстрируется таблицей переключений

(табл. 8.1). Триггер с таким же законом

работы можно выполнить на логических

элементах 2И-НЕ.

Т а б л и ц а 8.1

|

R |

S |

Qt+1 |

|

1 |

0 |

0 |

|

0 |

1 |

1 |

|

0 |

0 |

Qt |

|

1 |

1 |

X |

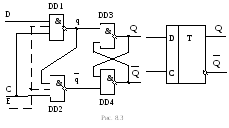

Синхронные

RS-триггеры

имеют два информационных входа R

и S

и синхровход С.

Схема триггера и его условное обозначение

показаны на рис. 8.2. Асинхронный RS-триггер

дополнен схемой управления на ЛЭ DD1-2,

которая формирует сигналы

![]() и

и

![]() ,

поступающие на его установочные входы.

Управление осуществляется низким

уровнем сигнала 0, поэтому на входах

показан знак инверсии. При

,

поступающие на его установочные входы.

Управление осуществляется низким

уровнем сигнала 0, поэтому на входах

показан знак инверсии. При

![]() = 1 любая комбинация

= 1 любая комбинация

![]() и

и

![]() дает на выходах

дает на выходах

![]() 0 и асинхронный триггер на элементах

DD3-4

находится в режиме хранения информации.

Схема управления сработает только при

поступлении низкого уровня на синхровход

(

0 и асинхронный триггер на элементах

DD3-4

находится в режиме хранения информации.

Схема управления сработает только при

поступлении низкого уровня на синхровход

(![]() = 0). Тогда

= 0). Тогда

![]() = 1 и

= 1 и

![]() =

0 приведет к

=

0 приведет к

![]() = 0 и

= 0 и

![]() = 1. Триггер перейдет в состояние

Q

= 1, а при

= 1. Триггер перейдет в состояние

Q

= 1, а при

![]() = 0,

= 0,

![]() = 1 – в состояние Q

= 0. Комбинация

= 1 – в состояние Q

= 0. Комбинация

![]() =

=![]() =

=![]() =

0 запрещена. Так как при

=

0 запрещена. Так как при

![]() =

1 любое изменение сигналов на входах

=

1 любое изменение сигналов на входах

![]() и

и

![]() игнорируется, синхронные триггеры

защищены от воздействия помех.

игнорируется, синхронные триггеры

защищены от воздействия помех.

Синхронный

D-триггер

состоит из асинхронного RS-триггера

и схемы управления на ЛЭ. Он имеет

информационный вход D

и синхровход С.

Его схема и условное обозначение показаны

на рис. 8.3. ЛЭ DD3-4

представляют собой RS-триггер,

управляемый инверсными сигналами. Его

устойчивое состояние обеспечивается

комбинацией

![]() 1.

При С =

0 на выходах обоих ЛЭ И-НЕ DD1-2

независимо от значения сигнала на входе

D

будут поддерживаться высокие уровни и

триггер сохранит предыдущее состояние.

С приходом синхроимпульса С

= 1, при D

= 1

1.

При С =

0 на выходах обоих ЛЭ И-НЕ DD1-2

независимо от значения сигнала на входе

D

будут поддерживаться высокие уровни и

триггер сохранит предыдущее состояние.

С приходом синхроимпульса С

= 1, при D

= 1

![]() = 0, а

= 0, а

![]() = 1, и RS-триггер

оказывается в состоянии Q

= 1. При D

= 0

= 1, и RS-триггер

оказывается в состоянии Q

= 1. При D

= 0

![]() = 1,

= 1,

![]() = 0, и триггер переходит в состояние Q

= 0. Это

значение не может измениться до прихода

следующего синхроимпульса. Поэтому

D-триг-геры

называют триггерами задержки – они

задерживают информацию на такт. На схеме

пунктиром показан вход Е,

объединяющий два дополнительных И-входа.

Этот вход расширяет возможности схемы.

Его называют разрешающим. При Е

= 1 триггер

работает в нормальном режиме, Е

= 0 дает

возможность сохранить информацию при

изменении сигналов на D-

и С-входах.

= 0, и триггер переходит в состояние Q

= 0. Это

значение не может измениться до прихода

следующего синхроимпульса. Поэтому

D-триг-геры

называют триггерами задержки – они

задерживают информацию на такт. На схеме

пунктиром показан вход Е,

объединяющий два дополнительных И-входа.

Этот вход расширяет возможности схемы.

Его называют разрешающим. При Е

= 1 триггер

работает в нормальном режиме, Е

= 0 дает

возможность сохранить информацию при

изменении сигналов на D-

и С-входах.

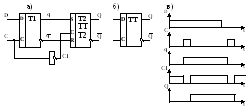

Широкое применение получили двухтактные D-триггеры. Схема и условное обозначение приведены на рис. 8.4, а, б. Он состоит из D-триггера и синхронного RS-триггера с объединенными через инвертор С-входами. Принцип работы триггера можно проследить по временной диаграмме (рис. 8.4, в). Сигнал со входа D записывается в Т1 по фронту синхроимпульса. При этом С1 = 0 и Т2 сохраняет прежнюю информацию. После окончания синхроимпульса С = 0, Т1 отключается от D-входа, С1 = 1 и Т2 переписывает информацию из Т1.

Рис.

8.4

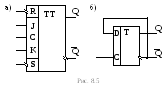

JK-триггер является универсальным. Его условное обозначение приведено на рис. 8.5, а. Он имеет два установочных входа R и S, информационные входы J и K и синхровход С.

У становочные

вхо-ды обладают приоритетом над другими.

С их помощью триггер устанавливают в

состояние Q

= 1 или

Q

= 0 независимо

от сигналов на всех других входах.

становочные

вхо-ды обладают приоритетом над другими.

С их помощью триггер устанавливают в

состояние Q

= 1 или

Q

= 0 независимо

от сигналов на всех других входах.

J- и K-входы работают по разрешающему импульсу на С-входе. При комбинации J = 1 и K = 0 на выходе Q = 1. При J = 0 и K = 1 триггер переходит в состояние Q = 0, а если J = K = 1, то с приходом каждого синхроимпульса он меняет состояние. Работу триггера можно описать логическим уравнением

![]() .

.

На основе JK-триггера можно построить любой другой тип триггера. Поэтому они массово производятся практически во всех сериях ИМС.

Т-триггер или счетный триггер имеет один информационный вход Т. Каждый импульс на этом входе переводит его в новое состояние. Это соответствует работе JK-триггера при K = J = 1.

Такой же триггер можно получить на основе D-триггера (рис. 8.5, б). Поэтому производить Т-триггеры в виде самостоятельных изделий нет смысла и их нет в сериях ИМС.

Т-триггеры используются как делители частоты на 2 или счетчики по модулю 2.