- •Методические указания

- •«Вычислительная техника»

- •2003 «Радиоаппаратостроение»

- •Аннотация.

- •Содержание.

- •Инструкция №1.

- •1. Общие требования безопасности.

- •2. Требования безопасности перед началом работы.

- •3. Требования безопасности во время работы.

- •4. Требования безопасности в аварийных случаях.

- •5. Требования безопасности по окончании работы.

- •Устройства и приборы, используемые при проведении лабораторных работ.

- •1.1 Логический преобразователь (Logic Converter)

- •Логический анализ n- входного устройства с одним выходом

- •Синтез логического устройства по таблице истинности.

- •Синтез логического устройства по булеву выражению.

- •1.2. Функциональный генератор

- •1.3. Логический анализатор (Logic Analyzer)

- •1.4. Генератор слова.

- •Выход тактовых

- •Выходы 16-разрядных слов р ис.1 Схемное изображение генератора слова.

- •Лабораторная работа №1.

- •Цель работы: Ознакомление с панелью программы ewb, изучение устройств и приборов программы ewb.

- •Лабораторная работа №2.

- •Лабораторная работа №3.

- •Лабораторная работа №4.

- •Лабораторная работа №5

- •Лабораторная работа №6.

- •Порядок работы.

- •Лабораторная работа № 7.

- •Лабораторная работа №8.

- •Контрольные вопросы:

- •Лабораторная работа №9.

- •Порядок исследования триггеров.

- •Лабораторная работа №10.

- •Лабораторная работа №11.

- •Лабораторная работа №12.

- •Лабораторная работа №13.

- •Лабораторная работа № 14.

- •Лабораторная работа № 15.

- •Лабораторная работа №16.

- •Лабораторная работа №17.

- •Лабораторная работа №18.

- •Лабораторная работа №19.

- •Список используемой литературы.

Лабораторная работа №8.

Тема: «Исследование сумматоров. Синтез сумматоров на элементах и на микросхемах».

Цель работы: «Исследовать полусумматор, полный сумматор, многоразрядный сумматор. Синтезировать восьмиразрядный сумматор».

Приборы и устройства: персональный компьютер, программа EWB 5.12.

Арифметические

сумматоры являются составной частью

так называемых арифметико-логических

устройств (АЛУ) микропроцессоров (МП).

Они используются также для формирования

физического адреса ячеек памяти в МП с

сегментной организацией памяти. В

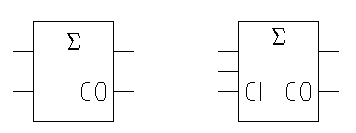

программе EWB арифметические сумматоры

представлены в библиотеке Comb`I двумя

базовыми устройствами, показанными на

рис.1: полусумматором и полным сумматором.

Арифметические

сумматоры являются составной частью

так называемых арифметико-логических

устройств (АЛУ) микропроцессоров (МП).

Они используются также для формирования

физического адреса ячеек памяти в МП с

сегментной организацией памяти. В

программе EWB арифметические сумматоры

представлены в библиотеке Comb`I двумя

базовыми устройствами, показанными на

рис.1: полусумматором и полным сумматором.

Рис.1.

Полусумматор, полный сумматор.

Они имеют следующие назначения выводов: А, В - входы слагаемых, -результат суммирования С0 – выход переноса, СI - вход переноса.

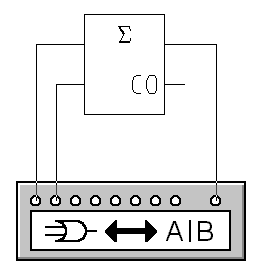

Для исследования внутренней структуры и логики функционирования сумматоров подходит логический преобразователь. После подключения полусумматора к преобразователю согласно рис.2 последовательно нажимая кнопки.

В

результате получаем таблицу истинности

и булево выражение. Сравнивая полученные

данные с результатами исследования

базовых логических элементов в предыдущем

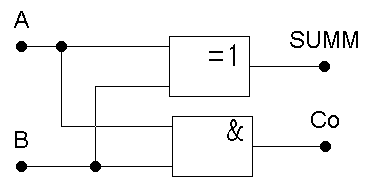

разделе, приходим к выводу, что при

подключении выхода

полусумматора к зажиму OUT преобразователя

(рис.2), он выполняет функции элемента

«Исключающее ИЛИ». Подключив клемму

OUT преобразователя к выходу С0 -

полусумматора и проделав аналогичные

действия приходим к выводу, что в таком

включении полусумматор выполняет

функции элемента И. Следовательно

эквивалентная схема полусумматора

имеет вид, показанный на рис.4

результате получаем таблицу истинности

и булево выражение. Сравнивая полученные

данные с результатами исследования

базовых логических элементов в предыдущем

разделе, приходим к выводу, что при

подключении выхода

полусумматора к зажиму OUT преобразователя

(рис.2), он выполняет функции элемента

«Исключающее ИЛИ». Подключив клемму

OUT преобразователя к выходу С0 -

полусумматора и проделав аналогичные

действия приходим к выводу, что в таком

включении полусумматор выполняет

функции элемента И. Следовательно

эквивалентная схема полусумматора

имеет вид, показанный на рис.4

Рис.3.Исследование

полусумматора. Рис.4. Функциональная схема полусумматора.

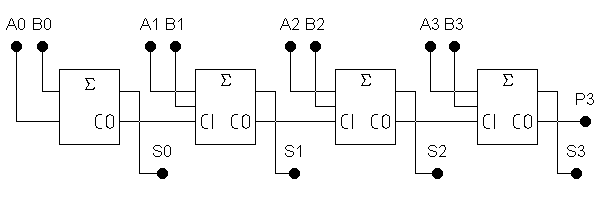

Многоразрядный сумматор создается на базе одного полусумматора и n- полных сумматоров. В качестве примера на рис.5 приведена структура четырехразрядного сумматора. На входы А1, А2, А3, А4 и В1, В2, В3, В4 подается первое и второе слагаемые соответственно, а с выходов S1,S2,S3,S4 снимается результат суммирования также одновременно.

Н

Рис.5.

Схема четырехразрядного полного

сумматора.

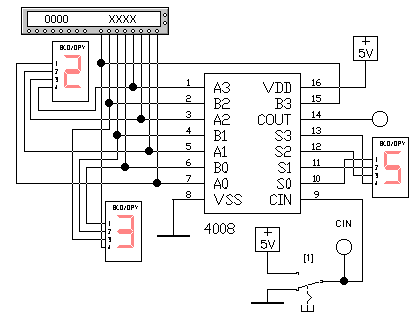

С умматоры

на микросхемах можно соединять друг с

другом, подключая выход COUT

предыдущей микросхемы к входу CIN

последующей. Так из двух микросхем 4008

можно составить восьмиразрядный двоичный

сумматор.

умматоры

на микросхемах можно соединять друг с

другом, подключая выход COUT

предыдущей микросхемы к входу CIN

последующей. Так из двух микросхем 4008

можно составить восьмиразрядный двоичный

сумматор.

Рис.6 Полный сумматор

на

микросхеме 4008 (EWB)

Порядок выполнения работы:

-

Исследуйте полусумматор, используя логический конвертор. Запишите таблицу истинности и логические выражения для сигналов и С0.

-

Выясните внутреннюю структуру полного сумматора, пользуясь схемой его подключения к логическому преобразователю и принимая во внимание методику решения аналогичной задачи для полусумматора.

-

Соберите схему четырехразрядного сумматора из полусумматора и полных сумматоров и исследуйте ее работу при помощи генератора слова трех семисегментных индикаторов для четырехразрядных чисел А, В и их суммы S и одноразрядного индикатора для сигнала переноса p.

-

Соберите схему полного сумматора на микросхеме 4008 рис.6 и исследуйте ее работу. Проверьте работу ИМС 4008 в режиме сумматора с переносом (на вход CIN подайте сигнал логической единицы).

-

Соберите на ИМС 4008 восьмиразрядный сумматор и исследуйте его.