mpusu_avr_p1

.pdf

20.12.2017

Микропроцессорные устройства систем управления

Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» Факультет электротехники и автоматики

Кафедра систем автоматического управления

к.т.н., доцент

Голик Станислав Евсеевич

E-mail: segolik@gmail.com

Тел: (921) 321-0875

2

Голик С.Е.

1

20.12.2017

Микропроцессорные устройства систем управления

Литература:

1.Голик С. Е. Микроконтроллеры для систем управления: Учеб. пособие. СПб.: Изд-во СПбГЭТУ «ЛЭТИ», 2015. 160 с.

2.Евстифеев, А.В. Микроконтроллеры AVR семейства Mega: руководство пользователя/ А.В. Евстифеев. – М.: ДМК Пресс, Додэка, 2015.

3. Микропроцессорные системы: Учеб. пособие для вузов / Е. К. Александров, Р. И. Грушвицкий, М. С. Куприянов и др.: Под общ. ред. Д. В. Пузанкова. СПб.: Политехника, 2002.

4.Мортон, Д. Микроконтроллеры AVR: ввод. курс: пер. с англ. / Д. Мортон. – М.:

ДОДЭКА-21, 2006.

3

Голик С.Е.

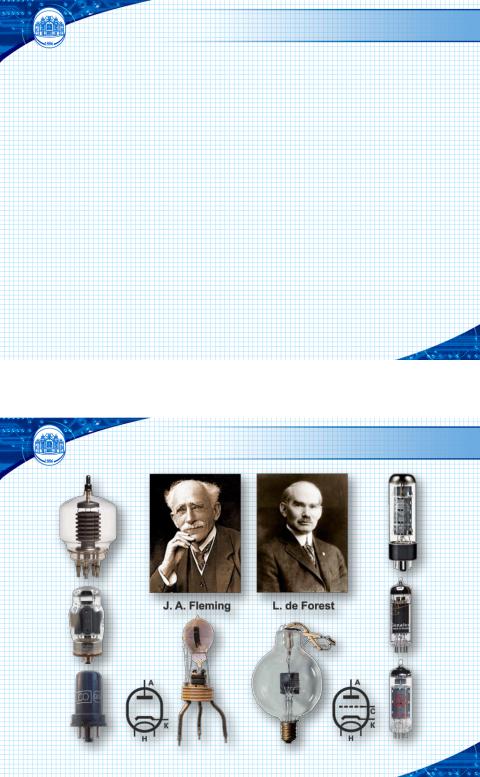

Электронные лампы

История изобретения и использования

4

Голик С.Е.

2

20.12.2017

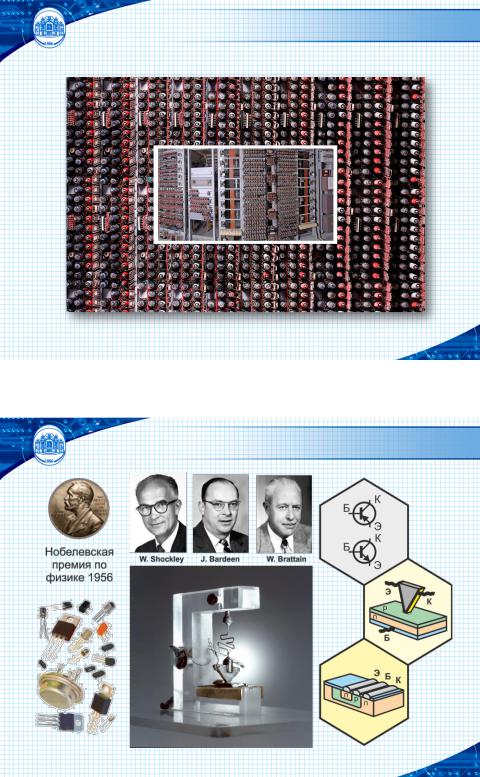

ЭВМ на электронных лампах

5

Голик С.Е.

Транзистор

6

Голик С.Е.

3

20.12.2017

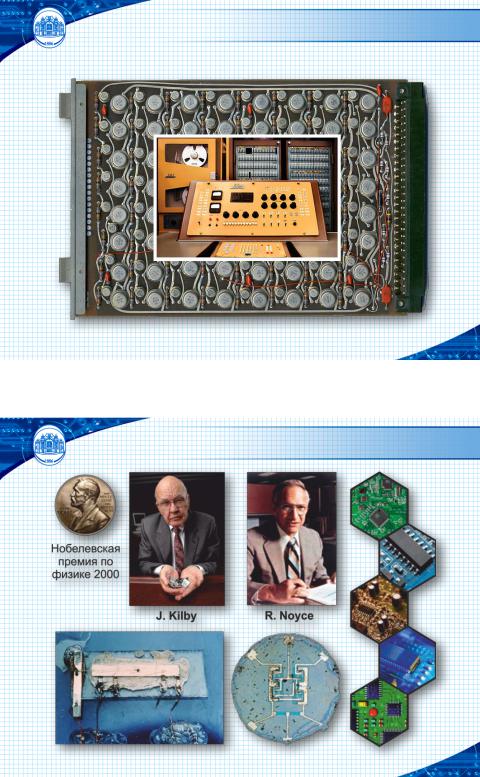

ЭВМ на транзисторах

7

Голик С.Е.

Микросхема

8

Голик С.Е.

4

20.12.2017

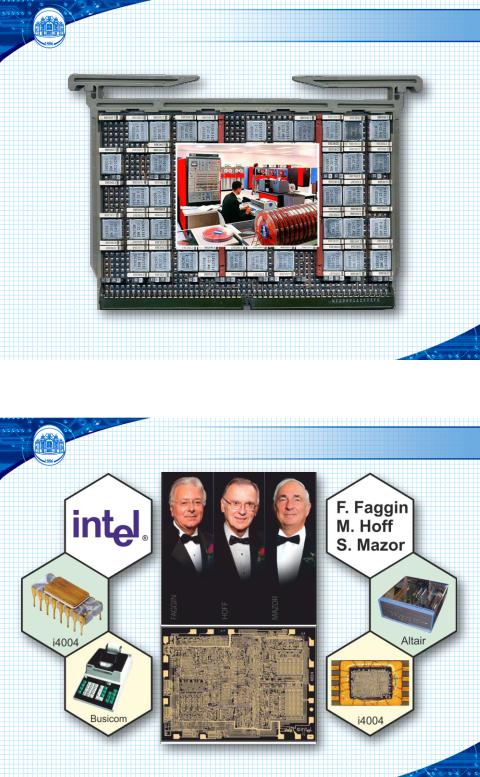

ЭВМ на микросхемах

9

Голик С.Е.

Микропроцессор

10

Голик С.Е.

5

20.12.2017

Современный компьютер

11

Голик С.Е.

Архитектура микроконтроллеров

Определение микроконтроллера

Микроконтроллер – это реализованное в виде одной интегральной схемы программируемое вычислительное устройство, включающее в свой состав процессорное ядро для производства вычислений и набор периферийных модулей для реализации различных функций контроля и управления

12

Голик С.Е.

6

20.12.2017

Архитектура микроконтроллеров

Магистрально-модульная организация

Типовая структура микроконтроллера

13

Голик С.Е.

Архитектура микроконтроллеров

Определение архитектуры

Понятие архитектуры микроконтроллеров отражает следующие наиболее важные компоненты:

•структуру МК как совокупность модулей и связей между ними;

•систему команд и форматы их представления;

•организацию памяти и структуру адресного пространства;

•способы представления данных;

•способы обращения ко всем элементам структуры (адресация к регистрам, ячейкам постоянной и оперативной памяти, функциональным модулям и внешним устройствам);

•систему обработки прерываний.

14

Голик С.Е.

7

20.12.2017

Архитектура микроконтроллеров

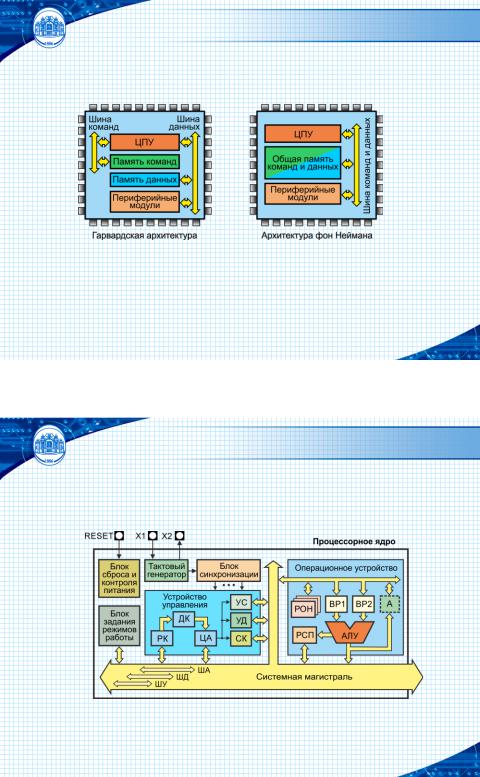

Классификация архитектур

По организации пространства памяти:

•гарвардская архитектура с раздельной памятью команд и данных;

•архитектура фон Неймана с общей памятью для команд и данных

По организации системы команд:

•CISC – архитектура с расширенным набором команд, включающем большое число достаточно сложных команд с развитыми возможностями адресации;

•RISC – архитектура с сокращенным набором команд фиксированной длины и выполнением команд за один машинный цикл

15

Голик С.Е.

Архитектура микроконтроллеров

Процессорное ядро

Процессорное ядро (MCU – Microcontroller Core Unit) является основным узлом любого микроконтроллера, предназначенным для выполнения вычислительных операций и координации работы всех остальных модулей микроконтроллера.

16

Голик С.Е.

8

20.12.2017

Процессорное ядро

Операционное устройство

Операционное устройство выполняет одну из главных функций микроконтроллера – арифметическую и логическую обработку данных в соответствии с командами прикладной программы. Основным узлом операционного устройства, выполняющим эту обработку, является арифметико-логическое устройство - АЛУ.

Основные регистры:

•регистры общего назначения (РОН);

•регистр состояния программы (РСП).

Типовые флаги регистра состояния программы:

•флаг переноса, который устанавливается в 1, если в результате выполнения операции произошел перенос из старшего разряда результата;

•флаг дополнительного переноса, который равен 1, если в результате выполнения операции

произошел перенос из младшей тетрады результата в старшую;

•флаг переполнения, который устанавливается в 1, если в результате выполнения арифметической операции произошло переполнение разрядной сетки результата;

•флаг нуля, в который заносится 1, если результат операции равен 0;

•флаг знака результата, который дублирует знаковый разряд результата операции;

•флаг четности, который равен 1, если число единиц в результате операции четно.

17

Голик С.Е.

Процессорное ядро

Устройство управления

Устройство управления обеспечивает выполнение последовательности микроопераций по коду текущей команды и организует выборку команд в соответствии с программой. Его основной функцией является превращение исходного кода команды в последовательность управляющих воздействий для АЛУ, внутренних регистров и регистрового файла, которая приводит к выполнению команды. Помимо этого, устройство управления координирует работу МК, поддерживая требуемую последовательность работы всех остальных его узлов.

Основные блоки устройства управления:

•дешифратор команд (ДК), который по зафиксированному в регистре команд (РК) коду команды определяет вид операции, число байтов в команде, адреса операндов, участвующих в операции, а также используемые способы адресации операндов;

•цифровой автомат (ЦА), который по полученному от дешифратора команд расширенному

коду формирует с каждым очередным тактом синхронизации необходимый для выполнения команды набор управляющих сигналов.

Основные регистры устройства управления:

•регистр счетчика команд (СК);

•регистр указателя стека (УС);

•регистр указателя данных (УД).

18

Голик С.Е.

9

20.12.2017

Процессорное ядро

Тактовый генератор и блок синхронизации

Тактовый генератор вырабатывает периодический сигнал, на основе которого блок синхронизации формирует синхронизирующие импульсы для процессорного ядра и периферийных модулей.

Типы времязадающих цепочек:

•кварцевые резонаторы – для формирования сигналов высокой стабильности (погрешность – сотые – тысячные доли процента) в диапазоне частот от десятков килогерц до десятков мегагерц;

•пьезокерамические резонаторы – для формирования сигналов средней стабильности

(погрешность – десятые доли процента) в диапазоне частот от десятков килогерц до единиц мегагерц;

•LC-цепочки – для формирования сигналов средней стабильности (погрешность – десятые доли – единицы процентов) в диапазоне частот от единиц до сотен килогерц;

•RC-цепочки – для формирования сигналов низкой стабильности частоты (погрешность – единицы процентов) в диапазоне частот от единиц до сотен килогерц.

19

Голик С.Е.

Процессорное ядро

Блок задания режимов

Блок задания режимов работы позволяет переводить МК в один из энергосберегающих режимов работы

Помимо основного режима работы в МК реализованы различные режимы энергосбережения, среди которых можно выделить два наиболее распространенных:

•режим ожидания (Wait, Idle или Halt mode)

•процессорное ядро отключено от тактового генератора

•системные и периферийные модули включены

•выход из режима - по прерыванию или сбросу

•снижение мощности в 5-10 раз

•режим останова (Stop, Sleep или Power Down mode)

•тактовый генератор отключен

•системные и периферийные модули отключены

•выход из режима - по прерыванию или сбросу

•снижение мощности до нескольких микроватт

20

Голик С.Е.

10