Схемотехника / Учебники и методички / lect16_m5_vt_vt_aloiscevm_niy06

.pdf

a |

|

b |

4 |

6 |

2 |

|

7 |

3 |

|

5 |

|

0 |

1 |

|

|

p |

|

|

|

|

|

а |

б |

|

|

|

|

|

в |

|

|

г |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

д |

е |

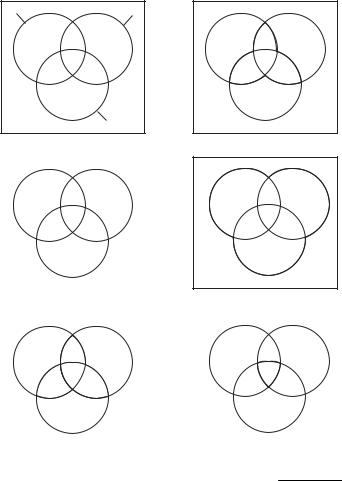

Рис.7.7. Диаграммы Венна: а - для трёх переменных; б - для функции ab + ap + bp; в - для функции S; г - для a + b + p; д - для ab ap bp ; e - для abp

Схема сумматора, реализованного по уравнениям (7.7) и (7.10), приведена на рис.7.8,а. В данной схеме используются многовходовые логические элементы И и ИЛИ. Если использовать только двухвходовые элементы, то получаются схемы, приведённые на рис.7.8,б и в.

a |

& |

1 |

|

a |

& |

b |

|

|

b |

||

p |

|

|

|

|

|

|

& |

|

|

|

1 |

|

& |

|

|

S |

|

|

& |

|

|

p |

& |

|

& 1 |

1 |

a |

|

|

|

|

|

& |

||

|

& |

|

|

P b |

|

|

|

|

|

||

|

& |

|

|

|

1 |

|

а |

|

|

p |

& |

|

|

|

|

||

|

|

|

|

|

|

& |

|

1 |

S |

1 |

& |

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

P |

|

б |

|

|

1 |

& |

1 |

S |

& |

|

|

|

1 |

1 |

|

|

|

|

P |

|

|

|

|

|

|

в |

|

|

Рис.7.8. Рациональные схемы полного двоичного сумматора: а - на многовходовых элементах; б, в - на двухвходовых элементах

5. Накапливающие сумматоры

Накапливающие сумматоры могут строиться двумя способами:

•с использованием счётных триггеров;

•по структуре комбинационный сумматор плюс регистр хранения. Первый способ в настоящее время практически не применяется

вследствие двухтактности операции сложения, низкой скорости распространения сигналов переноса и сложности управления сумматором.

Во втором случае можно реализовать две схемы:

•с запоминанием результата операции S = А плюс В;

•с накоплением результата S = S плюс А.

На рис.7.9 приведена схема четырёхразрядного параллельного накапливающего сумматора, выполненного по структуре комбинацион-

ный сумматор плюс регистр хранения (на часть схемы, нарисованную штриховой линией пока не следует обращать внимание). Число с выхода регистра подаётся на входы В сумматора, поэтому здесь реализуется микрооперация S = S плюс А.

Если схему дополнить вентилем И, нарисованным штриховой линией, то она может использоваться в качестве «делителя частоты», для которого в общем случае можно записать

fвых fвх A / 2n ,

где А - десятичный эквивалент двоичного кода числа А; n - разрядность сумматора.

Термин «делитель частоты» указан в кавычках, чтобы подчеркнуть тот факт, что выходные импульсы расставляются им неравномерно (равномерная расстановка импульсов обеспечивается только для значений А, являющихся степенью двойки). Временные диаграммы для рассматриваемой схемы при различных значениях А приведены на рис.7.10.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

SM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

b1 |

|

S0 |

|

|

|

|

|

|

|

|

|

|

b2 |

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

b3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a0 |

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

||||

|

a2 |

|

S3 |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

a3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pвх= 0 |

|

p |

|

P |

|

|

|

|

|

|||

|

|

|

P3 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

ТИ(fвх)

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c1 |

|

|

|

|

|

|

|

|

|

|

|

|

RG |

|

|

|

|

|

|

|

|||

|

|

c2 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

Q0 |

|

|

|

|

|

S0 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

DR |

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

Q1 |

|

|

|

|

|

||

«1» |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||||

V |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Q2 |

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

D0 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Q3 |

|

|

|

|

|

S3 |

|

|

|

D1 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||

|

|

D2 |

|

|

|

|

|

|

|

|

|

|

|

|

D3 |

ИР1 |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fвых |

|

& |

|

|

||||||

|

|

|||||||

|

|

|

|

|

|

|

|

|

Рис.7.9. Накапливающий сумматор, выполняющий микрооперацию S=S плюс A и функцию «делителя частоты»

Кроме использования сумматоров по их прямому назначению, они широко применяются при построении самых различных схем, узлов и

операционных блоков. Сумматор является ядром АЛУ, выпускаемого в виде специализированной ИС, причём само АЛУ является ядром процессорных элементов. Чрезвычайно широкое применение находят четвертьсумматоры («элементы сумма по mod 2»), реализуемые во многих сериях. Отметим еще несколько примеров использования сумматоров: двоично-десятичные сумматоры, инкременторы и декременторы, цифровые матричные умножители, цифровые фильтры, преобразователи кодов, счётчики и пересчётные устройства, пороговые схемы, линейные цифровые автоматы и др.

ТИ

A=1

2

3  4

4

5

5  6

6

7

7  8

8

9

9

10

11

11  12

12

13

13  14

14

15

15

Рис.7.10. Временные диаграммы для «делителя частоты», реализованного на четырёхразрядном накапливающем сумматоре