Схемотехника / Учебники и методички / LAB01PR

.pdf

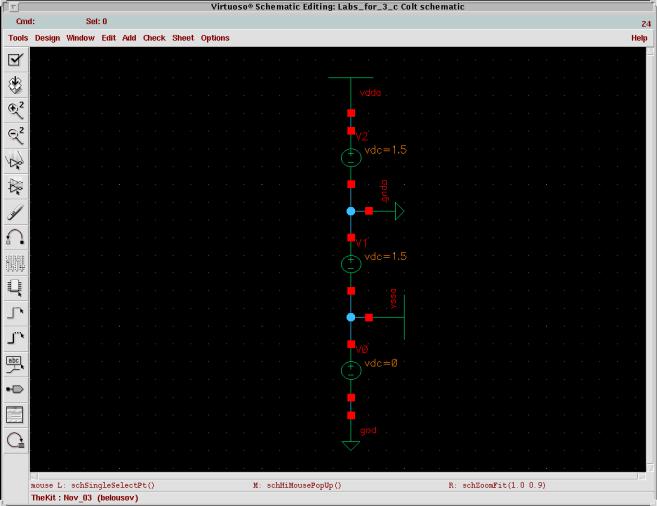

Рис. 14 – Блок источников питания для моделирования

3.Сохранение схемы

Шаг 13: В окне Virtuoso Schematic Editing выберите пункт меню

Design…→Check and Save или нажмите <Shift> + x. Исправьте все ошибки в нарисованной Вами схеме: описание ошибок (error) и предупреждений (warning) можно найти в Окне командного интерпретатора CIW. Редактирование свойств и параметров объекта – выберите изменяемый элемент, далее меню Edit Properties Objects… По окончании редактирования нажмите OK.

4. Моделирование схемы пассивного фильтра низких частот первого порядка в частотном режиме, определение частоты среза фильтра

Шаг 14: В окне Virtuoso Schematic Editing выберите пункт меню Tools…→Analog Enviroment, появится показанное на Рис. 15 окно диалога для проведения моделирования.

11

Рис. 15 – Окно диалога для проведения моделирования Analog Design Environment

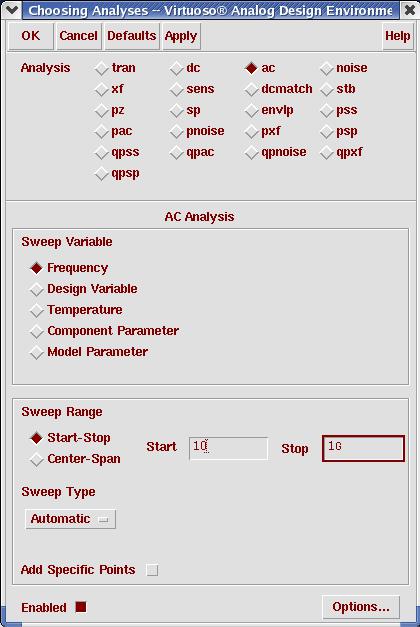

Шаг 15: В окне Virtuoso Analog Design Environment выберите пункт меню

Analysis…→Choose…, и заполните всплывающее диалоговое окно как показано на Рис. 16, затем нажмите OK.

Параметры моделирования для AC Analysis:

Sweep Variable: Frequency (параметр, по которому идет моделирование)

Sweep Range: Start-Stop, Start: 10, End: 1G (начальная и конечная частота)

12

Рис. 16 – Настройка частотного моделирования (AC Analysis)

Шаг 16: В окне Analog Design Environment выберите пункт меню

Simulation…→Netlist and Run.

Шаг 17: В окне Analog Design Environment выберите пункт меню

Session…→Options… В всплывающем окне измените опцию Waveform tool на AWD и

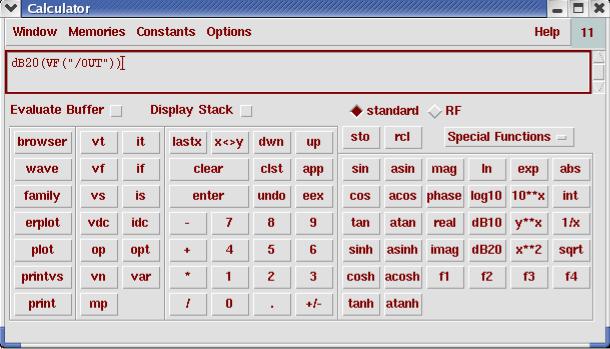

нажмите OK. Затем выберите пункт меню Tools…→Calculator. Для формирования выражения для вывода графика выходного сигнала необходимо выбрать пункт vf в

калькуляторе, затем выбрать на схеме узел, график напряжения которого требуется,

.Выражение dB20(VF(“/OUT”)) (см. Рис. 17) соответствует напряжению (в децибелах) на выходе фильтра. При нажатии Plot в отдельном окне будет выведен график АЧХ. Для

13

вывода ФЧХ воспользуйтесь функцией калькулятора phase, при этом выражение в строке ввода калькулятора примет вид phase(VF(“/OUT”)), затем Plot, после в окне графика нажмите Switch Axis Mode. Итоговый график приведен на Рис. 18. Формулу из строки ввода калькулятора можно видеть в подписи к графику на Рис. 18.

Рис. 17 – Калькулятор

14

Рис. 18 – График, полученный в результате проведения частотного анализа

Чтобы найти граничную частоту, необходимо включить курсор кнопкой «Crosshair Marker A», далее перемещая его мышкой вдоль кривой АЧХ и наблюдая за значениями в появившемся окошке, найти значение амплитуды выходного сигнала, равное –3 дБ.

Значение частоты в этой точке будет равно граничной частоте фильтра. Сохранить АЧХ (с

курсором на частоте среза) и ФЧХ схемы для отчета. Для сохранения графика необходимо нажать <Ctrl> + <Alt>, чтобы сделать окно виртуальной машины неактивным, затем сделать снимок экрана клавишей <PrtScrn> и вставить изображение в графический редактор.

Шаг 18: После проведения моделирования и сохранения результатов, закройте окно Analog Design Environment, и в возникшем окне для сохранения параметров моделирования нажмите Yes, введите название набора параметров (поле Save As), затем нажмите Ok. В дальнейшем, при повторном моделирования схемы, Вы можете вызвать сохранѐнный набор параметров моделирования путѐм выполнения команды

Session→Load State…

Шаг 19: Далее необходимо получить реакцию пассивного RC-фильтра на ступенчатый входной сигнал. Для этого необходимо подать на вход фильтра ступенчатый

15

сигнал из источника vpulse (из библиотеки analoglib) с параметрами: Voltage 1=200 mV, Voltage 2=-200 mV, Rise Time=Fall time=1 ns.

Pulse Width =50 us, Period=100 us.

Параметры для временного анализа (Transient):

Stop Time: 100us (конечное время моделирования),

Accuracy defaults: conservative.

5.Создание операционного усилителя (схемы и символа)

Для того чтобы собирать последующие схемы, необходимо сперва создать операционные усилители – полностью дифференциальный и неполностью дифференциальный.

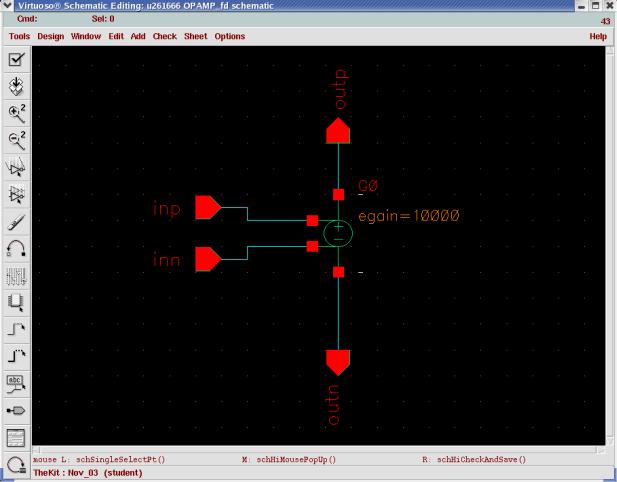

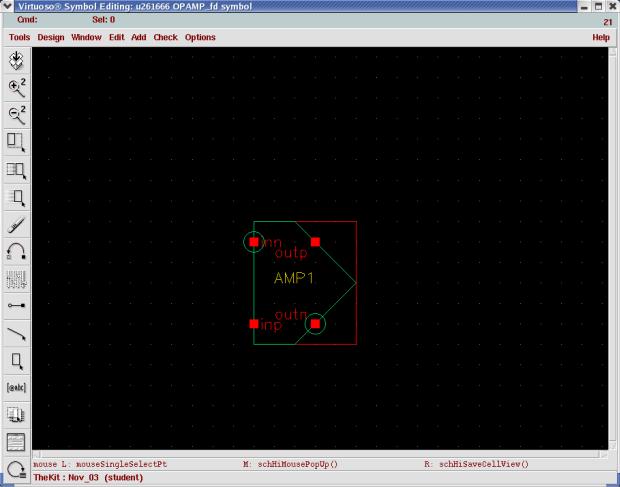

Шаг 1: Создайте в вашей библиотеке новый файл CellView с именем OPAMP_fd и

соберите схему, представленную на Рис. 19. Элемент VCVS находится в библиотеке analogLib. Параметр Voltage gain принять равным 10000.

Рис. 19 – Источник напряжения управляемый напряжением, используемый в качестве полностью дифференциального ОУ

16

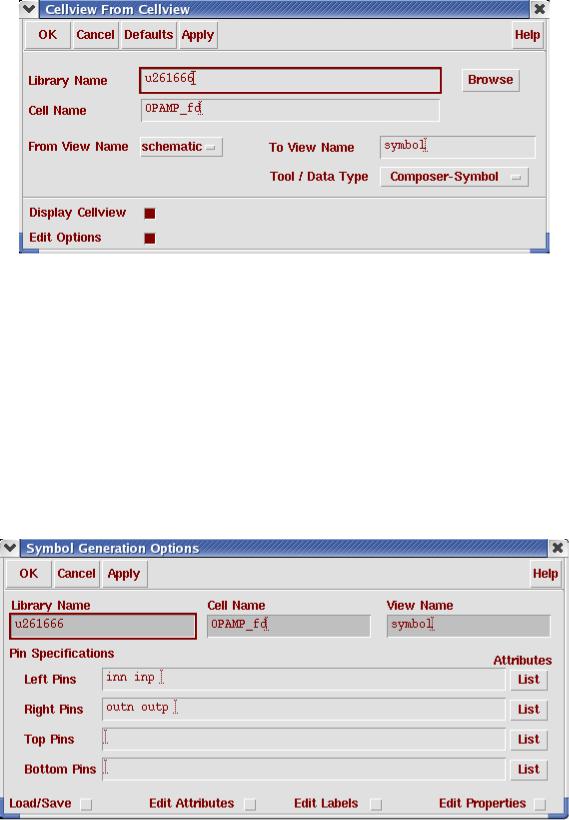

Шаг 2: В окне Virtuoso Schematic Editing выберите Design…→Create Cellview→From Cellview, и появится следующее всплывающее окно (Рис. 20).

Рис. 20 – Всплывающее окно “Cellview From Cellview”

Шаг 3: Проверьте названия представлений схемы (schematic – электрическая схема и symbol – изображение символа, соответственно) и нажмите OK. Убедитесь что название создаваемого изображения symbol, которое указано “To View Name”.

Шаг 4: После нажатия OK в Шаге 3, возникнет следующее окно. В окне “Symbol Generation Options” Вы можете отредактировать список выводов (pins) и с какой стороны символа они будут расположены. По умолчанию, входные выводы располагаются слева и выходные – справа символа. Если Вы не хотите ничего изменять, нажмите OK, чтобы продолжить.

Рис. 21 – Окно настроек создания символа “Symbol Generation Options”

17

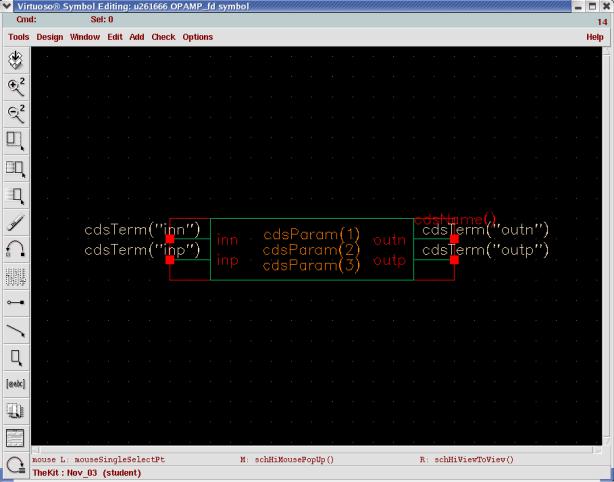

Шаг 5: В новом окне автоматически создастся новый символ. Форма иконки символа по умолчанию – это прямоугольник.

Рис. 22 – Созданный автоматически символ полностью дифференциального ОУ

Шаг 6: Редактирование формы иконки символа. Вы можете сделать следующие операции, доступные через меню Add, применительно к созданному символу:

(1)Удаление/замещение некоторых существующих частей;

(2)Добавление новых геометрических форм (Add→Shape…);

(3)Изменение расположения выводов и имени модуля (имя модуля следует добавить командой Add→Label…);

(4)Добавление новых пояснительных подписей(Add→Label…).

На Рис. 23 приведен пример созданного вручную символа ОУ, который был сделан путем редактирования символа на Рис. 22. Обратите внимание - красная рамка – граница символа, удалять еѐ не следует.

18

Рис. 23 – Символ полностью дифференциального ОУ после редактирования.

Шаг 7: В окне “Virtuoso Symbol Editing” выберите пункт Design…→Check and Save. Таким образом, Вы создали свой символ для дальнейшего использования.

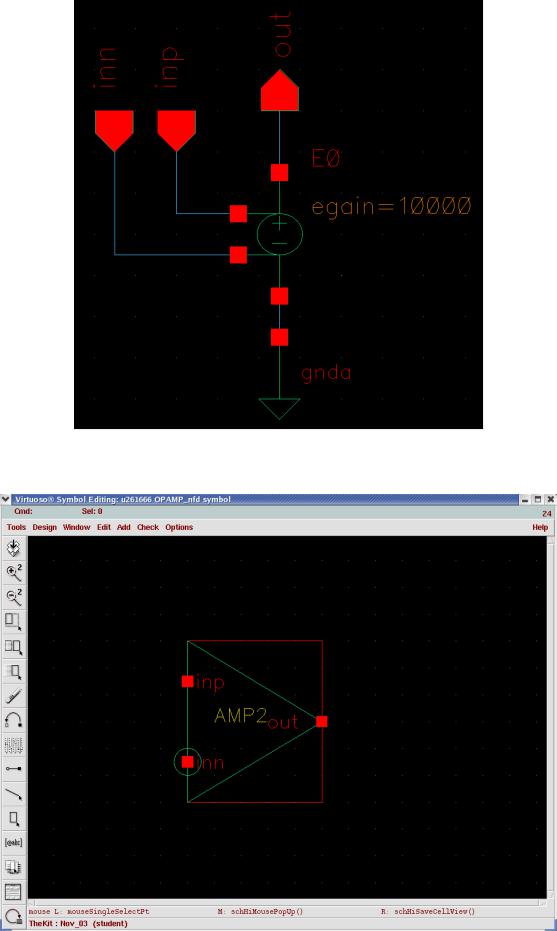

Шаг 8: Повторите шаги 1-7, но для НЕполностью дифференциального усилителя

(название файла – OPAMP_nfd). Элемент VCVS находится в библиотеке analogLib.

Параметр Voltage gain принять равным 10000.

19

Рис. 24 – Источник напряжения управляемый напряжением, используемый в качестве неполностью дифференциального ОУ (с одним выходом)

Рис 25 – Символ неполностью дифференциального ОУ (с одним выходом)

20