Схемотехника / Учебники и методички / lab_m3_vt_vt_aloiscevm_niy06

.pdf

D* X

A1 |

1 |

0 |

0 |

1 |

|

|

||

|

|

|

|

|

|

A0 |

||

|

|

|

|

|

||||

|

|

|

|

|

|

|

||

0 |

1 |

0 |

0 |

|||||

|

|

|||||||

|

|

|

|

|

|

|

||

1 |

1 |

0 |

0 |

|

|

|||

|

|

|

|

|

|

|

|

|

Q

Рис.9. Карты Карно для разряда регистра

В результате минимизации получаем

D* A1 Q A1 XQ A1 A0Q A1 Q A1Q( X A0 ) .

Теперь можно нарисовать схему одного разряда регистра, выполняющего заданные микрооперации (рис.10).

A0 |

|

|

1 |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Xi |

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

Qi |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

* |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

1 |

D |

|

D |

T |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(TT) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

& |

|

|

|

Т.И |

|

|

|

|

|

|

Qi |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i=0...3

Рис.10. Схема одного разряда регистра

4-разрядный регистр получается использованием четырёх одноразрядных регистров с общим кодом микрооперации A1A0.

Построим временную диаграмму работы разряда регистра (рис.11)

11

Т.И. |

A1 |

A0 |

Xi |

Qi |

Рис.11. Временная диаграмма работы одного разряда регистра |

Используя методические указания к предыдущим работам, присту- |

пим к практической реализации схемы делителя частоты (см. рис.7) в |

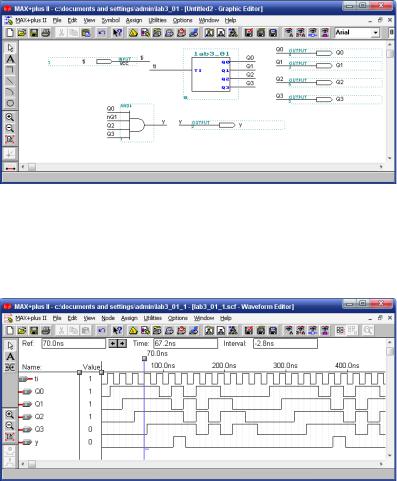

среде МАХ+ PLUS II. Нарисуем сдвиговый регистр (рис.12). |

РРис.12. Схема сдвигового регистра в среде МАХ+ PLUS II

Создадим из него компонент, который установим в новую схему. Добавим также необходимые входные и выходные сигналы, не забыв

про функцию выхода Fвых Q3Q2Q1Q0 . Результат показан на рис.13.

12

Рис.13. Схема делителя частоты с использованием созданного компонента

Используя методические указания к предыдущим работам, просимулируем работу делителя частоты. Для этого создадим файл с временной диаграммой, сохраним его с тем же именем, что и проект, добавляем входные и выходные сигналы, после чего запустим процесс симуляции (рис.14).

Рис.14. Симуляция работы делителя частоты

Для наглядности сгруппируем сигналы Q3, Q2, Q1, Q0 в одну группу с отображением представления в десятичном виде (рис.15). Этот результат наглядно покажет пути смены состояний сдвигового регистра делителя частоты.

13

Рис.15. Симуляция работы делителя частоты с сгруппированными сигналами Q3..Q0

Полученные диаграммы (см. рис.14 и 15), в случае правильного проектирования должны быть одинаковыми с расчётными рис.11. При несовпадении временных диаграмм с заданием необходимо найти ошибки синтеза или ошибки в схеме и исправить их, после чего снова выполнить симуляцию работы проекта.

Приступим к сборке полученных схем для второго задания. Соберём схему одного разряда регистра (см. рис.10) в среде MAX+PLUS II. Результат приведён на рис.16.

Рис.16. Схема одного разряда регистра в среде MAX+PLUS II

После успешной компиляции проекта с одним разрядом регистра для удобства использования создадим новый компонент, выполнив несложные команды в меню File -> Create Default Symbol. Компоненты

14

удобны в использовании и могут содержать огромные схемы, которые реализуют сложные вычисления.

Теперь создадим новый файл в графическом редакторе. Для получения 4-разрядного регистра вставим в него полученный компонент 4 раза. Для этого сделаем двойной клик левой клавишей мышки в рабочей области графического редактора, в появившемся окне в поле symbol Files выбираем имя добавляемого компонента. Добавив необходимые входы и выходы, получаем результат, показанный на рис.17.

Сохраним полученный проект и просимулируем его работу. Для наглядности на временной диаграмме оставим информационные сигналы одного разряда регистра. Подадим на входные сигналы A1, A0, X, ТИ те же уровни, что и на расчетной временной диаграмме (см. рис.11). Тогда результат симулирования Q, показанный на рис.18, должен быть таким, же как и на рис.11.

При несовпадении временных диаграмм с рассчитанными необходимо найти ошибки синтеза или ошибки в схеме и исправить их, выполнить компиляцию и симуляцию проекта снова и убедиться в правильности новых результатов.

Рис.17. 4-разрядный регистр

15

Рис.18. Временная диаграмма работы регистра

Перечень индивидуальных заданий

1.Используя сдвиговый регистр, разработать самовосстанавливающийся делитель частоты на N (тип триггера и N указаны в индивидуальном задании).

2.Используя триггеры, разработать 4-разрядный регистр, выполняющий несколько микроопераций. Тип триггера и перечень микроопераций указаны в индивидуальном задании.

3.Оформить схемы отдельными компонентами MAXPLUSII. Просимулировать работу регистра, сравнить временные диаграммы с расчётными.

Допуск к работе: выполнить задания, построить временную диаграмму ко второму заданию (для одного разряда), показать на ней выполнение всех операций.

Вариант 1

1.Тип триггера: JK. N = 10.

2.Тип триггера: D. Выполняемые микрооперации: - лог. «И»; - лог. «ИЛИ»;

- «хранение».

16

Вариант 2

1.Тип триггера: JK. N = 11.

2.Тип триггера: D. Выполняемые микрооперации: - «приём данных»; - лог. «И»; - лог. «=».

Вариант 3

1.Тип триггера: JK. N = 12.

2.Тип триггера: D. Выполняемые микрооперации: - приём данных; - лог. «И»;

- лог. «XOR».

Вариант 4

1.Тип триггера: JK. N = 13.

2.Тип триггера: D. Выполняемые микрооперации: - приём данных; - лог. «ИЛИ»; - лог. «1».

Вариант 5

1.Тип триггера: JK. N = 9.

2.Тип триггера: D. Выполняемые микрооперации: - приём данных; - лог. «И»; - «0».

Вариант 6

1.Тип триггера: D. N = 10.

2.Тип триггера: JK. Выполняемые микрооперации: - приём данных; - лог. «ИЛИ»;

- лог. «XOR».

17

Вариант 7

1.Тип триггера: D. N = 11.

2.Тип триггера: JK. Выполняемые микрооперации: - приём данных;

- лог. «XOR»; - лог. «0».

Вариант 8

1.Тип триггера: JK. N = 12.

2.Тип триггера: D. Выполняемые микрооперации: - приём данных; - лог. «И»; - лог. «ИЛИ».

Вариант 9

1.Тип триггера: D. N = 13.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «И»; - лог. «1»; - лог. «=».

Вариант 10

1.Тип триггера: D. N = 9.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «И»; - лог. «ИЛИ»;

- «приём данных».

Вариант 11.

1.Тип триггера: D. N = 10.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «И»; - лог. «=»; - «0».

18

Вариант 12

1.Тип триггера: D. N = 11.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «ИЛИ»; - лог. «=»;

- Qt 1 Q t x .

Вариант 13

1.Тип триггера: D. N = 12.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «ИЛИ»;

- лог. «XOR»; - лог. «0».

Вариант 14

1.Тип триггера: D. N = 13.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «И»; - лог. «=»;

- «счётный режим»; - лог. «1».

Вариант 15

1.Тип триггера: D. N = 9.

2.Тип триггера: JK. Выполняемые микрооперации: - лог. «XOR»;

- лог. «ИЛИ»; - лог. «1».

19

Вариант 16

1.Тип триггера: JK. N = 10.

2.Тип триггера: D. Выполняемые микрооперации: - приём данных; - лог. «И»; - лог. «0»; - лог. «1».

Вариант 17

1.Тип триггера: JK. N = 11.

2.Тип триггера: D. Выполняемые микрооперации: - приём данных; - лог. «ИЛИ»;

- «счётный режим».

Вариант 18

1.Тип триггера: JK. N = 12.

2.Тип триггера: D. Выполняемые микрооперации: - лог. «ИЛИ»;

- лог. «XOR»;

- «приём данных».

Вариант 19

1.Тип триггера: JK. N = 13.

2.Тип триггера: D. Выполняемые микрооперации: - лог. «1»; - лог. «И»;

- «счётный режим».

20