- •Структура 16-разрядного микропроцессора.

- •Мультиплексирование шины ардеса/данных .

- •3.Типы и характеристики модемов .

- •Типы и виды модемов.

- •4. Интерфейс микропроцессора с пзу и озу

- •5. Связь двух эвм по последовательному интерфейсу

- •6. Передача данных между эвм с помощью модемов

- •7. Программная модель эвм.(?)

- •8. Интерфейс микропроцессора с устройствами ввода/вывода

- •9. Выделенные и коммутируемые линии связи

- •10. Назначение сигналов интерфейса rs-232c.

- •11. Базовая система ввода/вывода (bios).

- •12. Методы адресации.

- •13. Приоритеты прерываний внешних устройств эвм.

- •14. Коммуникационные пакеты.

- •15. Графическая операционная среда windows.

- •Основными элементами графического интерфейса Windows являются:

- •Диалоговые окна

- •16. Маскируемые и немаскируемые прерывания.

- •17. Ascii коды.

- •18. Команды условных переходов.

- •19. Видеоадаптер. Цветной и монохромный режимы. Интерфейс с видеоадаптером

- •20. Интерфейс эвм и накопителей на магнитных дисках.

- •21. Системы телекоммуникаций.

- •22. Жесткие магнитные диски.

- •23. Структура диска: дорожки, блоки, сектора.

- •26. Как вы понимаете определение "открытая система"?

- •24. Семиуровневая модель открытых систем.

- •25. Гибкие магнитные диски.

- •27. Обмен информацией между эвм и магнитными дисками.

- •28. Параллельный lpt порт эвм.

- •29. Режимы работы эвм.

- •Режим пакетной обработки

- •Режим коллективного доступа

- •30. Вывод данных через параллельный порт.

- •31. Программная модель контроллера ввода-вывода.

- •32. Что такое транзакция?

- •33. Набор ат-команд.

- •34. Аппаратные и командные прерывания.

- •35. Операционная система ms-dos.

- •36. Принцип действия клавиатуры.

- •37. Последовательный com порт эвм.

- •38. Сетевые операционные системы.

- •39. Видеоадаптер. Режимы изображения: Текстовый и графический.

- •Режимы изображений.

- •40. Ввод данных через параллельный порт.

- •41. Программирование последовательного порта.

- •42. Интерфейс эвм и принтера.

- •43. Прерывания для работы с клавиатурой.

- •44. Глобальные вычислительные системы.

- •45. Локальные вычислительные сети.

- •46. Классификация вычислительных систем.

Структура 16-разрядного микропроцессора.

Структура микропроцессора.

Микропроцессор – это полупроводниковое устройство, состоящее из одной или нескольких программно-управляемых БИС, включающих все средства, необходимые для обработки информации и управления, и рассчитанное на совместную работу с устройствами памяти и ввода-вывода информации.

Микропроцессор состоит из трех основных блоков:

- арифметически-логического

- блока регистров

- устройства управления

Арифметически-логическое устройство (АЛУ) – выполняет все арифметические и логические преобразования данных.

Устройство управления – электронный блок компьютера, включающий в работу устройства, блоки, электронные элементы и цепи в зависимости от содержания текущей команды.

Регистр – ячейка памяти в виде совокупности триггеров, предназначенных для хранения одного данного в двоичном коде.

Количество разрядов в регистре определяется разрядностью микропроцессора

Регистры общего назначения – образуют сверхоперативную и служат для хранения операндов участвующих в вычислениях, а также результатов вычислений.

Операндом называются – исходные данные, над которыми производятся различные действия в арифметическом устройстве.

Регистр команд – служит для хранения команды, выполняемой в текущий момент времени.

Счетчик команд – регистр, указывающий адрес ячейки памяти, где хранится следующая команда.

Стек (стековая память) – совокупность связанных между собой регистров для хранения упорядоченных данных. Первый выбирается из стека данное попавшее туда последним, и наоборот.

Мультиплексирование шины ардеса/данных .

Магистрально-модульный принцип.

Основой архитектуры современных компьютеров является магистрально-модульный принцип организации аппаратных компонентов. Здесь все информационные и управляющие потоки между устройствами организуются с помощью шинной технологии.

В системную магистраль (системную шину) микропроцессорной системы входит три основные информационные шины: адреса, данных и управления.

Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд. Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями.

Обычно шина данных имеет 8, 16, 32 или 64 разряда. Понятно, что за один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных.

Шина адреса— вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2 в N-й ст, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП).

Шина управления— это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа.

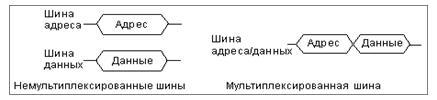

Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Понятно, что мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (Рис.). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.