Схемотехника / Аналог / Аналоговая схемотехника

.pdf

задающая схема токового зеркала. Выбор выходных транзисторов и эмиттерных резисторов определяется условием:

UИП = I1R1 +UБЭ1 +UБЭ2 + I1R2;

U Б = UБЭ2 +UR2 = UБЭ3 +UR3 = ..... = UБЭ(n+2) +UR(n+2)

или

U Б =UБЭ2 + I2R2 =UБЭ3 + IВЫХ1R3 = ..... = UБЭ(n+2) + IВЫХnR(n+2) .

Если плотность тока I/S одинаковая во всех выходных транзисторах Т3 - Тn+2 и в задающем транзисторе Т2, то падение напряжения на эмиттерном переходе UБЭ у них будет одинаковое. И соответственно падение напряжения на эмиттерных резисторах URi

получим

I2R2 = IВЫХ1R3 = ..... = IВЫХn R(n+2) .

Тогда для заданных значений выходных токов IВЫХ1 - IВЫХn получим

R3 = II2R2 , R(n+2) = II2R2 .

ВЫХ1 ВЫХn

Минимальное значение выходного напряжения, соответствующего диапазону линейного изменения тока, определяется как

UВЫХ min = UБ -UБКН = UR2 +UБЭ2 -UБКН = UR2 +UБЭ2 - 0,5 В .

Если площади транзисторов одинаковы, плотность токов различна и напряжения на эмиттерных переходах транзисторов различаются, то выравнивание достигается за счет подбора резисторов R3 - Rn+2.

R = |

(U |

БЭ2 |

-U |

БЭ3 |

)+ I |

R |

|

, R |

= |

|

(UБЭ2 -UБЭ(n |

+ |

2) )+ I2R2 |

|

||

|

|

|

|

2 2 |

|

|

|

|

|

|

||||||

3 |

|

|

IВЫХ1 |

|

|

(n+2) |

|

|

|

IВЫХn |

. |

|||||

|

|

|

|

|

|

|

|

|

||||||||

Дифференциальное выходное сопротивление по каждому выходу зависит от |

||||||||||||||||

дифференциальной выходной |

|

проводимости |

|

выходных |

|

транзисторов gКЭ(n+2) , |

||||||||||

увеличивается в 1+ gm(n+2) × R(n+2) |

раз за счет наличия эмиттерного сопротивления R(n+2) и |

|||||||||||||||

определяется выражением |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

rВЫХn = |

1+ gm(n+2) R(n+2) |

|

|

|

|

||||||

|

|

|

|

|

|

gКЭ(n+2) |

. |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

41

PDF created with pdfFactory Pro trial version www.pdffactory.com

3.3. Источники постоянного тока на МОП-транзисторах

Принцип построения ИПТ на МОП-транзисторах аналогичен принципу построения ИПТ на биполярных транзисторах.

3.3.1. Обычный источник тока

Схема источника тока на полевом транзисторе, включенном с общим истоком, приведена на рис.3.13.

Рис.3.13. Схема обычного источника тока на МДП-транзисторе

Чтобы транзистор работал в пологой области, необходимо выполнить следующие условия:

UЗИ ³ UПОР , UСИ ³ UЗИ -UПОР; |

|||||||||

IВЫХ = IС = |

kудW |

(UЗИ -UПОР )2; |

|||||||

|

|

|

|||||||

|

|

|

2L |

|

|

|

|

|

|

UЗИ = UИП × R2 |

|

|

|

|

|

||||

|

R1 + R2 . |

|

|

|

|

|

|||

Тогда |

|

|

|

|

|

|

|

|

|

|

kудW æU |

ИП |

R |

ö2 |

|||||

|

ç |

|

2 |

÷ |

|||||

IВЫХ = |

|

ç |

|

|

|

-UПОР ÷ |

|||

2L |

R |

|

+ R |

||||||

|

è 1 |

|

|

2 |

ø . |

||||

На рис.3.14 приведена малосигнальная эквивалентная схема источника тока.

Рис.3.14. Малосигнальная эквивалентная схема обычного ИПТ

42

PDF created with pdfFactory Pro trial version www.pdffactory.com

Выходное дифференциальное сопротивление ИПТ равно:

r |

= g −1 |

|

= |

U A |

|

= |

1 |

|

|

|

|

|

|

|

|||||

ВЫХ |

СИ |

|

IВЫХ |

|

|

l × IВЫХ . |

|||

|

|

|

|

|

|

||||

Минимальное выходное напряжение равно: |

|

|

|

|

|||||

UВЫХ min |

= UИП × R2 |

-UПОР |

|||||||

|

|

|

R1 + R2 |

|

. |

|

|||

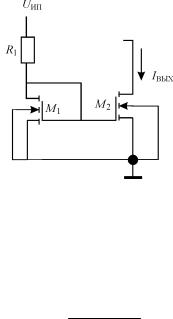

3.3.2. Токовые зеркала на МОП-транзисторах

Обычное токовое зеркало. На рис.3.15 приведена схема обычного токового зеркала на МОП-транзисторах.

Рис.3.15. Схема обычного токового зеркала

Ток в задающей цепи определяется как ток, протекающий через R1

I R1 = U ИП - U ЗИ

R1

С другой стороны, ток в задающей цепи можно определить как ток стока транзистора М1, а выходной - ток стока транзистора М2

|

|

|

|

IR1 = IС1 = |

kудW1 |

(UЗИ -UПОР )2 |

||||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

2L1 |

|

|

|

|

; |

|

|

|

|

IВЫХ = IС2 |

= |

kудW2 |

(UЗИ -UПОР )2 |

|||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

2L2 |

|

. |

|||

|

IВЫХ |

= W2 / L2 |

|

|

|

I |

ВЫХ |

= I |

W2 |

|||

|

|

|

|

|

||||||||

Тогда |

I |

|

W / L |

. Если L1 = L2 = L, то |

|

R1 W |

||||||

|

R1 |

1 1 |

|

|

|

|

1 . |

|||||

Можно реализовать токовое зеркало на несколько выходов. При этом размеры

выходного транзистора будут масштабироваться относительно размеров транзистора в

43

PDF created with pdfFactory Pro trial version www.pdffactory.com

задающей цепи М1 в соответствии с коэффициентом, определяемым соотношением токов

W = W × IВЫХn |

|

n 1 |

IR1 . |

|

|

Дифференциальное выходное сопротивление определяется коэффициентом модуляции длины канала и выходным током:

r |

= g−1 |

= |

U A |

= |

1 |

. |

|

|

|||||

ВЫХn |

СИn |

|

IВЫХn |

|

l × IВЫХn |

|

|

|

|

|

|

Минимальное выходное напряжение равно:

UВЫХ min =UИП - IR1R1 -UПОР .

Токовое зеркало Уилсона. На рис.3.16 приведена схема токового зеркала Уилсона.

UИП

r0 |

IВЫХ |

I0 |

M1 |

|

UЗИ1

|

|

|

M3 |

M2 |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|||

|

|

|

|

UЗИ |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а

б

Рис.3.16. Токовое зеркало Уилсона: а - схема; б - малосигнальная

эквивалентная схема

С повышением сложности токового зеркала увеличивается дифференциальное выходное сопротивление. Однако при этом ухудшаются динамические характеристики.

Соотношение токов с учетом эффекта модуляции длины канала определяется как

44

PDF created with pdfFactory Pro trial version www.pdffactory.com

|

|

æW ö |

(1+ l ×UСИ2 ) |

|||||

IВЫХ |

|

ç |

|

|

÷ |

|||

|

|

|

||||||

= |

è L ø2 |

|

|

|||||

I0 |

æW ö |

(1+ l ×UЗИ3 ) |

||||||

|

|

ç |

|

÷ |

||||

|

|

|

||||||

|

|

è L ø3 |

. |

|||||

Так как UСИ2 = UЗИ и UСИ3 = UЗИ +UЗИ1 , то UСИ2 ¹ UСИ3 .

Таким образом, отношение токов зависит от UЗИ и UЗИ1 .

Дифференциальное выходное сопротивление определяется как

r−1 |

= |

|

gСИ1 |

|

|

|

|

|

|

|

||

ВЫХ |

|

1+ |

gm |

|

r |

= r |

(1+ g |

r |

) |

|

||

|

|

|

|

|||||||||

|

|

g |

СИ2 |

или |

. |

|||||||

|

|

|

|

|

ВЫХ |

СИ1 |

|

m СИ2 |

|

|||

Усовершенствованное токовое зеркало Уилсона. На рис.3.17 приведена схема токового зеркала Уилсона с улучшенным соотношением токов, определяемым только соотношением геометрических размеров транзисторов.

Рис.3.17. Схема усовершенствованного токового зеркала Уилсона

Для этой схемы геометрические размеры транзисторов задаются таким образом,

чтобы

æW ö |

|

æW ö |

|

|||||||||

ç |

|

|

|

÷ |

|

ç |

|

|

÷ |

|

||

|

|

|

|

|

|

|||||||

è |

|

L ø1 |

= |

è |

|

L ø |

2 |

|||||

æW ö |

æW ö |

|||||||||||

|

|

|||||||||||

ç |

|

|

÷ |

|

ç |

|

|

÷ |

|

|||

|

|

|

|

|

||||||||

è |

|

L ø4 |

|

è |

|

L ø |

3 . |

|||||

При этом соотношение токов определяется следующим выражением:

45

PDF created with pdfFactory Pro trial version www.pdffactory.com

|

|

æW ö |

(1 |

+ lUСИ2 ) |

|||||

IВЫХ |

|

ç |

|

|

÷ |

||||

|

|

|

|||||||

= |

è |

|

L ø |

2 |

|

|

|||

I0 |

æW ö |

|

+ lUСИ3) |

||||||

|

|

ç |

|

|

÷ (1 |

||||

|

|

|

|||||||

|

|

è |

|

L ø3 |

. |

||||

По схеме в соответствии с соединением транзисторов получим

UСИ3 = UЗИ2 + UЗИ1 -UЗИ4 .

Если UЗИ1 = UЗИ4 , то UСИ3 = UЗИ2 . Поскольку транзистор М2 находится в диодном включении, то UСИ2 = UЗИ2 . Тогда окончательное соотношение токов имеет вид

|

|

æW ö |

+ lUСИ2 ) |

|

æW ö |

+ lUЗИ2 ) |

|

æW ö |

||||||||||||

IВЫХ |

|

ç |

|

|

÷ (1 |

|

ç |

|

|

÷ (1 |

|

ç |

|

|

÷ |

|||||

|

|

|

|

|

|

|

|

|

||||||||||||

= |

è L ø2 |

|

= |

è L ø2 |

|

= |

è L ø2 |

|||||||||||||

I0 |

æW ö |

+ lUСИ3 ) |

|

æW ö |

+ lUЗИ2 ) |

|

æW ö |

|||||||||||||

|

|

ç |

|

÷ (1 |

|

ç |

|

÷ (1 |

|

ç |

|

÷ |

||||||||

|

|

|

|

|

|

|

||||||||||||||

|

|

è L ø3 |

|

|

è L ø3 |

|

|

è L ø3 . |

||||||||||||

Токовое зеркало Видлора. На рис.3.18 приведена схема токового зеркала Видлора с улучшенным соотношением токов, определяемым только соотношением геометрических размеров транзисторов.

UИП

I0

I0

|

M 3 |

IС1 |

IВЫХ |

|

M2 |

|

M1 |

Рис.3.18. Схема токового зеркала Видлора

Транзисторы М1, М3 находятся в диодном включении, поэтому

UЗИ = UСИ Þ UСИ > UЗИ -UПОР .

Таким образом, эти транзисторы всегда работают в пологой области и их ток стока определяет ток в задающей цепи:

|

|

|

|

|

kуд æW ö |

|

|

2 |

|

||

IС1 = IС3 = |

|

ç |

÷ |

(UЗИ1 |

-UПОР1) (1 |

+ l1UЗИ1)= |

|||||

|

|||||||||||

|

|

|

|

|

2 è |

L ø1 |

|

|

|

|

|

|

kуд æW ö |

|

|

|

|

2 |

|

|

|||

= |

|

ç |

|

÷ |

(UЗИ3 -UПОР3 ) (1 |

+ l3UЗИ3 ). |

|||||

2 |

|

||||||||||

|

è |

L ø3 |

|

|

|

|

|

||||

46

PDF created with pdfFactory Pro trial version www.pdffactory.com

Если М2 работает в пологой области, то UВЫХ > UЗИ -UПОР и

|

|

kуд æW ö |

2 |

|

|||

IВЫХ = IС2 |

= |

|

ç |

|

÷ |

(UЗИ2 -UПОР2 ) (1 |

+ l2UВЫХ ) |

2 |

|

||||||

|

|

è |

L ø2 |

|

. |

||

Если транзисторы М1 |

и М2 имеют одинаковые следующие параметры: UЗИ1 = UЗИ2 , |

||||||||||||||||||

UПОР1 = UПОР2 = UПОР , l1 = l2 = l , то соотношение токов в схеме определяется как |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

æW ö |

(1+ lUВЫХ ) |

|||||||

|

|

|

|

|

ç |

|

|

|

÷ |

||||||||||

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

IВЫХ |

= |

è |

|

L ø |

2 |

|

|

|||

|

|

|

|

|

|

|

|

|

I0 |

æW |

ö |

+ lUЗИ ) |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

ç |

|

|

|

÷ (1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

è L |

ø1 |

. |

|||||

|

|

|

|

æW ö |

|

|

|

|

|

|

|

|

|||||||

|

IВЫХ |

|

ç |

|

|

÷ |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

= |

è |

|

L ø2 |

|

|

|

|

|

|

|

|

|||||||

|

I |

0 |

|

æW ö |

|

|

|

|

|

|

|

|

|||||||

Если λ = 0 , то |

|

ç |

|

|

÷ |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

è |

|

L ø1 . |

|

|

|

|

|

|

|

|

|||||||

Таким образом, в схеме источника тока Видлора:

-выходной ток IВЫХ зависит только от соотношения геометрических размеров транзисторов М1 и М2;

-выходной ток IВЫХ может быть стабильным током, если задающий ток I0 будет постоянным;

-выходной ток IВЫХ практически не зависит от выходного напряжения UВЫХ , если транзистор М2 работает в пологой области. Поэтому минимальное выходное напряжение,

соответствующее условию работы транзистора в пологой области, будет

UВЫХ ³ UЗИ2 -U ПОР ;

-выходное дифференциальное сопротивление схемы равно rВЫХ = rВЫХ2 = (lIВЫХ )−1 .

Каскодное токовое зеркало Видлора. На рис.3.19 приведена схема каскодного токового зеркала Видлора с увеличенным выходным дифференциальным сопротивлением.

Выходной ток определяется нижним токовым зеркалом, выполненным на транзисторах М1 и М2:

|

|

æW ö |

+ lUСИ2 ) |

|||||

IВЫХ |

|

ç |

|

|

÷ (1 |

|||

|

|

|

||||||

= |

è |

|

L ø2 |

|

|

|||

I0 |

æW ö |

+ lUЗИ1) |

||||||

|

|

ç |

|

÷ (1 |

||||

|

|

|

||||||

|

|

è |

L ø1 |

. |

||||

47

PDF created with pdfFactory Pro trial version www.pdffactory.com

Рис.3.19. Схема каскодного токового зеркала Видлора

Размеры транзисторов, соединенных последовательно и работающих на одном токе,

равны. Поэтому W1 = W3 и W2 = W4 и в соответствии с принципом работы токового зеркала

геометрические размеры транзисторов должны удовлетворять условию

|

æW ö |

|

æW |

ö |

|

||||||||

ç |

|

|

|

|

÷ |

ç |

|

|

|

÷ |

|

||

|

|

|

|

|

|

||||||||

è |

|

|

L ø1 |

= |

è L |

ø3 |

|

||||||

|

æW ö |

|

æW |

ö |

|

||||||||

ç |

|

|

|

÷ |

ç |

|

|

|

÷ |

|

|||

|

|

|

|

|

|||||||||

|

è L ø2 |

|

è L |

ø4 . |

|||||||||

Для реализации источника тока транзисторы М2, М4 должны работать в пологой |

|||||||||||||

области, т.е. UСИ ³ UЗИ -UПОР (рис.3.20). |

Для выполнения этого условия необходимо, |

||||||||||||

чтобы UСИ2 = UЗИ1 . При условии использования идентичных размеров транзисторов, когда |

|||||||||||||

L1 = L2 = L3 = L4 , получим, что UЗИ3 = UЗИ4 |

и UЗИ1 = UЗИ2 . |

||||||||||||

Тогда UСИ2 = UЗИ1 +UЗИ3 -UЗИ4 = UЗИ1 |

|

|

|

|

|

|

|

|

|

|

|||

Рис.3.20. Режимы работы транзисторов в выходной цепи

48

PDF created with pdfFactory Pro trial version www.pdffactory.com

В схеме на рис.3.19 необходимо учитывать влияние подложки в транзисторах М3 и М4, поскольку у них напряжение подложка - исток отлично от нуля, что приводит к перерасчету порогового напряжения:

UПИ3 = UПИ4 = -UЗИ ; UПОР = UПОР0 - hUПИ = UПОР0 + hUЗИ .

Для компенсации изменения порогового напряжения выбирают

æW ö |

æW ö |

||

ç |

÷ |

> ç |

÷ ; |

è |

L ø3 |

è |

L ø1 |

æW ö |

æW ö |

|

||

ç |

÷ |

> ç |

÷ . |

|

è |

L ø4 |

è |

L ø |

2 |

Если в качестве входной схемы используется резистор, то задающий ток равен:

I0 = UИП - 2UЗИ |

. Дифференциальное выходное сопротивление каскодного источника тока |

|||||||||

r0 |

||||||||||

увеличивается |

по отношению к простому токовому зеркалу за счет составляющей |

|||||||||

gm3 / gСИ4 . |

|

|

|

|

|

|

|

|

|

|

|

g |

ВЫХ |

= |

|

gСИ3 |

|

» |

gСИ3 |

. |

|

|

|

|

|

|

||||||

|

|

|

|

|

gm3 |

|

1+ A |

|||

|

|

|

|

|

|

|

|

|

U |

|

|

|

|

|

1+ gСИ4 |

||||||

|

|

|

|

|

|

|

|

|||

3.4. Источники тока на полевом транзисторе со встроенным каналом

Наиболее просто реализуются источники тока на основе ПТ со встроенным каналом. Однако выходное сопротивление ПТ невелико из-за эффектов короткого канала.

Увеличить выходное сопротивление удается при каскодном включении полевых транзисторов.

3.4.1. Простой источник тока

На рис.3.21,а приведена схема двунаправленного источника тока на полевом транзисторе со встроенным каналом, на рис.3.21,б - ВАХ транзистора, работающего при

UЗИ = 0 . На участке пологой области при UСИ > UПОР реализуется источник тока.

|

IC |

gСИ |

|

IC |

|

|

|

В |

IP |

|

|

T11 |

|

|

|

UСИ |

|

|

|

a |

UР |

UИП |

UСИ |

|

б |

|

|

Рис.3.21. Источник тока: а - схема; б - ВАХ |

|

||

49

PDF created with pdfFactory Pro trial version www.pdffactory.com

Неидеальность этого источника определяется низким дифференциальным выходным

rВЫХ = rСИ = U A

сопротивлением IC .

3.4.2. Однонаправленный каскодный источник тока

Для увеличения дифференциального выходного сопротивления используем каскодное включение полевых транзисторов (рис.3.22,а). В источнике тока транзистор B2

должен работать в пологой области UС1 ³ U р , UОП ³ UС1 +U p , UВЫХ ³ UОП -UС1 . Этот режим задается с помощью резистивного делителя.

Рис.3.22. Каскодный источник тока: а - схема; б - ВАХ

На рис.3.22,б приведены ВАХ B1 ® IC1 = f (UСИ1 ) при UЗИ1 = 0 и B2 ® IC2 = f (UСИ2 )

при UСИ2 > UСИ1 . При этом размеры транзисторов Т1 и Т2 одинаковы (W1 = W2).

Дифференциальная выходная проводимость источника тока в соответствии с малосигнальной эквивалентной схемой (рис.3.23) равна:

gВЫХ = |

|

gСИ2 |

|

. |

|

æ |

|

gm2 |

ö |

||

|

ç |

+ |

÷ |

|

|

|

|

|

|||

|

ç1 |

|

÷ |

|

|

|

è |

|

gСИ1 ø |

|

|

Поскольку транзисторы идентичны и работают на одном токе, то получим

gВЫХ » g+СИ2

1 AU .

50

PDF created with pdfFactory Pro trial version www.pdffactory.com