- •Список используемых аббревиатур

- •Предисловие

- •Раздел 1. Микропроцессор: ключевые понятия, классификация, структура, операционные устройства

- •Лекция 1.3. Организация цепей переноса в пределах секции АЛУ. Наращивание разрядности обрабатываемых слов. Примеры использования АЛУ

- •Лекция 1.4. Структуры операционных устройств. Регистровое арифметико-логическое устройство

- •Лекция 1.5. Разрядно-модульные и однокристальные регистровые арифметико-логические устройства

- •Раздел 2. Устройства управления. Конвейерный принцип выполнения команд. Основные режимы функционирования микропроцессора

- •Лекция 2.1. Устройство управления: структура, способы формирования управляющих сигналов и адресации микрокоманд

- •Лекция 2.2. Система команд и способы адресации операндов. Конвейерный принцип выполнения команд

- •Лекция 2.3. Структурные конфликты и конфликты по данным. Методы их минимизации

- •Лекция 2.5. Режимы функционирования микропроцессорной системы: выполнение основной программы, вызов подпрограмм

- •Лекция 2.6. Обработка прерываний и исключений. Примеры построения систем прерывания

- •Раздел 3. Системы памяти. Обмен информацией в микропроцессорных системах

- •Лекция 3.1. Классификация систем памяти. Организация систем памяти в микропроцессорных системах

- •Лекция 3.2. Принципы организации кэш-памяти. Схема обнаружения и исправления ошибок

- •Лекция 3.3. Обмен информацией между микропроцессором и внешними устройствами. Арбитр магистрали

- •Лекция 3.4. Режим прямого доступа к памяти

- •Лекция 3.5. Виртуальная память. Устройство управления памятью

- •Раздел 4. Архитектуры и структуры микропроцессоров и систем на их основе

- •Лекция 4.1. Классификация архитектур современных микропроцессоров

- •Лекция 4.2. Структура современных 32-разрядных микроконтроллеров с RISC-архитектурой

- •Лекция 4.4. Особенности построения микропроцессоров общего назначения на примере архитектуры Intel P6

- •Раздел 5. Архитектуры и структуры параллельных вычислительных систем

- •Лекция 5.1. Назначение, область применения и классификация архитектур параллельных вычислительных систем

- •Лекция 5.3. Матричные вычислительные системы

- •Лекция 5.4. Векторно-конвейерные вычислительные системы

- •Лекция 5.5. Кластерные вычислительные системы

- •Лекция 5.6. Реконфигурируемые и систолические вычислительные системы. Архитектура систем, управляемых потоками данных

Д.Н. Беклемишев, А.Н. Орлов, А.Л. Переверзев, М.Г. Попов, А.В. Горячев, А.И. Кононова

Микропроцессорные средства и системы

Курс лекций

Под редакцией доктора технических наук, профессора Ю.В. Савченко

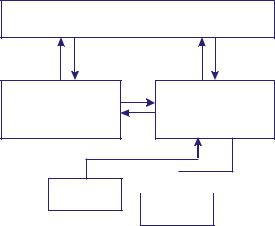

Память

Устройство Арифметикоуправления логическое устройство

Ввод  Вывод

Вывод

Москва 2013

Министерство образования и науки Российской Федерации

Национальный исследовательский университет «МИЭТ»

Д.Н. Беклемишев, А. Н. Орлов, А. Л. Переверзев,

М.Г. Попов, А. В. Горячев, А. И. Кононова

Микропроцессорные средства и системы

Курс лекций

Под редакцией доктора технических наук, профессора Ю. В. Савченко

Утверждено редакционно-издательским советом университета

Москва 2013

УДК 681.32 В75 М59

Рецензенты: докт. техн. наук, проф. А. Н. Соловьев; докт. техн. наук, проф. С. В. Гаврилов

Беклемишев Д. Н., Орлов А. Н., Переверзев А. Л., Попов М. Г., Горячев А. В., Кононова А. И.

М59 Микропроцессорные средства и системы: курс лекций / Под ред. Ю. В. Савченко. — М.: МИЭТ, 2013. — 288 с.: ил.

ISBN 978-5-7256-0723-9

Представлены материалы курса «Микропроцессорные средства и системы», целью которого является изучение особенностей построения и возможностей применения современной микропроцессорной техники, включающей как простейшие устройства с микропрограммным управлением, так и сложные многопроцессорные параллельные вычислительные системы.

Для студентов факультета МП и ТК МИЭТ, обучающихся по специальностям 230100 «Информатика и вычислительная техника», 210100 «Биотехнические системы и технологии», 211000 «Конструирование и технология электронных средств», 231000 «Программная инженерия», 231300 «Прикладная математика». Может быть полезен студентам других специальностей факультета, а также колледжа электроники и информатики.

ISBN 978-5-7256-0723-9 |

c |

○ МИЭТ, 2013 |

Список используемых аббревиатур

DSP |

— digital signal processor |

FLOPS — floating point operations per second |

|

MAC |

— multiplication with accumulation |

MIPS |

— million instructions per second |

MPA |

— message passing architecture |

MPI |

— message passing interface |

PC |

— program counter |

RAID |

— redundant array of independent disks |

SMP |

— symmetric multiprocessing |

АЛУ |

— арифметико-логическое устройство |

АЦП |

— аналого-цифровой преобразователь |

БИС |

— большая интегральная схема |

ВЗУ |

— внешнее запоминающее устройство |

ЗПДП |

— запрос прямого доступа к памяти |

ЗУ |

— запоминающее устройство |

ИП |

— интегрированный процессор |

КВВ |

— контроллер ввода/вывода |

КС |

— комбинационная схема |

КУП |

— команда условного перехода |

КШ |

— контроллер шины |

МК |

— микроконтроллер |

МП |

— микропроцессор |

МПК |

— микропроцессорный комплект |

МПУ |

— микропроцессорное устройство |

ОЗУ |

— оперативное запоминающее устройство |

ОП |

— основная память |

ОУ |

— операционное устройство |

ПА |

— периферийный адаптер |

ПБПП |

— программируемый блок приоритетных прерываний |

ПВС |

— параллельная вычислительная система |

ПДП |

— прямой доступ к памяти |

ПЗУ |

— постоянное запоминающее устройство |

3

ПЛИС |

— программируемая логическая интегральная схема |

ПЛМ |

— программируемая логическая матрица |

ПУ |

— периферийное устройство |

ПЦОС |

— процессор цифровой обработки сигналов |

ПЭ |

— процессорный элемент |

РА |

— регистр адреса |

РАЛУ |

— регистровое арифметико-логическое устройство |

РД |

— регистр данных |

РЗУ |

— регистровое запоминающее устройство |

РОН |

— регистры общего назначения |

РПДП |

— разрешение прямого доступа к памяти |

СОЗУ |

— сверхоперативное запоминающее устройство |

СУП |

— схема ускоренного переноса |

УМУ |

— устройство микропрограммного управления |

УУ— устройство управления

УФА — устройство формирования адреса ЦАП — цифро-аналоговый преобразователь ШИМ — широтно-импульсная модуляция

4

Предисловие

В настоящем издании представлены материалы курса «Микропроцессорные средства и системы», целью которого является изучение особенностей построения и возможностей применения современной микропроцессорной техники, включающей как простейшие устройства с микропрограммным управлением, так и сложные многопроцессорные параллельные вычислительные системы.

Для достижения указанной цели проанализированы общие тенденции развития и построения микропроцессорной техники, а также архитектуры и структуры микропроцессоров различного назначения, в частности, рассмотрены особенности организации операционных устройств, устройств управления, систем памяти, прерываний, режимов выполнения команд, обмена информацией и т. д.

Курс лекций разбит на пять разделов и имеет иерархическую структуру: каждый последующий раздел базируется на материалах предыдущих.

Раздел 1 состоит из пяти лекций и посвящен особенностям построения операционных устройств микропроцессоров. Первая лекция имеет общий характер и содержит ключевые определения и классификации, описание закономерностей развития микропроцессорной техники. Далее рассмотрены обобщенная структура микропроцессора

ипроцесс синтеза арифметико-логических устройств (АЛУ). Проанализированы способы наращивания разрядности обрабатываемых слов

иорганизации цепей арифметического переноса, приведены примеры использования АЛУ в качестве реконфигурируемого преобразователя информации. Показано функционирование АЛУ с разрядномодульной и однокристальной организацией.

Раздел 2 включает шесть лекций и посвящен особенностям построения устройств управления, структурным методам повышения производительности, а также режимам функционирования микропроцессорной системы. Рассмотрены общие структуры устройств управления на основе жесткой логики и с применением микропрограммирования, способы формирования управляющих сигналов и адресации

5

микрокоманд, а также способы адресации операндов. Проанализированы конвейерный принцип выполнения команд, возникающие при этом конфликтные ситуации и методы борьбы с ними. Рассмотрены основные режимы функционирования микропроцессорной системы: выполнение основной программы, вызов подпрограмм, обработка прерываний и исключений.

Раздел 3 состоит из пяти лекций и посвящен принципам организации систем памяти и обмена информацией в микропроцессорных системах. Приведены классификации систем памяти, рассмотрены принципы организации кэш-памяти, режима прямого доступа и виртуальной памяти. Проанализированы способы реализации обмена информацией микропроцессора с внешними устройствами.

Раздел 4 включает четыре лекции и посвящен архитектурам и структурам микропроцессоров и систем на их основе. Рассмотрены особенности архитектур с полным и сокращенным набором команд, суперскалярной, фон Неймана и гарвардской. Особенности архитектурных решений показаны на примерах структур современных микроконтроллеров, процессоров общего назначения и цифровой обработки сигналов.

Раздел 5 состоит из шести лекций и посвящен архитектурам и структурам параллельных вычислительных систем. Рассмотрены их назначение, область применения и классификация. Проанализированы принципы построения и функционирования векторно-конвейер- ных, матричных, кластерных и систолических систем, а также систем с реконфигурируемой структурой и управляемых потоком данных.

6