АНАЛИЗ И СИНТЕЗ ТИПОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ

.docxМИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«МАТИ - РОССИЙСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНОЛОГИЧЕСКИЙ УНИВЕРСИТЕТ имени К.Э. ЦИОЛКОВСКОГО» (МАТИ)

Кафедра

«Прикладная математика,

информационные технологии и электротехника»

Курсовая работа по модулю 2 «Электроника» дисциплины «Электротехника и электроника» на тему:

АНАЛИЗ И СИНТЕЗ ТИПОВЫХ ЭЛЕКТРОННЫХ УСТРОЙСТВ.

Выполнил: "___" _______201__г., ________

Сдано преподавателю на проверку

"___" _______ 201__г,

Проверил: ______________,

"___" _______ 201__г.

Москва

2015

Задание №3

|

№ п.п |

Последовательность выходных чисел |

|

99 |

14, 54, 84, 92, 36, 11, 54, 84 |

1. Определим необходимое число состояний и требуемый объем памяти автомата, формирующего на выходе заданную последовательность выходных кодов:

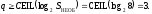

Согласно

заданию на выходе устройства должно

быть сформировано 8 чисел. Поэтому на

выходе формируется 8 различных чисел и

.

.

Для определения числа требуемых триггеров воспользуемся выражением:

Для реализации подсистемы памяти необходимо 3 триггера.

|

Исходное число |

Старший разряд выходного числа |

Младший разряд выходного числа |

|||||||

|

Z7 |

Z6 |

Z5 |

Z4 |

Z3 |

Z2 |

Z1 |

Z0 |

||

|

14 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

54 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

84 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

92 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

|

36 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

|

11 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

54 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

84 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

4. Согласно полученной таблице для реализации заданной последовательности кодов необходимо использовать 8-ми разрядный код.

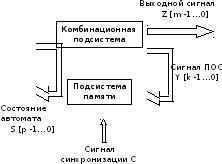

5. Обобщенная структурная схема проектируемого устройства имеет вид, показанный на рис. 1. Очевидно, что реализация проекта не требует использовать входной сигнал, т. е. имеем структуру автомата Мура.

Рис.

1. Обобщенная структурная схема

проектируемого устройства

-

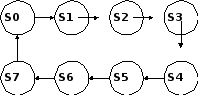

Синтезируем граф переходов проектируемого устройства.

-

Для реализации триггерной подсистемы выберем T-триггер. Запишем таблицу переходов триггера данного типа (см. табл.1).

|

Qn |

Qn+1 |

T |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

Таблица 1. Таблица переходов T-триггера

|

|

|

Y |

Z |

||||||||||||||||

|

Q2 |

Q1 |

Q0 |

Q2 |

Q1 |

Q0 |

T2 |

T1 |

T0 |

Z7 |

Z6 |

Z5 |

Z4 |

Z3 |

Z2 |

Z1 |

Z0 |

|||

|

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|||

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|||

|

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|||

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|||

|

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|||

|

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

|||

|

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

|||

|

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|||

-

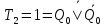

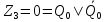

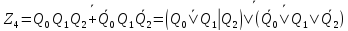

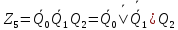

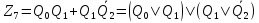

Минимизацию ФАЛ комбинационной подсистемы выполним с использованием карт Вейча (рис. 3).

T0

T2

Z1

Z3 |

T1

Z0

Z2

Z4 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Z5 |

Z6 |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Z7 |

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

-

Приведем полученные выражения к базису элементов 2И-НЕ.

|

(

|

( |

|

)

)

-

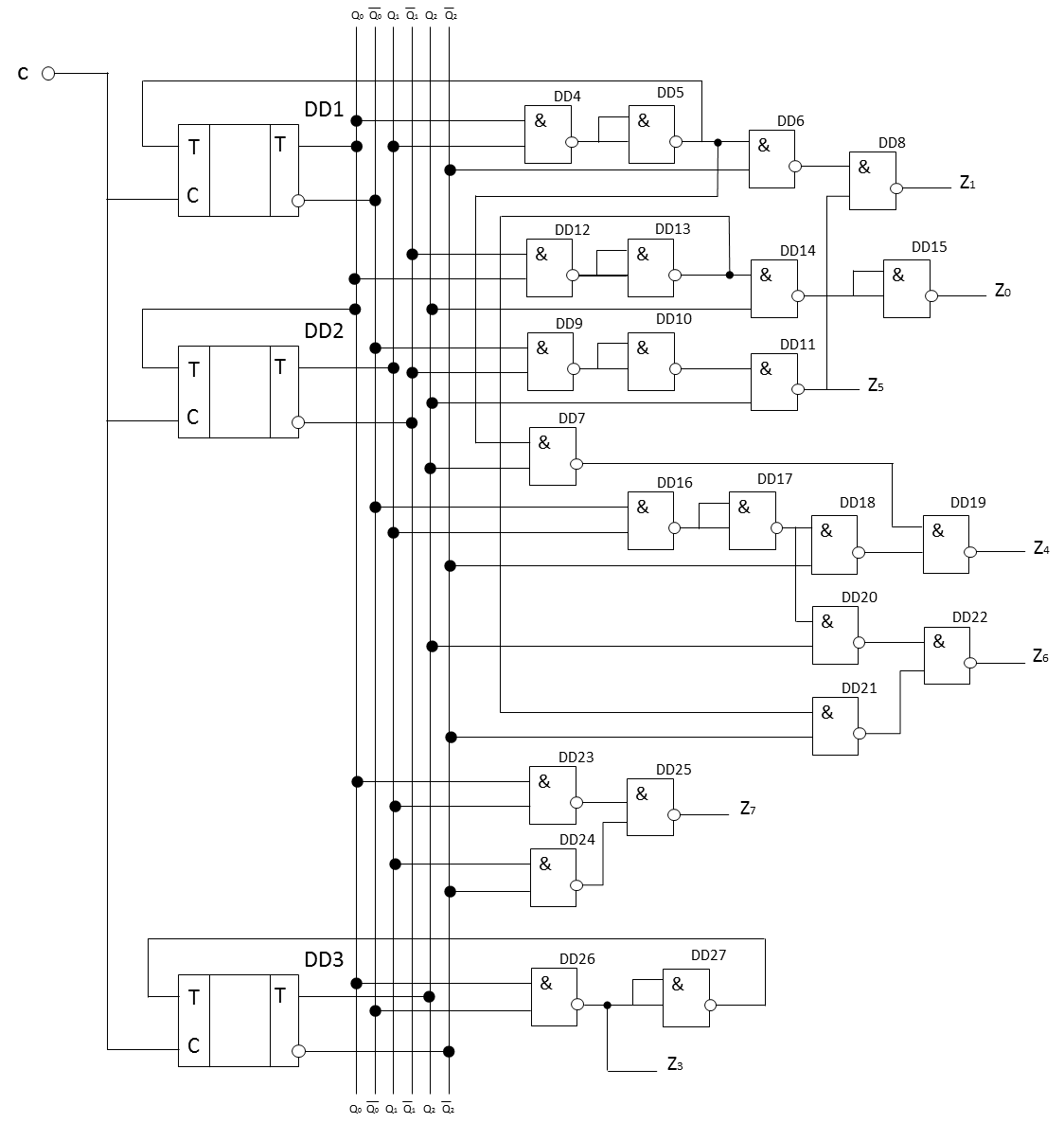

Синтезируем схему автомата.

Нарисуем временные диаграммы, поясняющие работу спроектированного устройства. Для этого на вход С подадим последовательность импульсов синхронизации, а на выходах триггеров подсистемы памяти зададим одно из возможных состояний S.