Elektronika3_laba-1

.docxМинистерство образования и науки Российской Федерации

Федеральное государственное автономное образовательное учреждение

высшего образования

«НАЦИОНАЛЬНЫЙ ИССЛЕДОВАТЕЛЬСКИЙ

ТОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ»

Институт - Энергетический

Направление - Электроэнергетика и электротехника

Кафедра - Электропривода и электрооборудования

Отчет по лабораторной работе № 3

Исследование логических схем

по курсу «Электроника 2.1»

Выполнили: студент гр.5А45 _________ _______ Анохин И.М.

Подпись Дата Фамилия И.О.

студент гр.5А45 _________ _______ Колесников И.С

Подпись Дата Фамилия И.О.

студент гр.5А45 _________ _______ Мельник С.О.

Подпись Дата Фамилия И.О.

Проверил преподаватель каф. ЭПЭО, _________ _________ Болгов И.С.

Подпись Дата Фамилия И.О.

Томск 2016

Цель работы: получить практические навыки при работе с логическими элементами микросхем транзисторно – транзисторной логики, а также навыки проектирования комбинационных логических схем.

Теоретические данные:

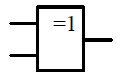

1) Логическая функция НЕ

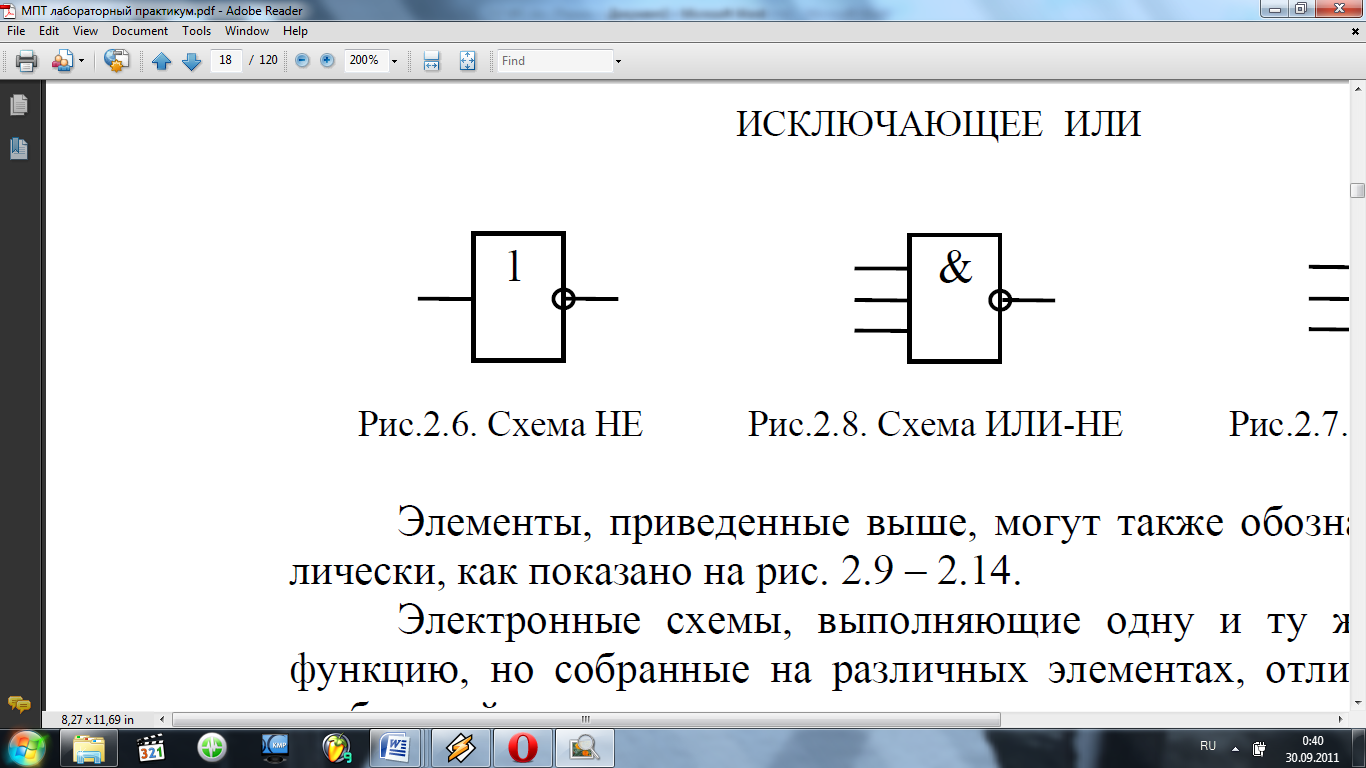

Графическое обозначениелогического элемента НЕ представлено на рисунке 1.

Рисунок 1. Логический элемент НЕ

Таблица 1. Таблица функциональности логического элемента НЕ

|

Входной уровень сигнала |

Выходной уровень сигнала |

|

|

Теория |

|

0 |

1 |

|

1 |

0 |

2) Логическая функция И

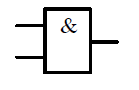

Графическое обозначение логического элемента И представлено на рисунке 2.

Рисунок 2. Логический элемент И

Таблица 2. Таблица функциональности логического элемента И

|

Входные уровни сигналов |

Выходные уровни сигналов |

|

|

X1 |

X2 |

Теория |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

3) Логическая функция ИЛИ

Графическое обозначение логического элемента ИЛИ представлено на рисунке 3.

Рисунок 3. Логический элемент ИЛИ

Таблица 3. Таблица функциональности логического элемента ИЛИ

|

Входные уровни сигналов |

Выходные уровни сигналов |

|

|

X1 |

X2 |

Теория |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

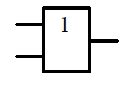

4) Логическая функция Исключающее ИЛИ.

Графическое обозначение логического элемента Исключающее ИЛИ представлено на рисунке 4.

Рисунок 4. Логический элемент исключающее ИЛИ

Таблица 4. Таблица функциональности логического элемента Исключающее ИЛИ

|

Входные уровни сигналов |

Выходные уровни сигналов |

|

|

X1 |

X2 |

Теория |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

5) Логическая функция 2И-НЕ.

Графическое обозначение логического элемента 2И-НЕ представлено на рисунке 5.

Рисунок 5. Логический элемент 2И-НЕ

Таблица 5. Таблица функциональности логического элемента 2И-НЕ

|

Входные уровни сигналов |

Выходные уровни сигналов |

|

|

X1 |

X2 |

Теория |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

6) Логическая функция 2ИЛИ-НЕ.

Графическое обозначение логического элемента 2ИЛИ-НЕ представлено на рисунке 6

Рисунок 6. Логический элемент 2ИЛИ-НЕ.

Таблица 6. Таблица функциональности логического элемента 2ИЛИ-НЕ

|

Входные уровни сигналов |

Выходные уровни сигналов |

|

|

X1 |

X2 |

Теория |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Ход работы:

Заданное уравнение: Y1=(X1+X2)X3

Схема № 1:

Результаты исследования приведены в таблице 7. Таблица 7. Результаты исследования первой схемы

|

Входные уровни сигнала |

Выходные уровни сигнала |

||||

|

X1 |

X2 |

X3 |

Yэксп |

Yтеор |

|

|

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

0 |

0 |

0 |

|

|

1 |

1 |

0 |

0 |

0 |

|

|

0 |

0 |

1 |

0 |

0 |

|

|

1 |

0 |

1 |

1 |

1 |

|

|

0 |

1 |

1 |

1 |

1 |

|

|

1 |

1 |

1 |

1 |

1 |

|

Заданное

уравнение: Y2=(X1+X2)

Схема № 2:

Результаты исследования приведены в таблице 8. Таблица 8. Результаты исследования первой схемы

|

Входные уровни сигнала |

Выходные уровни сигнала |

||||

|

X1 |

X2 |

X3 |

Yэксп |

Yтеор |

|

|

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

0 |

0 |

|

|

0 |

1 |

0 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

|

|

0 |

0 |

1 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

0 |

|

|

0 |

1 |

1 |

1 |

1 |

|

|

1 |

1 |

1 |

0 |

0 |

|

Выполнение работы с помощью программы "Electronics Workbench"

Заданное уравнение: Y1=(X1+X2)X3

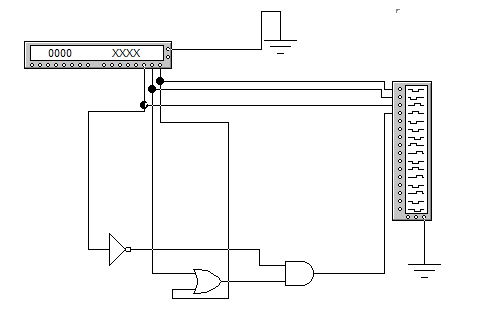

Рисунок 7. Модель схемы в программной среде Electronics Workbench

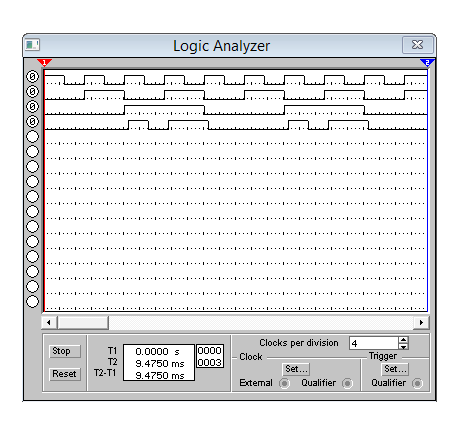

Рисунок 8. Осциллограмма подачи сигналов и получение результата на выходе схемы

Заданное

уравнение: Y2=(X1+X2)

Рисунок 9. Модель схемы в программной среде Electronics Workbench

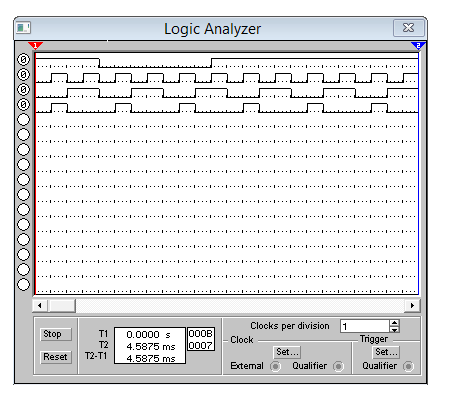

Рисунок 10. Осциллограмма подачи сигналов и получение результата на выходе схемы

Вывод: в ходе лабораторной работы мы ознакомились с базовыми логическими элементами и разработали схему для заданных уравнений. После чего она была проверена на лабораторной стенде и теоретические результаты сошлись с практическими. Так же данные схемы были реализованы в программной среде Electronics Workbench. Результаты были представлены в виде осциллограмм.