TsMU_variant_14

.docЗадание №1

Составить 4-х разрядное десятичное число путем добавления к числу 14, составляющему старшие разряды, двух младших разрядов, соответствующих последним цифрам вашей зачетной книжки (порядковому номеру), например, 1101,1102 и т.д. Используя методы перевода чисел из одной позиционной системы счисления в другую, перевести сформированное десятичной число в двоичную систему счисления, а полученное двоичное – снова в десятичное.

Решение:

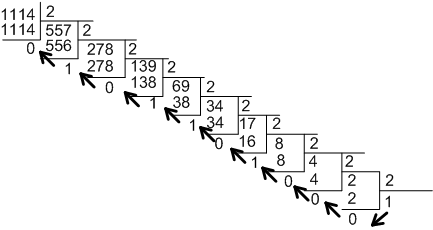

В соответствии с номером зачётной книжки 14, получим число 1114, произведём его перевод в двоичную форму:

Таким образом: 111410=100010110102.

Переведём полученное число из двоичной формы в десятичную:

100011111102=0·20+1·21+0·22+1·23+1·24+0·25+1·26+0·27+0·28+0·29+1·210=111410.

Задание №2

-

По принципиальной электрической схеме провести анализ и установить функциональную зависимость в виде формул алгебры логики и таблицы истинности.

2. По таблице истинности составить совершенную конъюнктивную нормальную форму (СКНФ).

-

Минимизировать логическую функцию любым известным методом.

-

Синтезировать комбинационное устройство в базисе И-НЕ, ИЛИ-НЕ.

-

Синтезировать комбинационное устройство в заданных базисах 2-х входовых элементов 2И-НЕ (Шеффера), 2ИЛИ-НЕ(Пирса).

-

Проверить работу синтезированного устройства путем моделирования в системе Matlab (Simulink) или Multisim.

Решение:

|

№ варианта |

ДД1 |

ДД2 |

ДД3 |

ДД4 |

ДД5 |

ДД6 |

ДД7 |

ДД8 |

|

14 |

- |

* |

ИЛИ-НЕ |

И-НЕ |

ИЛИ-НЕ |

И |

ИЛИ-НЕ |

И-НЕ |

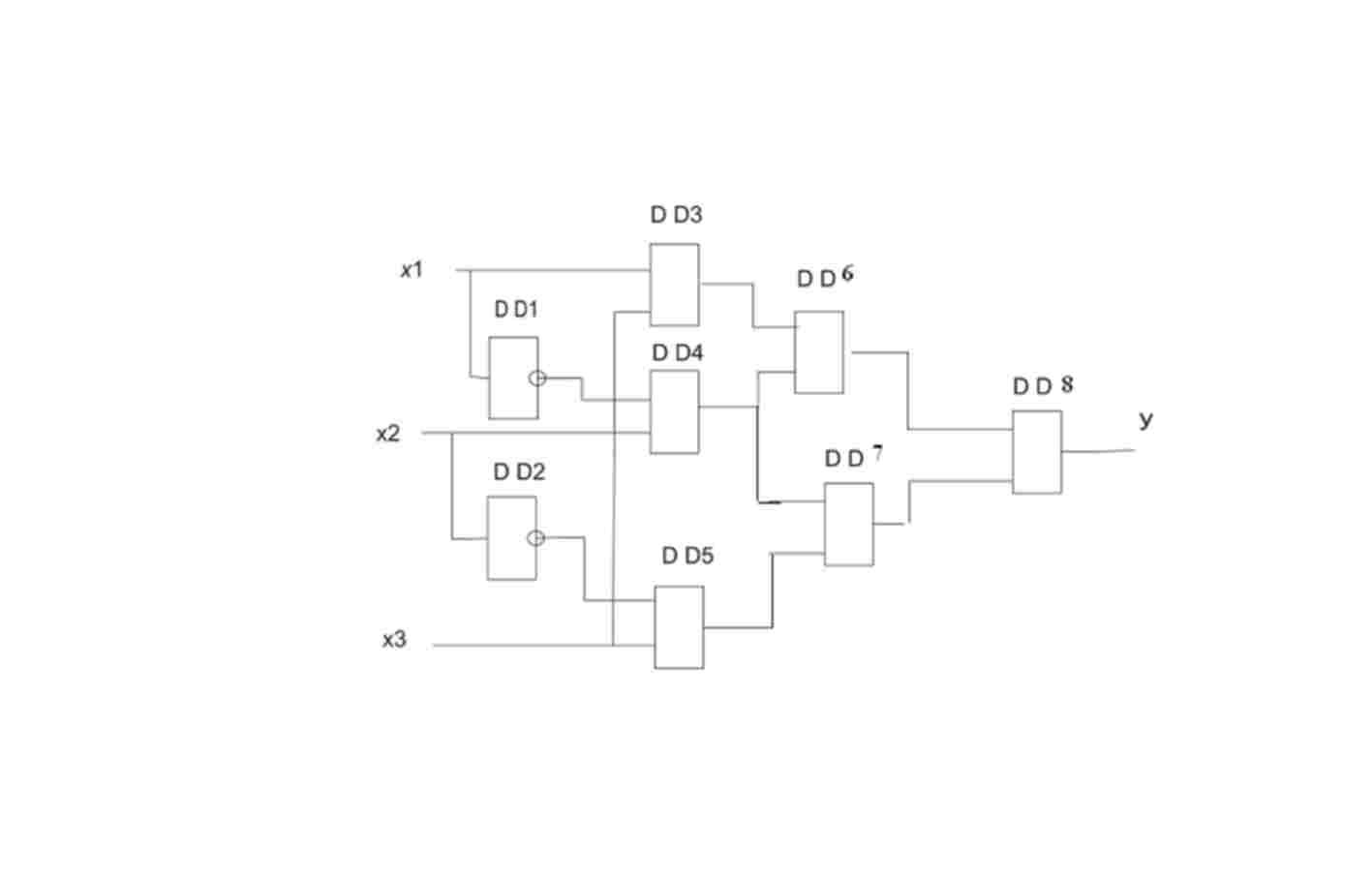

Рисунок 1 – Исходная схема для расчёта

DD1, DD2 – инверторы, прочерк в таблице соответствует отсутствию инвертора, знак "*" соответствует наличию инвертора в схеме.

Исходные данные:

ДД1–-; ДД2– НЕ; ДД3 –ИЛИ-НЕ; ДД4–И-НЕ; ДД5 – ИЛИ-НЕ; ДД6 –И, ДД7 – ИЛИ-НЕ, ДД8 - И-НЕ.

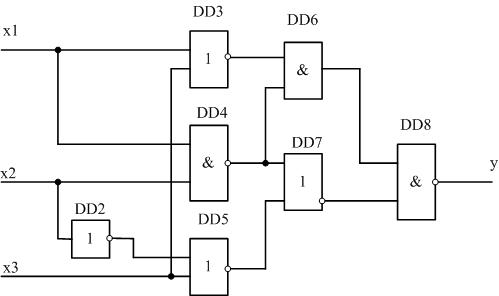

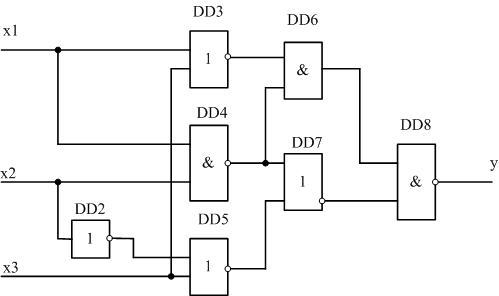

Изобразим схему в соответствии с заданием (см. рисунок 2).

Рисунок 2 – Схема для расчёта

Решение.

-

Установим функциональную зависимость.

Обозначим промежуточные переменные.

![]()

Исключим внутренние промежуточные переменные путем подстановки

![]() .

.

-

Составим таблицу истинности.

|

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

3. 3. Запишем функцию в совершенной дизьюнктивной нормальной форме (СДНФ)

![]()

Каждому члену СДНФ соответствует единичное значение функции.

-

Проведем операции склеивания и поглощения. Склеивание и поглощение не требуется.

-

Получаем минимальную дизьюнктивную форму

![]() .

.

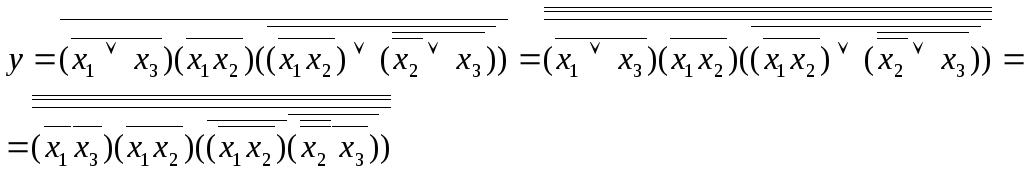

Построим структурную схему устройства по полученной минимальной ДНФ (см. рисунок 3)

Рисунок 3 – Схема после минимизации функции

В схеме использовано 7 элементов.

9. Синтезируем схему устройства по полученной минимальной ДНФ (см. рисунок 3) в базисе 2И-НЕ (Шеффера)

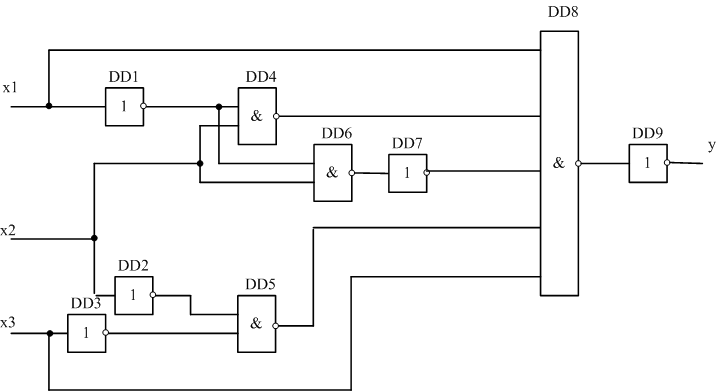

10. Построим структурную схему устройства в базисе 2И-НЕ (см. рисунок 4).

Рисунок 4 – Схема в базисе И-НЕ

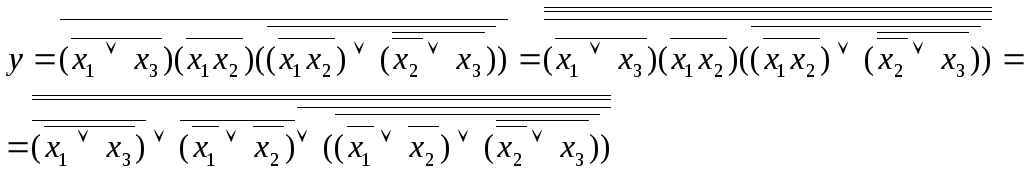

11. Для построения комбинационной схемы в базисе ИЛИ-НЕ составляем совершенную коньюнктивную нормальную форму

![]()

Каждому члену произведения СКНФ соответствует нулевое значение функции.

12.Произведем склеивание и поглощение, получим сокращенную форму

Склеивание и поглощение не требуется.

-

Получаем минимальную дизьюнктивную форму

![]() .

.

16. Построим структурную схему устройства по полученной минимальной КНФ. (см. рисунок 5).

Рисунок 5 – Схема, после минимизации СКНФ

В схеме использовано 7 элементов.

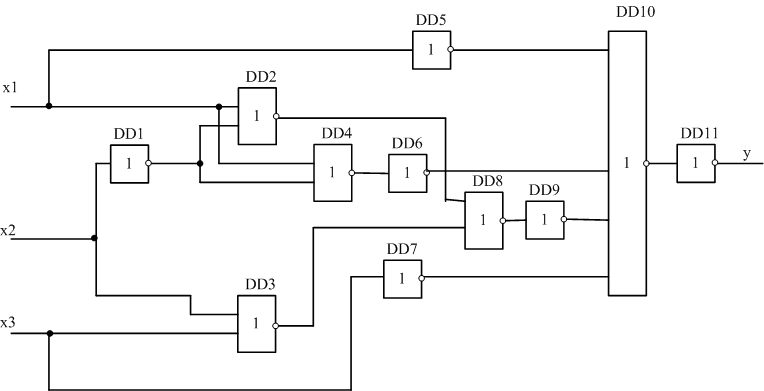

17. Синтезируем схему в базисе ИЛИ-НЕ, используя формулы де Моргана. В результате получим

Построим структурную схему устройства в базисе ИЛИ-НЕ (см. рисунок 6).

Рисунок 6 – Схема в базисе ИЛИ-НЕ

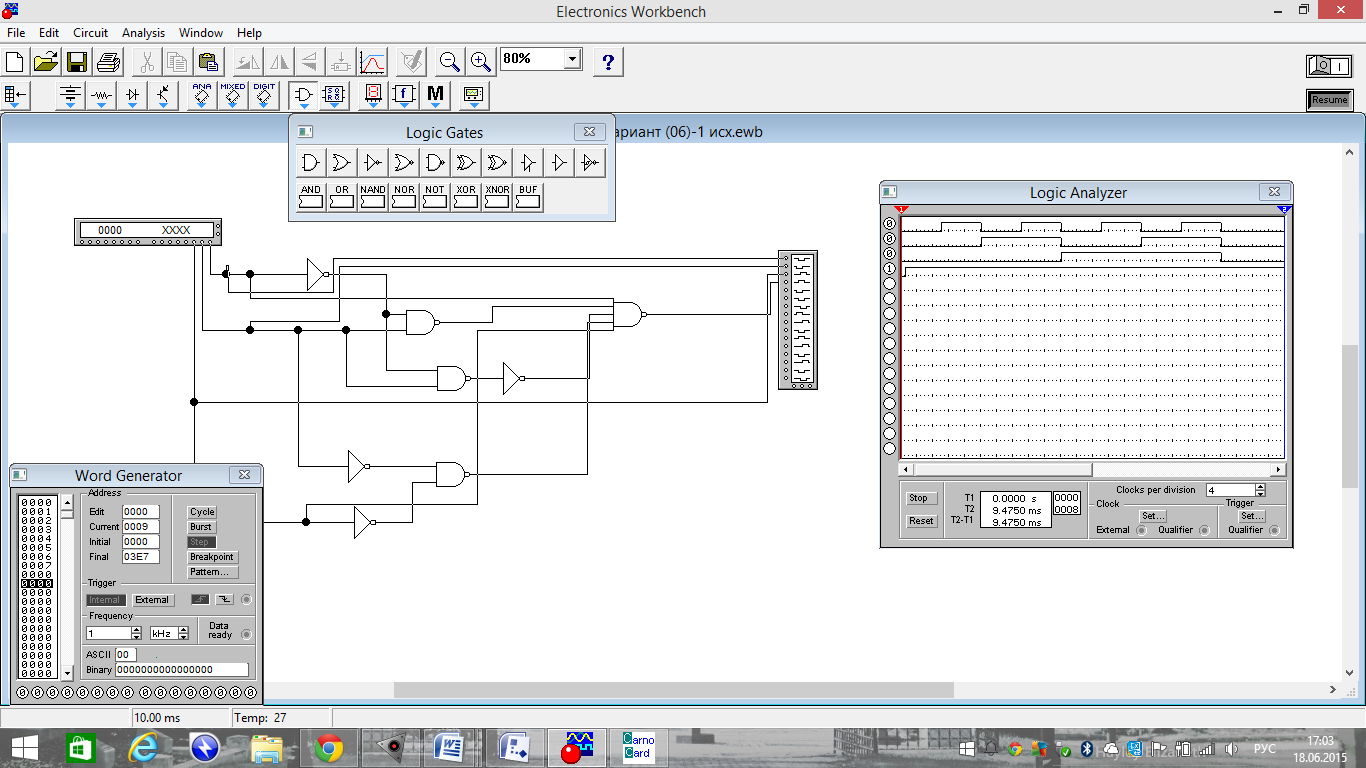

Модель комбинационной схемы в базисе И-НЕ, временные диаграммы входных и выходного сигналов (см. рисунок 7).

Рисунок 7 - Модель комбинационной схемы в базисе И-НЕ, временные диаграммы входных и выходного сигналов

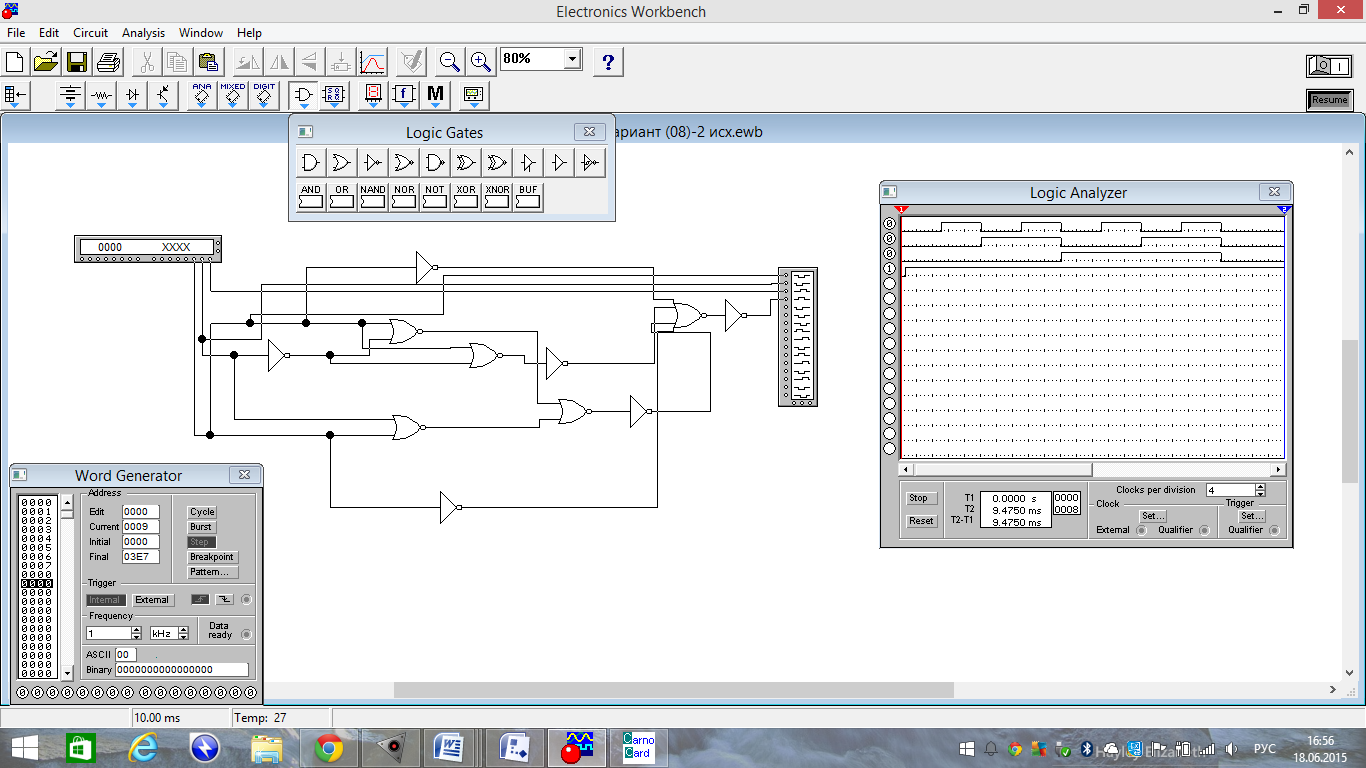

Рисунок 7 - Модель комбинационной схемы в базисе ИЛИ-НЕ, временные диаграммы входных и выходного сигналов

Как видно из временных диаграмм синтезированные схемы и модели функционируют в соответствии с таблицей истинности.

Задание №3.

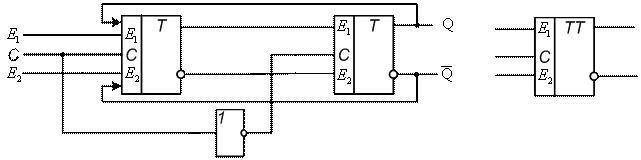

14. Изобразить условно графически двух ступенчатый D-триггер.

Задать произвольно воздействия по его информационным входам.

Синхронным

двухступенчатым (двухтактным) триггером

называется схема, состоящая из двух

одноступенчатых синхронных триггеров.

Одновременный прием информации в

обе ступени такого триггера запрещён.

При наличии синхроимпульса на

входе «С» происходит

приём информации, определяемой состоянием

логических входов ![]() ,

, ![]() ,

в первую ступень триггера. Вторая ступень

триггера не переключается и сохраняет

ранее записанную информацию (смю рисунок

3.1).

,

в первую ступень триггера. Вторая ступень

триггера не переключается и сохраняет

ранее записанную информацию (смю рисунок

3.1).

Рисунок 3.1 - Структура двухступенчатого триггера и его условное обозначение

После снятия синхроимпульса приём информации в первую ступень триггера запрещается, а уже имеющаяся информация из первой ступени переписывается во вторую и появляется на выходе триггера. Такая последовательность в приёме информации достигается включением инвертора в цепь синхроимпульса второй ступени. Используемый принцип записи позволяет исключить потерю информации, когда один и тот же элемент памяти одновременно используется в качестве приёмника и источника информации.

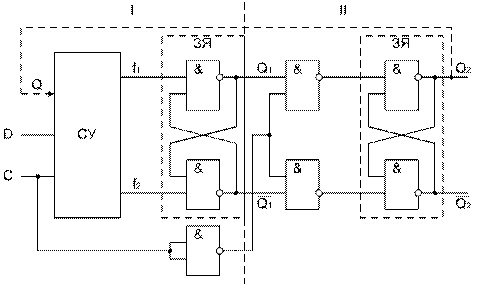

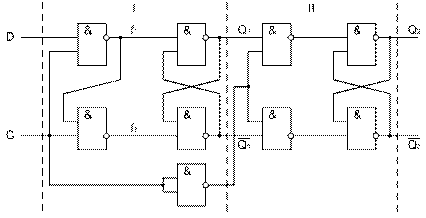

Методику логического проектирования двухступенчатых триггеров рассмотрим на примере синтеза двухтактного D-триггера со статическим управлением записью (см. рисунок 3.2).

Рисунок 3.2 - Синтез двухступенчатого D-триггера

Как и в случае с одноступенчатым триггером, первая ступень двухтактного триггера включает в себя схему управления и реализованную в выбранном базисе запоминающую ячейку. Вторая ступень триггера содержит ЗЯ и два логических элемента «И–НЕ». Данные элементы выполняют роль логических ключей, управляемых синхроимпульсом, и обеспечивают прохождение сигнала с первой ступени триггера во вторую.

При

выбранном типе ЗЯ синтез триггера

заключается в определении

функций ![]() ,

, ![]() возбуждения

ЗЯ первой ступени и минимизации этих

функций в заданном базисе. Далее, на

основании полученных для функций

возбуждения

ЗЯ первой ступени и минимизации этих

функций в заданном базисе. Далее, на

основании полученных для функций ![]() и

и ![]() формул

строится схема управления триггера и

добавляются остальные, входящие в состав

двухступенчатого триггера, функциональные

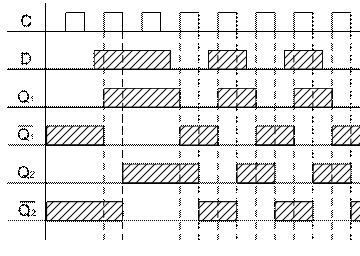

элементы (см. рисунок 3.3). Функционирование

синтезированного двухступенчатого

D-триггера отображено на временной

диаграмме, представленной на рисунок

3.4.

формул

строится схема управления триггера и

добавляются остальные, входящие в состав

двухступенчатого триггера, функциональные

элементы (см. рисунок 3.3). Функционирование

синтезированного двухступенчатого

D-триггера отображено на временной

диаграмме, представленной на рисунок

3.4.

Рисунок 3.3 - Синтез двухступенчатого D-триггера

Рисунок 3.4 - Временная диаграмма работы синтезированного двухступенчатого D-триггера

ЛИТЕРАТУРА

1. Браммер Ю.А. Цифровые устройства: Учеб. пособие для вузов. –М.:Высш. шк., 2004. –229с.

2. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для втузов.- СПб.: Политехника, 1996.- 885 с.