203-elektrotehnika-i-elektronika-elektronika-26mb

.pdf

таблица истинности имеет вид, показанный в табл. 10.1.

Таблица 10.1

А |

0 |

1 |

Х1 0

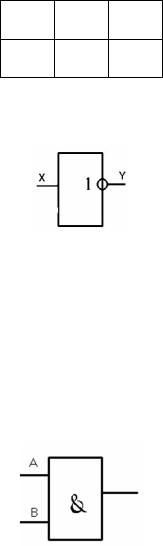

Графически эта функция обозначается кружком на входе или вы- ходе логического символа в виде прямоугольника (рис. 10.1).

Рис. 10.1. Графическое изображение логического элемента, выполняющего функцию НЕ

Логическое умножение (конъюнкция) двух переменных А и В есть логическая функция X, которая истинна только тогда, когда од- новременно истинны входные переменные А и В. Логическое умно- жение записывается в виде

X = A B или X = A B .

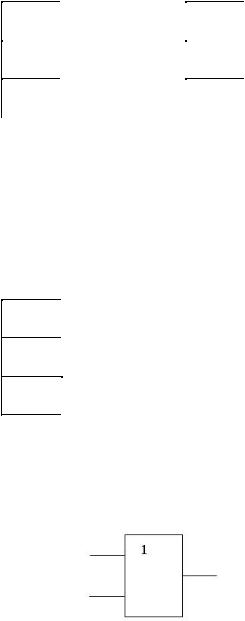

Графически элемент И обозначается в виде прямоугольника, внутри которого ставится символ & (рис. 10.2).

Рис. 10.2. Графическое изображение логического элемента И

Ниже представлена таблица истинности логического элемента И

(табл. 10.2).

81

|

|

|

|

Таблица 10.2 |

|

|

|

|

|

|

|

А |

0 |

0 |

1 |

|

1 |

|

|

|

|

|

|

В |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

Х |

0 |

0 |

0 |

|

1 |

|

|

|

|

|

|

Пример выполнения функции умножения: устройство, подклю- ченное через согласующий усилитель к выходу элемента И сработает только тогда, когда на входах этого логического элемента сработают оба датчика, контролирующие температуру и влажность, например, в стиральной машине.

Логическое сложение переменных А и В есть логическая функция

Х, которая истинна, когда хотя бы одна из входных переменных истинна. Таблица истинности для этого случая имеет вид, показанный в табл. 10.3.

|

|

|

|

Таблица 10.3 |

|

|

|

|

|

|

|

А |

0 |

0 |

1 |

|

1 |

|

|

|

|

|

|

В |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

Х |

0 |

1 |

1 |

|

1 |

|

|

|

|

|

|

Ей соответствует логическая функция в символах алгебры логики

X = A + B = A B .

Графическое изображение логического элемента ИЛИ показано на рис. 10.3.

Рис. 10.3. Графическое изображение логического элемента ИЛИ

82

Указанные функции позволяют реализовать практически любую логическую зависимость.

Кроме приведенных выше логических функций рассмотрим еще три. Это комбинированные функции: И-НЕ, ИЛИ-НЕ и исклю-

чающее ИЛИ.

Функция И-НЕ: X = A B .

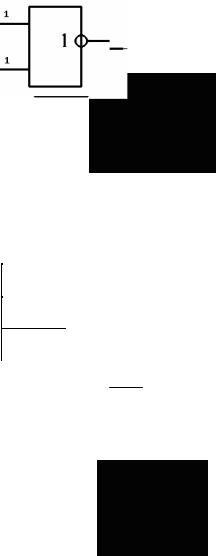

Графическое изображение логического элемента И-НЕ показано на рис. 10.4.

Рис. 10.4. Графическое изображение логического элемента И-НЕ

Таблица истинности для И-НЕ имеет вид, показанный в табл. 10.4.

|

|

|

|

Таблица 10.4 |

|

|

|

|

|

|

|

А |

0 |

0 |

1 |

|

1 |

|

|

|

|

|

|

В |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

Х |

1 |

0 |

0 |

|

0 |

|

|

|

|

|

|

Функция ИЛИ-НЕ: X = A + B .

Графическое изображение логического элемента ИЛИ-НЕ пока- зано на рис. 10.5.

Рис. 10.5. Графическое изображение логического элемента ИЛИ-НЕ

83

Таблица истинности для ИЛИ-НЕ имеет вид, показанный в табл. 10.5.

|

|

|

|

Таблица 10.5 |

|

|

|

|

|

|

|

А |

0 |

0 |

1 |

|

1 |

|

|

|

|

|

|

В |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

Х |

1 |

1 |

1 |

|

0 |

|

|

|

|

|

|

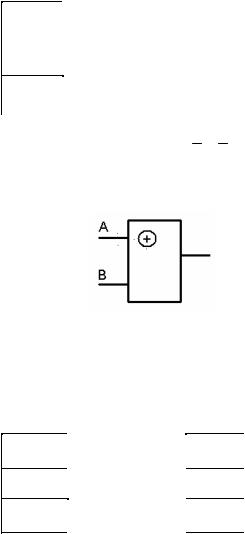

Функция исключающее ИЛИ: X = AB AB .

Графическое изображение логического элемента исключающее ИЛИ показано на рис. 10.6.

Рис. 10.6. Графическое изображение логического элемента

исключающее ИЛИ

Таблица истинности для элемента исключающее ИЛИ имеет вид, показанный в табл. 10.6.

|

|

|

|

Таблица 10.6 |

|

|

|

|

|

|

|

А |

0 |

0 |

1 |

|

1 |

|

|

|

|

|

|

В |

0 |

1 |

0 |

|

1 |

|

|

|

|

|

|

Х |

0 |

1 |

1 |

|

0 |

|

|

|

|

|

|

Количество входов элементов И, ИЛИ, И-НЕ, ИЛИ-НЕ может быть больше двух.

Все логические элементы исполняются по интегральной технологии, т.е. на одном полупроводниковом кристалле, на котором формируется вся схема, включая транзисторы, диоды, резисторы.

84

В зависимости от технологической структуры и принципа преобразования сигналов различают несколько типов логики.

Наиболее широко используются ТТЛ-логика (транзисторно-

транзисторная) и МДП-логика (металл–диэлектрик–полупроводник).

Ниже приведена сравнительная таблица параметров ТТЛ и МДП- логики (табл. 10.7).

|

|

|

|

|

Таблица 10.7 |

|

|

|

|

|

|

Тип |

Напряжение |

Потребляемый |

Уровень |

Уровень |

Быстродействие, |

питания, |

логического |

логической |

|||

логики |

В |

ток, мА |

«0», В |

«1», В |

с |

|

|

|

|||

|

|

|

|

|

|

ТТЛ |

+5 |

25…35 |

0,24 |

3,5 |

10–9 |

|

|

|

|

|

|

МДП |

+3 … +15 |

0,1 |

0 |

+Е |

10–7 |

|

|

|

|

|

|

Дешифратор – комбинационная схема, обеспечивающая форми- рование для схемы с n входами активного сигнала только на одном из его выходов. Максимальное количество выходов в дешифраторе может быть равным 2n.

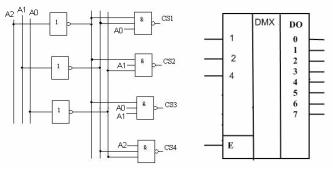

На рис. 10.7 приведен фрагмент схемы дешифратора, отражаю- щий принцип дешифрации двоичного кода.

Рис. 10.7. Схема, иллюстрирующая принцип построения дешифратора-демультиплексора и его условное обозначение

Демультиплексор имеет дополнительный информационный вход E. Состояние на этом входе будет передаваться на выбранный выход.

Функции мультиплексора (рис. 10.8) состоят в том, чтобы один из входных сигналов передать на общий выход.

85

Рис. 10.8. Структура и условное обозначение мультиплексора

10.3.Подготовка к работе

1.Освоить основные положения теоретического введения.

2.Начертить в лабораторной тетради принципиальные схемы и условные обозначения логических элементов, мультиплексора и де- мультиплексора.

3.Подготовить таблицы для записи значений напряжений, соот- ветствующих логическим уровням для входов и выходов логических элементов ТТЛ и КМОП.

4.Подготовить таблицы состояний для исследуемых устройств.

5.Начертить в лабораторной тетради схемы проведения эксперимента.

10.4.Порядок выполнения работы

Задание 1. Определение логических и физических уровней для входов и выходов логических элементов

1. Собрать в рабочем окне схему, изображенную на рис. 10.9. Ло- гический элемент «НЕ» серии LS (серия ТТЛ с диодами Шоттки).

Рис. 10.9. Схема измерения значений напряжений, соответствующих логическим уровням для входов и выходов логических элементов

86

2.Для функционального генератора установить режим: треуголь- ные импульсы с амплитудой 2 В, смещением 2 В.

3.Измерить напряжение логического нуля и единицы по входу и выходу.

4.Выполнить те же измерения для элемента КМОП (CMOS 4009BCL-10V) при напряжении питания 5 В.

5.Результаты измерений занести в табл. 10.8.

|

|

|

|

Таблица 10.8 |

|

|

|

|

|

Технология |

Uвх0 |

Uвх1 |

Uвых0 |

Uвых1 |

|

|

|

|

|

ТТЛ |

|

|

|

|

|

|

|

|

|

КМОП |

|

|

|

|

|

|

|

|

|

6. Составить на логических элементах комбинационную схему, на выходе которой высокий уровень напряжения (логическая «1») появляется только при значениях сигналов на входах, заданных в табл. 10.9.

|

|

|

|

|

|

|

|

Таблица 10.9 |

|

|

|

|

|

|

|

|

|

|

|

Номера |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

8 |

вариантов |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

x2 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

x3 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|

Задание 2. Изучение работы дешифратора

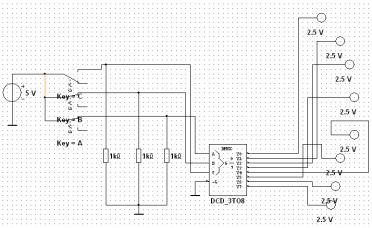

1. Собрать в рабочем окне схему, изображенную на рис. 10.10. Дешифратор выбрать из серии элементов digital – DCD_3TO8 (один из восьми). В качестве индикаторов использованы элемен- ты probe. Входы A, B, C соответствуют весам 1, 2, 4. Таким обра- зом, при замкнутых ключах A и C должен быть активирован индикатор 5.

87

Рис. 10.10. Схема для исследования дешифратора

2.Проверить работу дешифратора при всех возможных комбина- циях положений ключей.

3.Результаты эксперимента (состояние ключей и номер активиро- ванного выхода Na) записать в табл. 10.10.

Таблица 10.10

A–C |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

|

|

|

|

|

|

|

|

Na |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Задание 3. Изучение работы демультиплексора

Микросхема 74LS138 представляет собой дешифратор- демультиплексор (3TO8-DECODER). Для работы в режиме дешифра- тора на выводе G1 должна быть установлена логическая «1», а на выводах G2A, G2B – логический «0».

При установлении на входах А, В, С определенной комбинации ло- гических уровней высокий уровень будет на одном из выходов.

Если вывод G1 использовать как линию передачи информации, то ее можно вывести на любой из восьми выходов Y. В этом случае реализуется работа в режиме демультиплексора (рис. 10.11).

88

Рис. 10.11. Схема для исследования демультиплексора

1.Собрать в рабочем окне схему, изображенную на рис. 10.11.

2.К выводу G1 подключить источник прямоугольных импульсов

счастотой 2 Гц.

3.Записать номер выхода Y на который передаются импульсы с входа G1 при различных комбинациях состояния ключей.

4.Результаты эксперимента занести в табл. 10.11.

Таблица 10.11

A–C |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

|

|

|

|

|

|

|

|

|

Y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

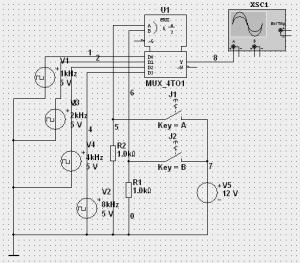

Задание 4. Изучение работы мультиплексора

Мультиплексор имеет четыре цифровых информационных входов (D0 – D3), два адресных входа (A, B), вход разрешения (G), выход

(Y)и инверсный выход (W).

1.Собрать в рабочем окне схему, изображенную на рис. 10.12. На входы мультиплексора поступают сигналы от источников

прямоугольных импульсов V1–V8 с частотами 1, 2, 4, 8 кГц. Из- меняя состояние ключей A и B, к выходу подключается один из 4 входов.

89

Рис. 10.12. Исследование работы мультиплексора

2.Записать значение частоты импульсов на выходе при различ- ных комбинациях состояния ключей.

3.Результаты эксперимента занести в табл. 10.12.

|

|

|

|

Таблица 10.12 |

|

|

|

|

|

|

|

A–B |

00 |

01 |

10 |

|

11 |

|

|

|

|

|

|

F, Гц |

|

|

|

|

|

|

|

|

|

|

|

10.5.Содержание отчета

1.Наименование и цель работы.

2.Необходимые теоретические сведения.

3.Изображения электрических схем испытаний.

4.Таблицы результатов измерений и расчетов.

5.Выводы по работе.

Контрольные вопросы

1. Какая логическая функция описывает поведение системы пуска трехфазного двигателя (двигатель может быть запущен, если три датчика подтверждают наличие фазных напряжений)?

90