Прерывания pci: inTx#, pme#, msi и serr#

Устройства РСIимеют возможность сигнализации об асинхронных событиях с помощью прерываний. На шине РСI возможны четыре типа сигнализации прерываний:

традиционная проводная сигнализация по линиям INTx:

проводная сигнализация событий управления энергопотреблением по линии РМЕ#;

сигнализация с помощью сообщений - MSI;

сигнализация фатальной ошибки по линии SERR#.

Аппаратные прерывания в рс - совместимых компьютерах

Аппаратные прерывания обеспечивают реакцию процессора на события, происходящие асинхронно по отношению к исполняемому программному коду. Аппаратные прерывания делятся на маскируемые и немаскируемые. Процессор х86 по сигналу прерывания приостанавливает выполнение текущего потока инструкций, сохраняя в стеке состояние (флаги и адрес возврата), и выполняет процедуру обработки прерывания. Конкретная процедура обработки выбирается из таблицы прерываний по вектору прерывания - однобайтному номеру элемента в данной таблице. Вектор прерывания доводится до процессора разными способами: для немаскируемого прерывания он фиксирован, для маскируемых прерываний его сообщает специальныйконтроллер прерываний. Кроме аппаратных прерываний у процессоров х86 имеются такжевнутренние прерывания -исключения (exceptions), связанные с особыми случаями выполнения инструкций, ипрограммные прерывания. Для исключений вектор определяется самим особым условием, и под исключения фирмой Intel зарезервированы первые 32 вектора (0-31 или 00-1Fh). В программных прерываниях номер вектора содержится в самой инструкции (программные прерывания - это лишь специфический способ вызова процедур по номеру, с предварительным сохранением в стеке регистра флагов). Все эти прерывания используют один и тот же набор из 256 возможных векторов. Исторически сложилось так, что векторы, используемые для аппаратных прерываний, пересекаются с векторами исключений и векторами для, программных прерываний, используемых для вызовов сервисов BIOS и DOS. Таким образом, для ряда номеров векторов процедура, на которую ссылается таблица прерываний, должна в начале содержать программный код, определяющий, по какому поводу она вызвана: из-за исключения, аппаратного прерывания или же для вызова какого-то системного сервиса. Таким образом, процедура, собственно и обеспечивающая реакцию процессора на то самое асинхронное событие, будет вызвана только после ряда действий по идентификации источника прерываний. Один и тот же вектор прерывания может использоваться и несколькими периферийными устройствами - это так называемоеразделяемое использование прерываний.

Вызов процедуры обслуживания прерываний в реальном и защищенном режимах процессора существенно различается:

в реальном режиме таблица прерываний содержит 4-байтные дальние указатели (сегмент и смещение) на соответствующие процедуры, которые вызываются дальним вызовом (Call Farс предварительным сохранением флагов). Размер (256х4 байт) и положение таблицы (начинается с адреса 0) фиксированы;

в защищенном режиме (и в его частном случае - режиме V86) таблица содержит 8-байтные дескрипторы прерываний, которые могут быть шлюзами прерываний (Interrupt Gate), ловушек (Тгар Gate) или задач (Task Gate). Размер таблицы может быть уменьшен (максимальный - 256х8 байт), положение таблицы может меняться (определяется содержимым регистраIDTпроцессора). Код обработчика прерываний должен быть не менее привилегированным, чем код прерываемой задачи (иначе сработает исключение защиты). По этой причине обработчики прерываний должны работать на уровне ядра ОС (на нулевом уровне привилегий). Смена уровня привилегии при вызове обработчика приводит к дополнительным затратам времени на переопределение стека. Прерывания, вызывающие переключение задач (черезTask Gate), расходуют значительное время на переключение контекста - выгрузку регистров процессора в сегмент состояния старой задачи и их загрузку из сегмента состояния новой.

Номера векторов, используемых для аппаратных прерываний в операционных системах защищенного режима, отличаются от номеров, используемых в ОС реального режима, чтобы исключить их конфликты с векторами, используемыми для исключений процессора.

На немаскируемое прерывание (NMI - Non-Maskable Interrupt) процессор реагирует всегда (если обслуживание предыдущего NMI завершено); этому прерыванию соответствует фиксированный вектор 2. Немаскируемые прерывания в РС используются для сигнализации о фатальных аппаратных ошибках. Сигнал на линиюNMI приходит от схем контроля памяти (четности илиЕСС), от линий контроля шины ISA (IOCHK) и шины РСI (SERR#). СигналNMI блокируется до входа процессора установкой в 1 бита 7 порта 070h, отдельные источники разрешаются и идентифицируются битами порта 061h:

бит 2 R/W -ERP- разрешение контроля ОЗУ и сигналаSERR#шины PCI;

бит 3 R/W -ЕIС- разрешение контроля шины ISA;

бит 6 R - IOCHK- ошибка контроля на шине ISA (сигналIOCHK#);

бит 7 R - РСК - ошибка четности ОЗУ или сигналSERR# на шине PCI.

Реакция процессора на маскируемые прерывания может быть задержана сбросом его внутреннего флагаIF(инструкцияCLIзапрещает прерывания,SТI - разрешает). Маскируемые прерывания используются для сигнализации о событиях в устройствах. По возникновении события, требующего реакции, адаптер (контроллер) устройства формируетзапрос прерывания, который поступает на вход контроллера прерываний. Задача контроллера прерываний - довести до процессора запрос прерывания и сообщить вектор, по которому выбирается программная процедура обработки прерываний.

Процедура обработки прерывания от устройства должна выполнить действия по обслуживанию данного устройства, включая сброс его запроса для обеспечения возможности реакции на следующие события, и послать команды завершения в контроллер прерываний. Вызывая процедуру обработки, процессор автоматически сохраняет в стеке значение всех флагов и сбрасывает флаг IF, что запрещает маскируемые прерывания. При возврате из этой процедуры (по инструкцииIRET) процессор восстанавливает сохраненные флаги, в том числе и установленный (до прерывания)IF, что снова разрешает прерывания. Если во время работы обработчика прерываний требуется реакция на иные прерывания (более приоритетные), то в обработчике должна присутствовать инструкцияSТI. Особенно это касается длинных обработчиков; здесь инструкцияSТIдолжна вводиться как можно раньше, сразу после критической (не допускающей прерываний) секции. Следующие прерывания того же или более низкого уровня приоритета контроллер прерываний будет обслуживать только после получения команды завершения прерыванияЕОI(End Of Interrupt).

В IBM РС - совместимых компьютерах применяется два основных типа контроллеров прерываний:

PIC (Peripheral Interrupt Controller) - периферийный контроллер прерываний, программно совместимый с «историческим» контроллером 8259А, применявшимся еще в первых моделях IBM РС. Со времен IBM РС/АТ применяется связка из пары каскадно-соединенных PIC, позволяющая обслуживать до 15 линий запросов прерываний;

APIC (Advanced Peripheral Interrupt Controller) –усовершенствованный периферийный контроллер прерываний, введенный для поддержки мультипроцессорных систем в компьютеры на базе процессоров 4 -5 поколений (486 и Pentium) и используемый поныне для более поздних моделей процессоров. Кроме поддержки мультипроцессорных конфигураций современный АРIС позволяет увеличивать число доступных линий прерываний и обрабатывать запросы прерываний от устройств PCI, посылаемые через механизм сообщений (MSI). Компьютер, оснащенный контроллером АРIС, обязательно имеет возможность функционировать и в режиме, совместимом со стандартной связкой пары PIC. Этот режим включается по аппаратному сбросу (и включению питания), что позволяет использовать старые ОС и приложения MS DOS, «незнающие» - APIC и мультипроцессирования.

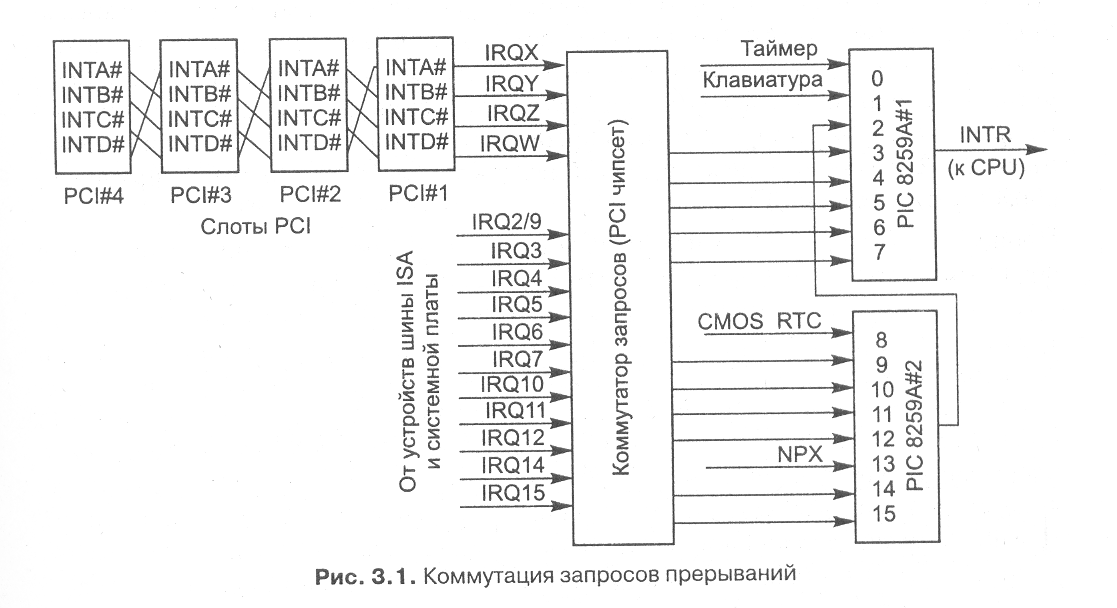

Традиционная схема формирования запросов прерываний с использованием пары PIC изображена на рис. 2.

Рис. 2 - Коммутация запросов прерываний.

На входы контроллеров прерываний поступают запросы от системных устройств (клавиатура, системный таймер, СМОS-таймер, сопроцессор), периферийных контроллеров системной платы и карт расширения. Традиционно все линии запросов, не занятые перечисленными устройствами, присутствуют на всех слотах шины ISA/ ElSA. Эти линии обозначаются как IRQxи имеют общепринятое назначение (табл. 2). Часть этих линий отдается в распоряжение шины PCI. В таблице отражены и приоритеты прерываний - запросы расположены в порядке их убывания. Номера векторов, соответствующих линиям запросов контроллеров, система приоритетов и некоторые другие параметры задаются программно при инициализации контроллеров. Эти основные настройки остаются традиционными для обеспечения совместимости с программным обеспечением, но различаются для ОС реального и защищенного режимов. Так, например, в ОС Windows базовые векторы для ведущего и ведомого контроллеров - 50h и 58h соответственно.

|

Таблица 2. Аппаратные прерывания (в порядке убывания приоритета) | ||||

|

Имя (номер1) |

Вектор 2 |

Вектор 3 |

Контрол- |

Описание |

|

|

|

|

лер/маска |

|

|

NMI |

02h |

|

|

Контроль канала, четность памяти |

|

|

|

|

|

(в ХТ - сопроцессор) |

|

IRQ0 |

08h |

50h |

#1/1 h |

Таймер (канал 0 8253/8254) |

|

IRQ1 |

09h |

51h |

#1/2h |

Клавиатура |

|

IRQ2 |

0Ah |

52h |

#1/4h |

ХТ - резерв, АТ - недоступно |

|

|

|

|

|

(подключается каскад IRQ8-IRQ15) |

|

IRQ8 |

70h |

58h |

#2/1 h |

CMOS RТС - часы реального |

|

|

|

|

|

времени |

|

IRQ9 |

71h |

59h |

#2/2h |

Резерв |

|

IRQ10 |

72h |

5Ah |

#2/4h |

Резерв |

|

IRQ11 |

73h |

5Bh |

#2/8h |

Резерв |

|

IRQ12 |

74h |

5Ch |

#2/10h |

PS/2-Mouse (резерв) |

|

IRQ13 |

75h |

5Dh |

#2/20h |

Математический сопроцессор |

|

IRQ14 |

76h |

5Eh |

#2/40h |

НDС - контроллер НЖМД |

|

IRQ15 |

77h |

5Fh |

#2/80h |

Резерв |

|

IRQ3 |

0Bh |

52h |

#1/4h |

СОМ2, СОМ4 |

|

IRQ4 |

0Ch |

53h |

#1/10h |

СОМ1, СОМ3 |

|

IRQ5 |

0Dh |

54h |

#1/20h |

ХТ - НDС, АТ - LPT2, Sound |

|

|

|

|

|

(резерв) |

|

IRQ6 |

0Eh |

55h |

#1/40h |

FDC - контроллер НГМД |

|

IRQ7 |

0Fh |

56h |

#1/80h |

LPT1 - принтер |

|

1 Запросы прерываний 0,1,8 и 13 на шины расширения не выводятся. | ||||

|

2 Указаны номера векторов при работе в реальном режиме процессора. | ||||

|

3 Указаны номера векторов при работе в ОС Windows. |

| |||

Каждому устройству, для поддержки работы которого требуются прерывания, должен быть назначен свой номер прерывания. Назначения номеров прерываний выполняются с двух сторон: во-первых, адаптер, нуждающийся в прерываниях, должен быть сконфигурирован на использование конкретной линии шины (джамперами или программно). Во-вторых, программное обеспечение, поддерживающее данный адаптер, должно быть проинформировано о номере используемого вектора. В процессе назначения прерываний может участвовать система РnР для шин ISA и PCI, для распределения линий запросов между шинами служат специальные параметры CMOS Setup. Современные ОС имеют возможность изменить назначение запросов относительно распределения, сделанного через CMOS Setup.

После того как про изведено конфигурирование системы прерываний (проинициализирован контроллер прерываний, устройствам назначены линии запросов и установлены указатели на процедуры обработки), отработка маскируемых аппаратных прерываний происходит следующим образом:

устройство по событию прерывания возбуждает назначенную ему линию запроса прерывания;

контроллер принимает сигналы запросов от источников прерываний (сигналыIRQx) и при наличии незамаскированного запроса подает сигналобщего запроса прерывания (сигналINTR) процессору х86;

процессор, реагируя на запрос (когда прерывания флагом IFразрешены), сохраняет в стеке содержимое регистра флагов и адрес возврата, после чего формируетшинный цикл lNТА (Interrupt Acknowledge, подтверждение прерывания), который доводится до контроллера прерываний;

в момент получения сигнала INTAконтроллер прерываний фиксирует состояние своих входов запросов - к этому моменту их состояние могло измениться: могли появиться новые запросы или пропасть запрос от «нетерпеливого» устройства. Контроллер анализирует поступившие запросы в соответствии с запрограммированной схемой приоритетов и посылает процессорувектор прерывания, соответствующий самому приоритетному незамаскированному запросу, присутствующему на входе контроллера в момент подачи шинной командыlNTA. При этом контроллер выполняет и некоторые действия в соответствии с установленной приоритетной политикой, учитывающие, какой именно вектор был послан (какой из запросов пошел на обслуживание);

получив вектор прерывания, процессор по его номеру вызывает соответствующую процедуру обработки прерывания. Если данный вектор прерывания используется не только для аппаратных прерываний, но и для исключений и/или программных прерываний, то процедура в первую очередь должна определить, к какому из этих типов относится данное событие. Для этого процедура может обратиться к контроллеру PIC (прочитать регистр ISR) и проанализировать состояние регистров процессора. Дальнейшие шаги рассматриваются для случая, когда обнаружено аппаратное прерывание;

процедура обработки прерывания должна идентифицировать источник прерывания - определить устройство, его вызвавшее. В случае разделяемого использования несколькими устройствами данного номера запроса (следовательно, и вектора) идентифицировать источник прерывания можно только последовательными обращениями к регистрам каждого из этих устройств. При этом следует учитывать возможность поступления запросов от нескольких устройств одновременно или в процессе обработки прерывания от одного из них;

процедура должна обслужить устройство-источник прерывания - выполнить «полезные» действия, связанные с событием, о котором и сигнализировало устройство. Это обслуживание должно обеспечить и снятие сигнала запроса прерывания от данного устройства. В случае разделяемых прерываний источников может быть и несколько, и все они требуют обслуживания;

если обработка прерывания занимает значительное время, в течение которого требуется реакция системы на более приоритетные запросы, то после критической секции в обработчик включают инструкцию SТI, устанавливающую флаг разрешения прерываний (IF) в процессоре. С этого момента возможнывложенные прерывания, прерывающие работу данного обработчика другой, более приоритетной процедурой;

процедура обработки прерывания должна послать контроллеру команду завершения обработки прерывания ЕОI (End Of Interrupt), по которой контроллер разрешит последующий прием сигнала с обслуженного входа и менее приоритетных. Это должно быть сделано после снятия сигнала прерывания от обслуженных устройств, иначе контроллер послеЕОI пошлет повторный запрос. Обработчик прерывания, для которого запрос поступил от ведомого контроллера, должен послатьЕОI как ведомому, так и ведущему контроллеру. Участок обработчика, начинающийся от подачи командыЕОI до завершения (инструкцииIRET), должен бытьнепрерываемым, то есть он являетсякритической секцией. Если обработчик разрешал вложенные прерывания, то перед подачей командыЕОI должна присутствовать инструкцияСLI,запрещающая прерывания;

завершается обработка прерывания инструкцией IRET, по которой процессор возвращается к выполнению прерванного потока инструкций, предварительно извлекая из стека содержимое регистра флагов. При этом аппаратные прерывания снова окажутся разрешенными.

Эта последовательность описана применительно к обычному контроллеру прерываний (PIC), в системах с APIC меняется способ доставки вектора прерывания от контроллера к процессору, а в прерываниях MSI меняется способ доставки сигнала от устройства к контроллеру APIC.