- •Прикладное программирование в информационно-навигационных системах

- •1.2 Направления повышения производительности (vliw, simd)

- •2.1 Цсп фирмы Texas Instruments. Семейства, области применения, особенности архитектуры.

- •2.2 Цифровой сигнальный контроллер tms320f28335

- •2.2.1 Основные параметры и характеристики

- •2.2.2 Краткое описание основных узлов и блоков

- •3.1 Вход/выходы общего назначения

- •3.2 Таймеры cpu

- •3.3 Внешний интерфейс

- •3.4 Прямой доступ к памяти

- •4.1 Модуль eQep квадратурного датчика (Encoder)

- •4.2 Модуль eCap захвата внешних событий (Capture)

- •4.3 Модуль ePwm широтно-импульсной модуляции

- •4.4 Модуль hrpwm широтно-импульсной модуляции с повышенным разрешением

- •4.5 Аналого-цифровой преобразователь adc

- •5.1 Модуль spi последовательного периферийного интерфейса

- •5.2 Модуль i2c межмикросхемного последовательного интерфейса

- •5.3 Модуль sci последовательного коммуникационного интерфейса

- •5.4 Модуль McBsp многоканального буферированного последовательного порта

- •5.5 Модуль can интерфейса

- •6.1.Интегрированная среда разработки и отладки программного обеспечения – общие понятия

- •6.2.Code Composer Studio ide (ccs): состав, общая характеристика

- •6.3 Настройка (Target and Host Setup), интерфейс пользователя

- •7.1 Конфигурация проекта

- •7.2 Текстовый редактор

- •7.3 Инструменты для создания программы

- •7.4 Построение проекта в ccs

- •7.5 Базовое программное обеспечение

- •8.1 Конфигурирование среды для отладки

- •8.2 Основные инструменты отладки

- •8.3 Отладка в реальном времени

- •8.4 Опции Reset

- •9.1 Анализ и оптимизация программы

- •9.2 Оптимизация прикладной программы

- •10.2 Примеры программ

- •10.3 Порядок внедрения заголовочных файлов и примеров программ

- •10.4 Использование matlab и LabView для подготовки и тестирования программ.

- •10.5 Аппаратная платформа для выполнения лабораторных работ tms320c2000 dsc Experimenter Kit. Назначение, устройство, особенности работы»

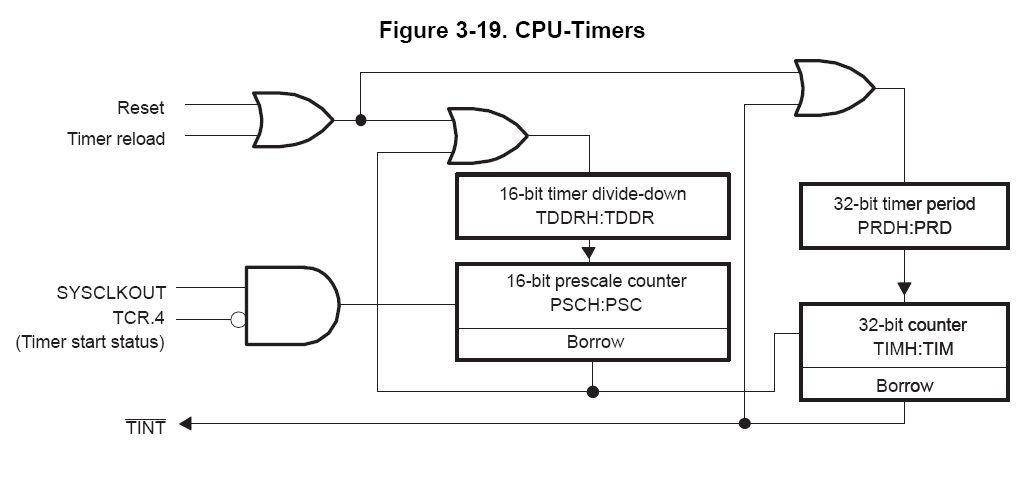

3.2 Таймеры cpu

3.2.1 CPUобслуживают три таймера:Timer0,Timer1,Timer2. Схема таймера приведена на рис 3.2. Таймеры 32-разрядные с предустановкой периода, имеют на входе 16-разрядный делитель для программирования частоты счетных импульсов. Период таймера задается в регистре PRD:PRDH. Значение периода перегружается в счетчик, состояние которого отображается регистромTIM:TIMH. Содержимое счетчика декриментируется импульсами с частотой тактовых импульсов процессора, поделенной на число, на 1 большее записанного в регистреTDDR. СодержимоеTDDRпереписывается в счетчикPSCи декриментируется тактовыми импульсами процессораSYSCLKOUT. При достижении нуля вырабатывается импульс, подаваемый на вход счетчика таймера. При достижении нуля в счетчике таймера вырабатывается прерывание, а в счетчик таймера автоматически загружается установленное 32-разрядное значение периода.

Рис.3.2. Блок-схема таймера CPU

3.2.2 Таймеры подключены к следующим входам прерывания CPU:

|

Таймер |

Вход прерывания |

Примечания |

|

Timer 0 |

Через блок PIE |

Общего назначения |

|

Timer 1 |

INT13 |

Общего назначения |

|

Timer 2 |

INT14 |

Резервирован для ОСРВ, если она не используется – общего назначения |

3.3 Внешний интерфейс

3.3.1 Описание функционирования

Внешняя память размечена на карте памяти в трех фиксированных зонах. Каждой зоне соответствует свой чип-селект сигнал, который переключается когда идет обращение к данной зоне. Для работы с внешней памятью предварительно должны быть конфигурированы выводы GPIO.

Каждая из трех зон может быть запрограммирована на индивидуальные число тактов ожидания, установки строб-сигнала, время удержания информации, причем для записи и чтения эти времена могут быть установлены различными. Перечисленные параметры доступа конфигурируются в соответствующих регистрах XTIMINGx. За базу при формировании временных интервалов принимается сигналXTIMCLK, частота которого одинакова для всех зон и может быть равна или в два раза ниже частоты тактовых импульсов контроллераSYSCLKOUT. По умолчаниюXTIMCLKвыключен, для включения необходимо записать 1 в битXINTFENCLKрегистраPCLKCR3.

Каждая зона может быть отконфигурирована для использования с 16- или 32-разрядной шириной шины данных.

Зона 0 – маленькая, содержит 8К адресов, зоны 1 и 2 содержат по 1М адресов каждая. Для обращения к внешней памяти в зоне 1 контроллер вырабатывает адреса от 0x00000 до 0x00FFFодновременно с чип-селектомXZCS0, для обращения к внешней памяти в зонах 6 и 7 - адреса 0x00000 до 0xFFFFFодновременно с чип-селектамиXZCS6,XZCS7, соответственно.

Все зоны имеют возможность прямого доступа к памяти, позволяя пересылку информации в или из зоны без отвлечения процессора от решения других задач.

3.3.2 Конфигурирование интерфейса внешней памяти

Перед изменением конфигурации интерфейса внешней памяти все обмены с ней должны быть завершены и буфер очищен.

Выбор частоты XTIMCLKосуществляется записью 1 в битXTIMCLKрегистраXINTFCNF2. По умолчанию частотаXTIMCLKустанавливается в два раза ниже частотыSYSCLKOUT.

Обращение к внешней памяти начинается по переднему фронту выходных тактов внешней памяти XCLKOUT, частота которых по умолчанию устанавливается в два раза ниже частотыXTIMCLK, при записи 1 в битCLKMODEрегистраXINTFCNF2 частоты уравниваются.

Для снижения шума выдача XCLKOUTможет быть отключена записью 1 в битCLKOFFрегистраXINTCNF2.

Процесс обращения к любому адресу в INTFзоне может быть разбит на три части: начало (lead), рабочая часть (active) и хвост (trail). Число тактовXTIMCLKдля каждой части обращения может быть сконфигурировано в соответствующей зоне регистраXTIMING, причем независимо для чтения и записи.