- •Цифровые сигнальные процессоры Архитектура, особенности организации вычислений

- •Отличительные особенности ЦСП: Архитектура шин

- •Обобщенная схема цифрового сигнального процессора

- •Шина программ

- •Типовые алгоритмы DSP

- •Цифровой сигнальный контроллер

- •Отличительные особенности ЦСП: Архитектура шин

- •Цифровые сигнальные процессоры

- •Texas Instruments DSP/DSC

- •Семейство TMS320 Texas Instruments

- •Цифровой сигнальный контроллер TMS320F28335

- •2.2.1 Основные параметры и характеристики

- •Устройство тактирования и управления системой, содержащее встроенную электронику генератора, систему ФАПЧ с поддержкой

- •Карта памяти

- •Особенности организации регистрового пространства периферийных устройств:

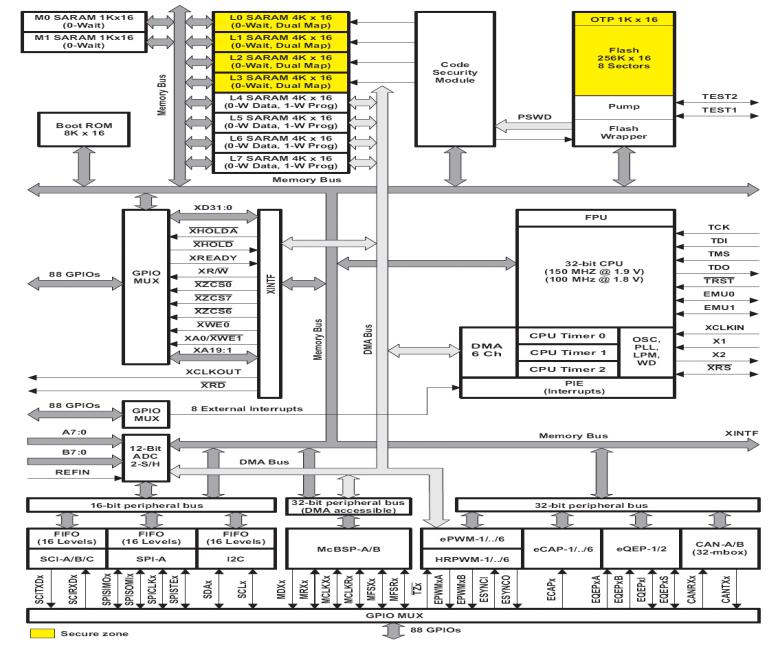

Цифровой сигнальный контроллер TMS320F28335

26

2.2.1 Основные параметры и характеристики

Высококачественная КМОП технология:

-частота до 150 МГц;

-напряжения питания: ядра 1,9/1,8 В; периферии 3,3 В.

32-разрядное центральное процессорное устройство (CPU):

-сопроцессор (FPU) с плавающей точкой (IEEE-754 одиночной точности);

-двойной аппаратный умножитель (MAC)16х16 с возможностью выполнения 32х32;

-Гарвардская архитектура шин;

-быстрая реакция на прерывания;

-унифицированная для программирования модель памяти;

-эффективная программируемость на С/С++ и Ассемблере.

6-каналььный контроллер прямого доступа к памяти(DMA).

16- или 32-разрядный интерфейс с внешней памятью (до 2Мх16 адресов).

Встроенная память:

-34Кх16 оперативная (SARAM);

-256Кх16 постоянной (Flash);

-1Кх16 постоянной (OTP ROM).

-ПЗУ загрузчика 8Кх16 с режимами загрузки через различные

интерфейсы и стандартными математическими таблицами. |

27 |

|

Устройство тактирования и управления системой, содержащее встроенную электронику генератора, систему ФАПЧ с поддержкой динамического изменения отношения частот, модуль сторожевого таймера.

128-разрядный кодовый замок, защищающий встроенную память. Три 32-разрядных таймера CPU

Расширенные средства управления исполнительными устройствами:

-18 выходов сигналов с ШИМ (PWM), из которых 6 выходов с ШИМ высокого разрешения до 150 пс (HRPWM);

-6 входов захвата внешних событий (Event Capture);

-8 32-разрядных таймеров;

-2 интерфейса энкодеров.

Последовательные порты:

-два модуля интерфейса CAN;

-три модуля интерфейса SCI (UART);

-два модуля интерфейса McBSP;

-SPI модуль;

-модуль I2С;

16-канальный 12-разрядный АЦП с временем преобразования 80 нс

-мультиплексор 2х8 каналов;

-два устройства выборки/хранения;

-возможность одновременного преобразования двух сигналов;

- внутренний или внешний источник опорного напряжения. |

28 |

29

30

31

32

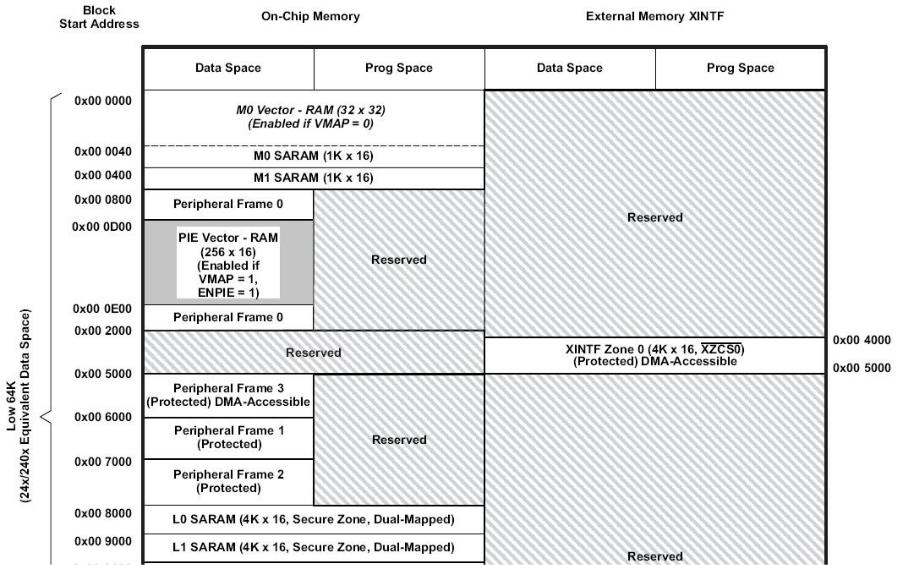

Карта памяти

Распределение адресного пространства

процессора зафиксировано в его карте памяти

Особенности карты памяти TMS320F28335: -Размер блоков фиксирован и не может быть изменен пользователем;

-Периферийные фрэймы Per. Frame 0, 1, 2, 3 предназначены только для данных и недоступны для пользовательских программ

-В области адресов 0х38 0080 – 0х38 008F хранится процедура калибровки АЦП – пользователем не программируется

-Если в проекте CAN интерфейс не используется, то его область оперативной памяти может быть использована как память общего назначения.

33

34

35

36

37