- •Цифровые сигнальные процессоры Архитектура, особенности организации вычислений

- •Отличительные особенности ЦСП: Архитектура шин

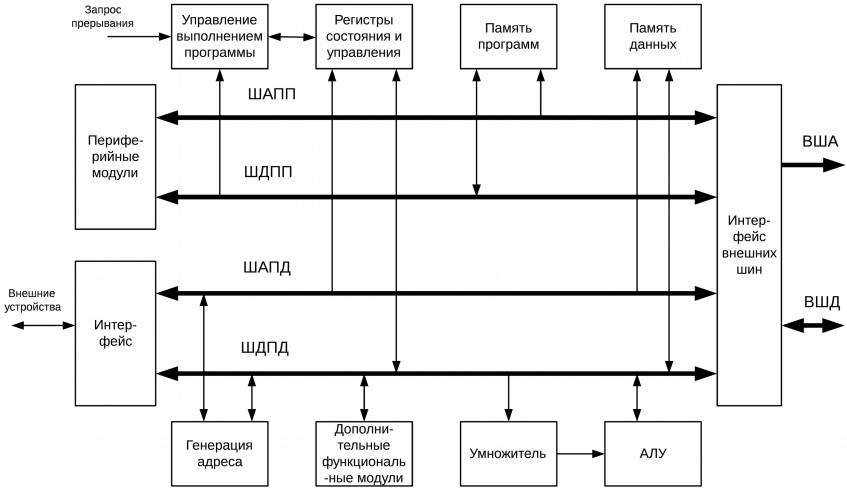

- •Обобщенная схема цифрового сигнального процессора

- •Шина программ

- •Типовые алгоритмы DSP

- •Цифровой сигнальный контроллер

- •Отличительные особенности ЦСП: Архитектура шин

- •Цифровые сигнальные процессоры

- •Texas Instruments DSP/DSC

- •Семейство TMS320 Texas Instruments

- •Цифровой сигнальный контроллер TMS320F28335

- •2.2.1 Основные параметры и характеристики

- •Устройство тактирования и управления системой, содержащее встроенную электронику генератора, систему ФАПЧ с поддержкой

- •Карта памяти

- •Особенности организации регистрового пространства периферийных устройств:

Цифровые сигнальные процессоры Архитектура, особенности организации вычислений

1

Отличительные особенности ЦСП: Архитектура шин

Конвейерное выполнение команд Аппаратная реализация программных функций Специфические команды ЦОС

Направления повышения производительности:

-увеличение количества одновременно выполняемых операций

-увеличение количества одновременно обрабатываемых данных

-увеличение количества одновременно выполняемых команд

2

3

Обобщенная схема цифрового сигнального процессора

4

|

|

|

|

|

|

|

|

Конвейер |

|

|

|||

A |

F1 |

F2 |

D |

D |

R1 |

R2 |

X |

W |

|

|

8-уровневый |

||

1 |

2 |

|

|

||||||||||

B |

|

F1 |

F2 |

D |

D |

R1 |

R2 |

X |

W |

|

конвейер |

||

|

1 |

2 |

|

||||||||||

C |

|

|

F |

F |

D |

D |

R |

R |

X |

W |

|

|

|

|

|

1 |

2 |

1 |

2 |

1 |

2 |

|

|

|

|||

D |

|

|

|

F1 |

F2 |

D |

D |

R1 |

R2 |

X |

W |

|

E & G доступ к |

|

|

|

1 |

2 |

|

||||||||

E |

|

|

|

|

F1 |

F2 |

D |

D |

R1 |

R2 |

X |

W |

тому же адресу |

|

|

|

|

|

|

|

1 |

2 |

|

|

|

|

|

F |

|

|

|

|

|

F1 F2 |

D D |

R1 |

R2 X W |

||||

|

|

|

|

|

|

|

|

1 |

2 |

|

|

|

|

G |

|

|

|

|

|

|

F1 |

F2 |

D D |

R1 |

|

R2 X W |

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

|

|

H |

|

|

|

|

|

|

|

F1 F2 |

D D |

|

R1 R2 X W |

||

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

|

F1: Адрес инструкции |

Защита конвейера |

|

F2: Чтение инструкции |

Порядок результатов такой же как |

|

D1: Декодирование инструкции |

||

D2: Вычисление адресов |

это записано в программе |

|

операндов |

Программисту не нужно заботиться о |

|

R1: Адрес операнда |

||

R2: Получение операнда |

конвейере |

5 |

X: Вычисление в ЦП |

|

|

W: Сохранение содержимого |

|

|

Шина программ |

|

|

|

|

|

|

|

|

Ядро ЦСП |

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Шина данных |

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

16/3 |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

XT (32) or T/TL |

|

|

|

|

8/16/32 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

2 |

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

Умножитель |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

32 x 32 или |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Сдвиг R/L (0- |

|

|

|

|

|

два 16 x 16 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

16) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

P (32) or PH/PL |

|

|

|

|

|

|

|

|

8/16 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

32 |

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

32 |

|

|

|

|

|

Сдвиг R/L (0-16) |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32

|

|

|

|

АЛУ (32) |

|

|

|

|

|

|||||

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АКК (32) |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

AH (16) |

|

AL (16) |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AH.MSB |

|

AH.LSB |

|

AL.MSB |

|

|

AL.LSB |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сдвиг R/L (0- |

|

||||||||||

Шина |

|

|

16) |

|

|

|

|

6 |

||||||

|

|

|||||||||||||

|

|

|

|

|

32 |

|

|

|

|

|

|

|

||

данных

Типовые алгоритмы DSP

Сумма произведений – основной элемент большинства DSP алгоритмов:

Алгоритмы

• Фильтр с конечной y(n) импульсной характеристикой

M

ak x(n k)

k 0

|

Фильтр с бесконечной |

|

|

M |

|

k |

|

N |

|

|

|

|

|

• |

|

|

a |

k |

|

|

|

||||||

|

y(n) |

|

|

x(n k) |

b y(n k) |

|

|||||||

импульсной характеристикой |

|

k 0 |

|

|

|

k 1 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y(n) |

N |

x(k)h(n k) |

|

|

|

|

|

||||

• Свертка |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

k 0 |

|

|

|

|

|

|

|

|

||

|

|

|

|||||||||||

|

Дискретное преобразование |

X (k) x(n) exp[ j(2 / N )nk] |

|

||||||||||

• |

|

|

|

N 1 |

|

|

|

|

|

|

|||

Фурье |

|

|

n 0 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||

• Дискретное косинусное |

|

|

N 1 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||||

F u c(u). f (x).cos |

|

u 2x 1 |

|||||||||||

2N |

|||||||||||||

преобразование |

|

|

x 0 |

|

|

|

|

|

|

||||

Цифровой сигнальный контроллер

|

|

|

Шина программ |

Менеджер |

||

|

|

|

|

|

|

Событий А |

|

|

|

|

|

Загр. |

Менеджер |

|

|

Секторна |

|

Событий B |

||

|

|

я |

|

ОЗУ |

ПЗУ |

12 битный |

A(18-0) |

22 |

Flash |

|

|

АЦП |

|

|

|

Сторожевой |

||||

|

|

|

|

|

|

|

|

32 |

|

|

|

|

таймер |

|

|

|

|

|

|

|

D(15-0) |

32 |

|

|

|

|

|

|

32 |

|

|

R-M-W |

PIE |

McBSP |

|

|

|

менеджер |

|

||

|

|

|

|

|

||

|

|

32-бит. |

32x32 бит |

АЛУ |

|

|

|

|

прерыв. |

CAN2.0B |

|||

|

|

Регистры |

Умножитель атомар. |

|||

|

|

|

|

|||

|

|

|

|

функций |

|

SCI-A |

|

|

|

|

|

3 |

|

|

|

|

|

|

32 битных |

SCI-B |

JTAG |

|

|

Шина регистров |

Таймера |

||

|

ЦП |

|

|

|||

|

|

|

|

|

||

реального |

|

|

|

SPI |

||

времени |

|

|

|

|

||

Шина данных

|

|

8 |

|

GPIO |

|

|

|

|

|

|

|

Отличительные особенности ЦСП: Архитектура шин

Конвейерное выполнение команд Аппаратная реализация программных функций Специфические команды ЦОС

Направления повышения производительности:

-увеличение количества одновременно выполняемых операций

-увеличение количества одновременно обрабатываемых данных

-увеличение количества одновременно выполняемых команд

9

Цифровые сигнальные процессоры

фирмы Texas Instruments

10