- •Эвм и вычислительные системы».

- •Часть I.

- •Лекция №1 общие сведения о микропроцессорах и микропроцессорных системах.

- •Предисловие

- •1.1 . Основные определения и классификация микропроцессорных систем.

- •1.2. Однокристальные мп.

- •1.2.1 Краткий исторический обзор развития.

- •Лекция №2 обзор микропроцессоров фирм клонмейкеров. Современный уровень развития однокристальных микропроцессоров.

- •2.1. Микропроцессоры-клоны.

- •2.2. Современные универсальные однокристальные микропроцессоры.

- •Процессоры Pentium II.

- •2.2.1. Процессоры фирмы amd

- •2.2.2.ПроцессорыфирмыCyrix.

- •2.2.3. Сравнительный анализ мп различных семейств.

- •2.2.4. Перспективы развития.

- •2.3. Программируемые микроконтроллеры.

- •Лекция №3 обзор микропроцессоров с микропрограммным управлением и микропроцессоров с сокращенным набором команд.

- •3.1. Мп с микропрограммным управлением.

- •3.2. Мп с сокращенным набором команд.

- •3.2.1. Risc-процессоры: предпосылки создания.

- •3.2.2. Принципы risc

- •3.2.3. Особенности risc-процессоров.

- •3.2.4. Представители группы risc-процессоров.

- •3.2.5. Цифровые процессоры обработки сигналов.

- •Лекция №4 представление информации в мпс.

- •4.1. Способы кодирования информации в мпс.

- •4.2 Двоичный формат.

- •4.3. Двоично-десятичная система кодирования.

- •4.4. Шестнадцатиричная система счисления.

- •4.4. Формат с плавающей точкой.

- •4.5. Кодирование команд.

- •Лекция №5 архитектура мп и мпс.

- •5.1. Понятие организации и архитектуры мп и мпс.

- •5.2 Обобщенная функциональная схема мп.

- •5.2.1 Устройство управления на основе аппаратной реализации.

- •5.2.2. Программируемая логическая матрица.

- •Лекция №6 архитектура мп и мпс.(продолжение)

- •6.1. Функциональная схема однокристального мп.

- •6.2 Структура адресного пространства мпс.

- •6.3 Взгляд программиста на адресное пространство.

- •6.4 Понятие стека.

- •Лекция №7 способы адресации

- •7.1 Основные определения.

- •7.2 Однокомпонентные способы адресации.

- •7.2.1 Прямой способ адресации.

- •7.2.3 Способы адресации с автомодификацией.

- •7.3 Многокомпонентные способы адресации.

- •Лекция №8 основы проограммирования на языке ассемблера для мп i8086.

- •8.1. Формат команд на языке встроенного ассемблера.

- •8.2. Архитектура мп i8086.

- •8.2.1 Сегментация памяти мп i8086.

- •8.2.2 Структура мп i8086.

- •8.2.3 Устройство шинного интерфейса.

- •8.2.4 Операционное устройство(оу).

- •8.3 Основные команды языка Ассемблер для мп i8086.

- •8.3.1 Команды пересылки данных.

- •Лекция №9 основы проограммирования на языке ассемблера для мп i8086. (продолжение).

- •9.1. Арифметические команды.

- •9.2. Логические команды.

- •9.3. Команды передачи управления.

- •9.4. Команды управления мп.

- •Лекция №10 запоминающие устройства.

- •10.1 Основные характеристики полупроводниковых запоминающих устройств.

- •10.2 Способы организации бис зу.

- •10.3 Классификация полупроводниковых зу.

- •10.3.1. Статические озу (Static Random Access Memory).

- •10.3.2. Озу динамического типа (Dynamic Random Access Memory dram).

- •10.3.4. Кмоп - озу.

- •Лекция №11 запоминающие устройства. (продолжение)

- •11.1. Постоянные зу. (Read Only Memory - rom).

- •11.2. Flash-память.

- •11.3. Корпуса модулей зу.

- •11.4. Наращивание объема и разрядности памяти, построенной на полупроводниковых зу.

- •Лекция № 12 организация магистралей мпс.

- •12.1 Типы магистралей мпс.

- •12.2 Циклы обращения к магистрали.

- •12.3 Примеры архитектур системных магистралей современных мпс.

- •Лекция №13 методы расширения адресного пространства мпс.

- •13.1 Предварительные замечания.

- •13.2 Метод окна.

- •13.3 Метод базовых регистров.

- •13.4 Метод банков.

- •13.5 Метод виртуальной памяти.

- •Лекция №14 система прерываний.

- •14.1 Понятие системы прерываний, классификация систем прерываний.

- •14.2. Организация радиальной системы прерываний.

- •14.3. Расширение радиальной системы прерываний методом поллинга.

- •14.4. Организация векторной системы прерываний.

- •Лекция №15 организация связи мпс с переферийными устройствами.

- •15.1. Классификация способов обмена информацией в мпс.

- •Прямой ввод/ вывод

- •15.3 Условный ввод-вывод.

- •15.4. Режим прямого доступа к памяти.

- •Лекция №16 интерфейсы мпс.

- •16.1. Принципы организации и классификация интерфейсов.

- •16.2. Элементная база интерфейсов.

- •16.3. Средства параллельного ввода/вывода.

- •Лекция №17 расширитель интерфейса для ibm-совместимых пк. Программируемый интервальный таймер.

- •17.1. Расширитель интерфейса рс на основе ппа кр580вв55.

- •17.2 Программируемый интервальный таймер.

- •17.3. Модуль преобразования цифрового кода в шим-сигнал на базе пит.

- •Лекция №18 интерфейсы последовательной связи.

- •18.1. Общая характеристика последовательной связи.

- •18.2. Асинхронные последовательные интерфейсы.

- •18.3. Бис для организации последовательного интерфейса.

- •18.4. Модем.

- •18.5. Стандарты физической связи. Стандарт rs -232- c.

16.2. Элементная база интерфейсов.

Унификация малых интерфейсов периферийных устройств привела к созданию ряда стандартных адаптеров и контроллеров в виде периферийных БИС, применение которых позволяет в значительной степени освободить МП от управления операциями ВВ и выполнения вспомогательных процедур преобразования форматов данных, подсчета передаваемых байт (бит) и т.д.

К числу периферийных БИС относятся шинные формирователи К589АП16, буферные регистры К589ИР12, программируемые периферийные адаптеры К580ВВ55, программируемые связные адаптеры К580ВВ51, программируемый интервальный таймер К580ВИ53. С их помощью могут создаваться как программируемые , так и непрограммируемые интерфейсы. Функции непрограммируемых интерфейсов не изменяются в процессе работы МПС. Программируемые интерфейсы могут перестраиваться под управлением МП с выполнения одной функции на другую, благодаря чему обеспечивается более гибкая работа МПС.

Использование специализированных периферийных БИС позволяет не только упростить разработку программного обеспечения , но и облегчает проектирование аппаратуры . Заменяя большие объемы аппаратных средств, которые в противном случае пришлось бы разрабатывать на основе схем малой логики , они повышают компактность и надежность систем.

16.3. Средства параллельного ввода/вывода.

Параллельный В/В - один из наиболее простых и широко распространенных способов обмена информацией с ПУ, при котором практически не требуется никакого промежуточного преобразования данных.

Для построения портов, реализующих параллельный В/В информации, могут быть использованы различные БИС буферных регистров, шинных формирователей и программируемых приемопередатчиков. Рассмотрим более подробно схему программируемого периферийного адаптера (ППА) и интерфейсную плату для подключения к системной шине ПК, разработанную на его основе.

Программируемый периферийный адаптер.

Программируемый периферийный адаптер (ППА) КР580ВВ55 представляет собой однокристальное программируемое устройство параллельного ВВ информации произвольного формата. В состав осуществляемых им процедур входит параллельный обмен данными с квитированием или без него как в режиме программного управления, так и по прерываниям. При этом обеспечивается организация не только однонаправленного, но и двунаправленного ВВ. Определение и переопределение типа интерфейса выполняется программными методами с помощью процедур инициализации.

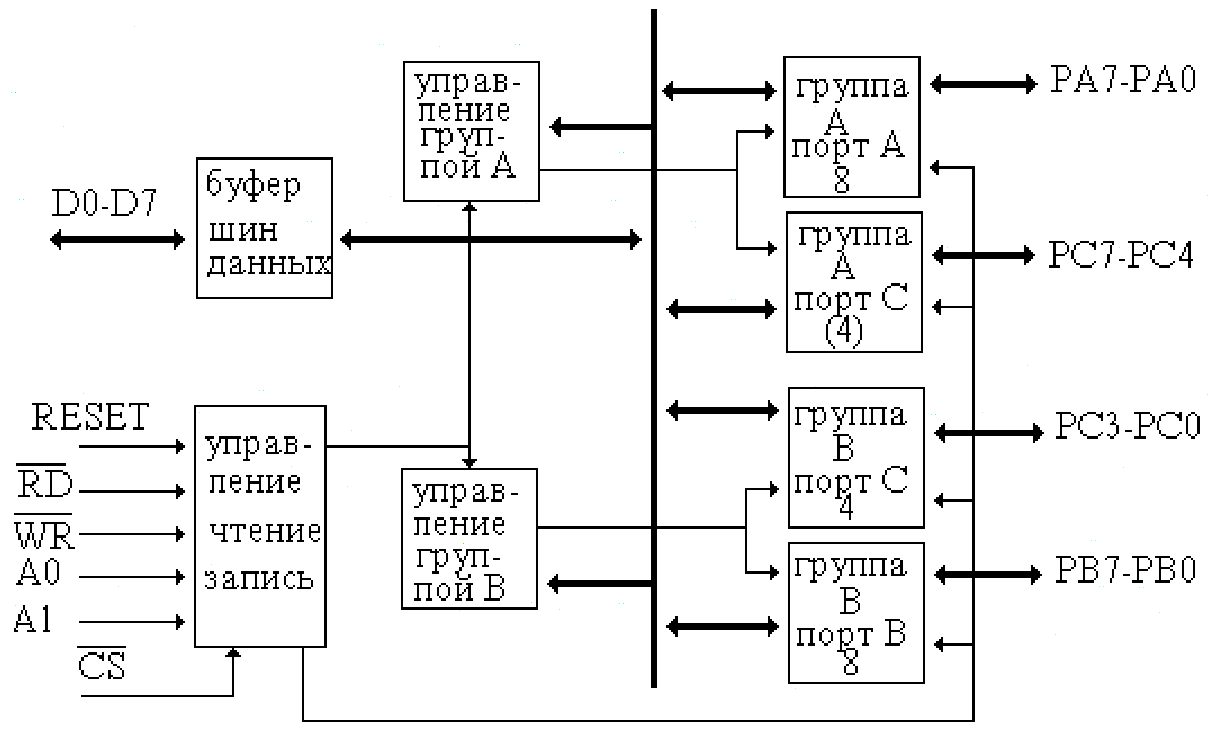

Структурная схема ППА показана на рис.16.6.

В состав ППА входят три двунаправленных 8-разрядных порта, разбитых на две группы, два устройства управления группами портов и интерфейсная логика для согласования с системной магистралью.

ППА поддерживает три режима работы портов:

- режим 0 - однонаправленный ВВ без квитирования (применим к любому из трех портов);

- режим 1 - однонаправленный ВВ с квитированием (применим к портам А и В);

- режим 2 - двунаправленный ВВ (допускается только для порта А).

Рис.16.6.

При работе портов А и В в режимах 1 и 2 часть линий порта С из соответствующей группы используется для управления обменом с внешними ПУ.

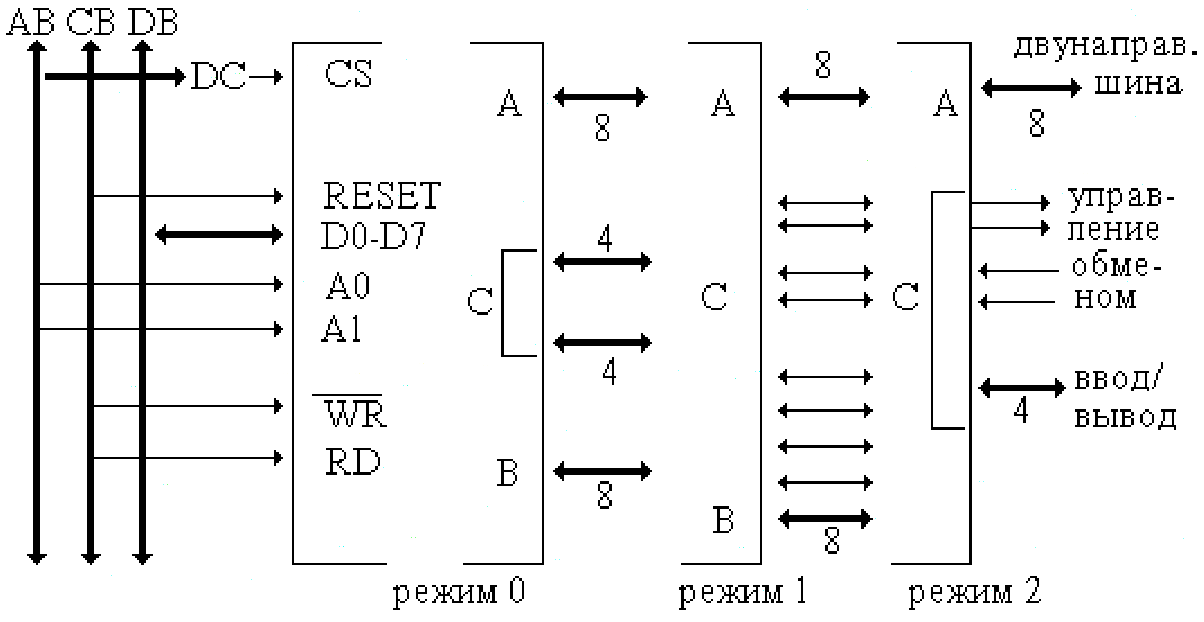

Подключение ППУ к системной магистрали показано на рис.16.7.

Рис.16.7.

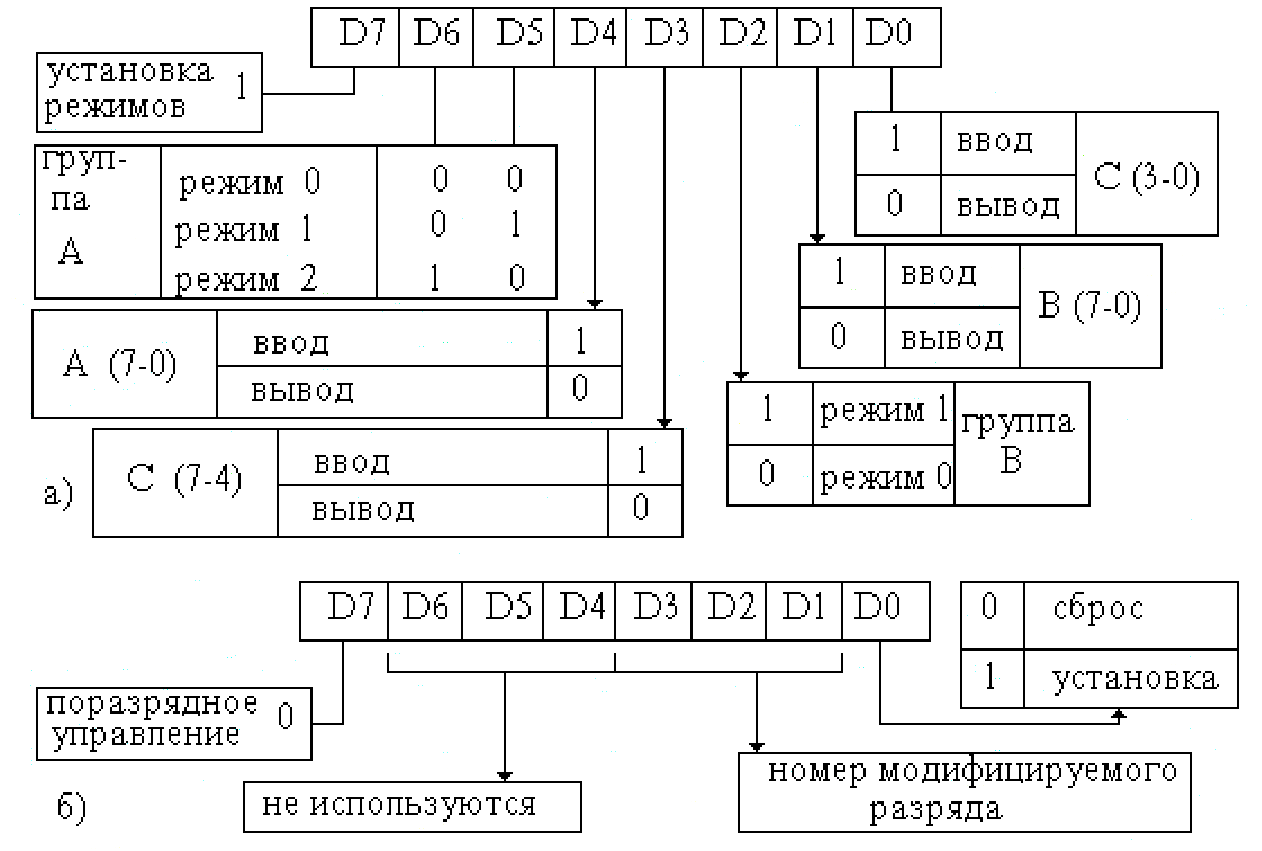

Режим работы каждого из каналов ППА программируется с помощью управляющего слова, формат которого представлен на рис.16.8.

Разряд D7 управляющего слова определяет либо установку режимов работы его каналов (D7=1), либо работу ППА в режиме сброса-установки отдельных разрядов канала С (D7=0).

Рис.16.8.

Код управляющего слова для установки ППА: А-вывод, В-ввод, С-вывод, режим-0, имеет вид: 10000010(2) = 82H.

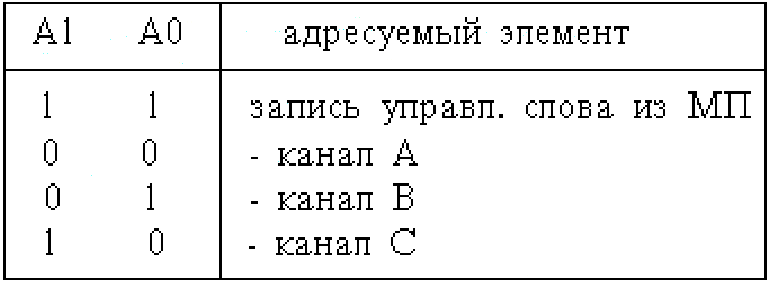

Вид операции, выполняемой БИС, задается сигналами управления RD, WR, RESET, CS совместно с адресными линиями А0, А1 (таблица 16.1).

Таблица 16.1