- •Эвм и вычислительные системы».

- •Часть I.

- •Лекция №1 общие сведения о микропроцессорах и микропроцессорных системах.

- •Предисловие

- •1.1 . Основные определения и классификация микропроцессорных систем.

- •1.2. Однокристальные мп.

- •1.2.1 Краткий исторический обзор развития.

- •Лекция №2 обзор микропроцессоров фирм клонмейкеров. Современный уровень развития однокристальных микропроцессоров.

- •2.1. Микропроцессоры-клоны.

- •2.2. Современные универсальные однокристальные микропроцессоры.

- •Процессоры Pentium II.

- •2.2.1. Процессоры фирмы amd

- •2.2.2.ПроцессорыфирмыCyrix.

- •2.2.3. Сравнительный анализ мп различных семейств.

- •2.2.4. Перспективы развития.

- •2.3. Программируемые микроконтроллеры.

- •Лекция №3 обзор микропроцессоров с микропрограммным управлением и микропроцессоров с сокращенным набором команд.

- •3.1. Мп с микропрограммным управлением.

- •3.2. Мп с сокращенным набором команд.

- •3.2.1. Risc-процессоры: предпосылки создания.

- •3.2.2. Принципы risc

- •3.2.3. Особенности risc-процессоров.

- •3.2.4. Представители группы risc-процессоров.

- •3.2.5. Цифровые процессоры обработки сигналов.

- •Лекция №4 представление информации в мпс.

- •4.1. Способы кодирования информации в мпс.

- •4.2 Двоичный формат.

- •4.3. Двоично-десятичная система кодирования.

- •4.4. Шестнадцатиричная система счисления.

- •4.4. Формат с плавающей точкой.

- •4.5. Кодирование команд.

- •Лекция №5 архитектура мп и мпс.

- •5.1. Понятие организации и архитектуры мп и мпс.

- •5.2 Обобщенная функциональная схема мп.

- •5.2.1 Устройство управления на основе аппаратной реализации.

- •5.2.2. Программируемая логическая матрица.

- •Лекция №6 архитектура мп и мпс.(продолжение)

- •6.1. Функциональная схема однокристального мп.

- •6.2 Структура адресного пространства мпс.

- •6.3 Взгляд программиста на адресное пространство.

- •6.4 Понятие стека.

- •Лекция №7 способы адресации

- •7.1 Основные определения.

- •7.2 Однокомпонентные способы адресации.

- •7.2.1 Прямой способ адресации.

- •7.2.3 Способы адресации с автомодификацией.

- •7.3 Многокомпонентные способы адресации.

- •Лекция №8 основы проограммирования на языке ассемблера для мп i8086.

- •8.1. Формат команд на языке встроенного ассемблера.

- •8.2. Архитектура мп i8086.

- •8.2.1 Сегментация памяти мп i8086.

- •8.2.2 Структура мп i8086.

- •8.2.3 Устройство шинного интерфейса.

- •8.2.4 Операционное устройство(оу).

- •8.3 Основные команды языка Ассемблер для мп i8086.

- •8.3.1 Команды пересылки данных.

- •Лекция №9 основы проограммирования на языке ассемблера для мп i8086. (продолжение).

- •9.1. Арифметические команды.

- •9.2. Логические команды.

- •9.3. Команды передачи управления.

- •9.4. Команды управления мп.

- •Лекция №10 запоминающие устройства.

- •10.1 Основные характеристики полупроводниковых запоминающих устройств.

- •10.2 Способы организации бис зу.

- •10.3 Классификация полупроводниковых зу.

- •10.3.1. Статические озу (Static Random Access Memory).

- •10.3.2. Озу динамического типа (Dynamic Random Access Memory dram).

- •10.3.4. Кмоп - озу.

- •Лекция №11 запоминающие устройства. (продолжение)

- •11.1. Постоянные зу. (Read Only Memory - rom).

- •11.2. Flash-память.

- •11.3. Корпуса модулей зу.

- •11.4. Наращивание объема и разрядности памяти, построенной на полупроводниковых зу.

- •Лекция № 12 организация магистралей мпс.

- •12.1 Типы магистралей мпс.

- •12.2 Циклы обращения к магистрали.

- •12.3 Примеры архитектур системных магистралей современных мпс.

- •Лекция №13 методы расширения адресного пространства мпс.

- •13.1 Предварительные замечания.

- •13.2 Метод окна.

- •13.3 Метод базовых регистров.

- •13.4 Метод банков.

- •13.5 Метод виртуальной памяти.

- •Лекция №14 система прерываний.

- •14.1 Понятие системы прерываний, классификация систем прерываний.

- •14.2. Организация радиальной системы прерываний.

- •14.3. Расширение радиальной системы прерываний методом поллинга.

- •14.4. Организация векторной системы прерываний.

- •Лекция №15 организация связи мпс с переферийными устройствами.

- •15.1. Классификация способов обмена информацией в мпс.

- •Прямой ввод/ вывод

- •15.3 Условный ввод-вывод.

- •15.4. Режим прямого доступа к памяти.

- •Лекция №16 интерфейсы мпс.

- •16.1. Принципы организации и классификация интерфейсов.

- •16.2. Элементная база интерфейсов.

- •16.3. Средства параллельного ввода/вывода.

- •Лекция №17 расширитель интерфейса для ibm-совместимых пк. Программируемый интервальный таймер.

- •17.1. Расширитель интерфейса рс на основе ппа кр580вв55.

- •17.2 Программируемый интервальный таймер.

- •17.3. Модуль преобразования цифрового кода в шим-сигнал на базе пит.

- •Лекция №18 интерфейсы последовательной связи.

- •18.1. Общая характеристика последовательной связи.

- •18.2. Асинхронные последовательные интерфейсы.

- •18.3. Бис для организации последовательного интерфейса.

- •18.4. Модем.

- •18.5. Стандарты физической связи. Стандарт rs -232- c.

12.2 Циклы обращения к магистрали.

Процессы передачи информации по магистрали называются циклами обращения к магистрали. За один цикл передается один байт или одно машинное слово. Существуют несколько типовых циклов обращения к магистрали:

- чтение памяти и запись в память;

- при изолированном вводе/выводе - чтение порта ввода и запись в порт вывода;

- чтение памяти программ (для архитектуры Гарвардского типа).

В зависимости от числа типовых циклов обращения к магистрали шина управления СВ должна содержать соответствующее число линий для синхронизации и управления процессами обмена. К типовому набору сигналов управления относятся:

СLС - сигнал синхронизации;

![]() - сигнал чтения;

- сигнал чтения;

![]() - сигнал записи;

- сигнал записи;

![]() /IО

- выбор пространства памяти или ВВ;

/IО

- выбор пространства памяти или ВВ;

СОD - выбор памяти программ.

Для отражения состояния шин во времени (передача информации, неопределенное состояние, неустановившееся состояние, высокоимпедансное состояние -z), а также последовательности работы различных устройств МПС используют временные диаграммы изменения сигналов.

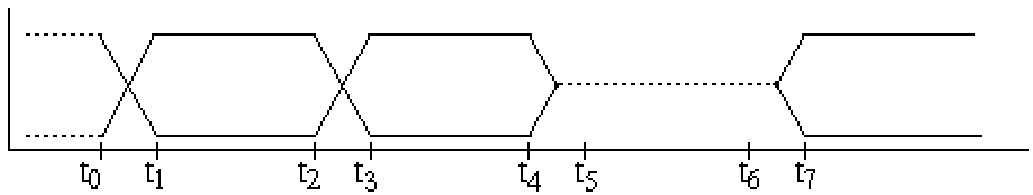

Пример диаграммы, отражающей различные состояния шины , приведен на рис. 12.5.

Рис.12.5

Интервалу времени t<t0 соответствует неопределенное состоя-ние шины; интервалам [t0 ,t1 ], [t2 ,t3 ], [t4 ,t5 ], [t6 ,t7 ] -неустановившееся состояние линий (процессы переключения); интервалам [t1 ,t2 ],[t3 ,t4 ],t>t7 – соответствует состояние, при котором информация на линиях установлена; на интервале [t5,t6] - линии шины находятся в высоко-импедансном состоянии.

Причинно-следственные связи между сигналами на временных диаграммах отражают при помощи специальных стрелок.

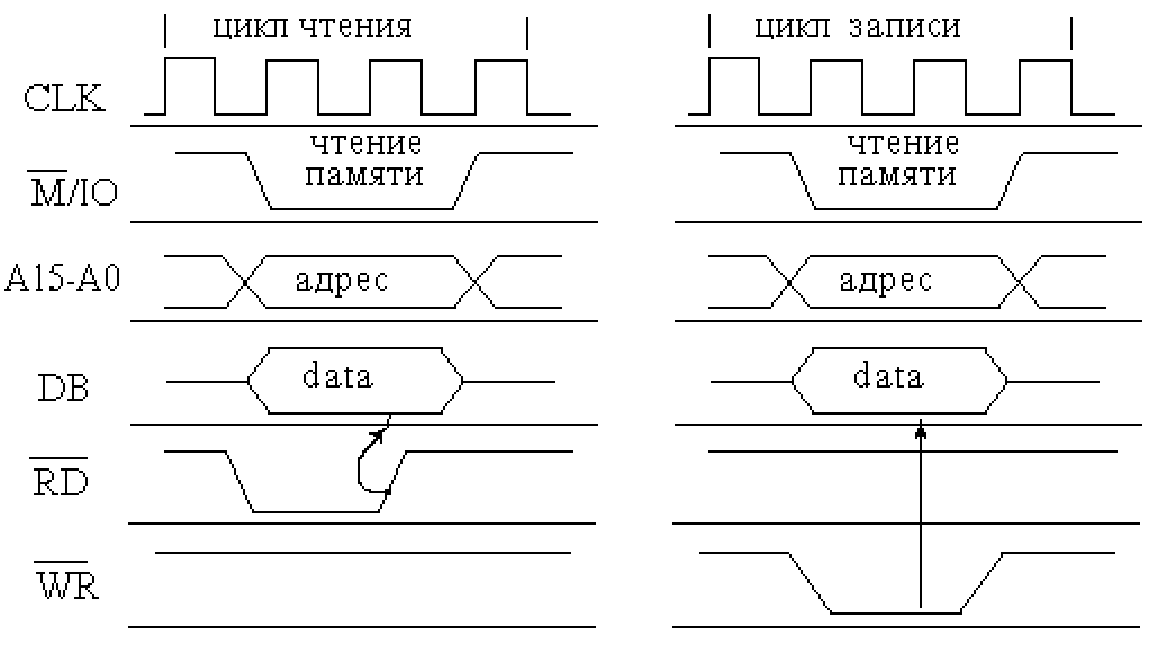

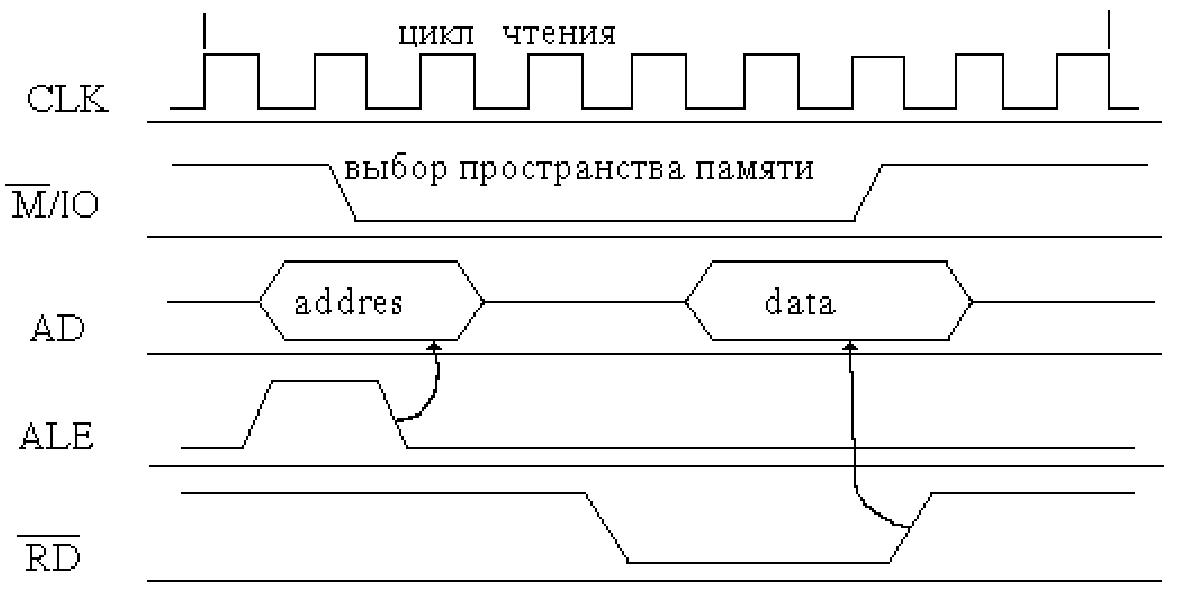

Примеры временных диаграмм передачи данных по трехшинной магистрали приведены на рис.12.6. и по двухшинной магистрали - на рис.12.7.

Рис 12.6.

Рис.12.7.

Из представленных временных диаграмм следует, что периферийные модули, к которым происходит обращение МП (память) успевают отреагировать на стробы RD и WR. В этом случае говорят о синхронном режиме работы магистрали, который обеспечивает безусловную передачу данных со скоростью, определяемой МП.

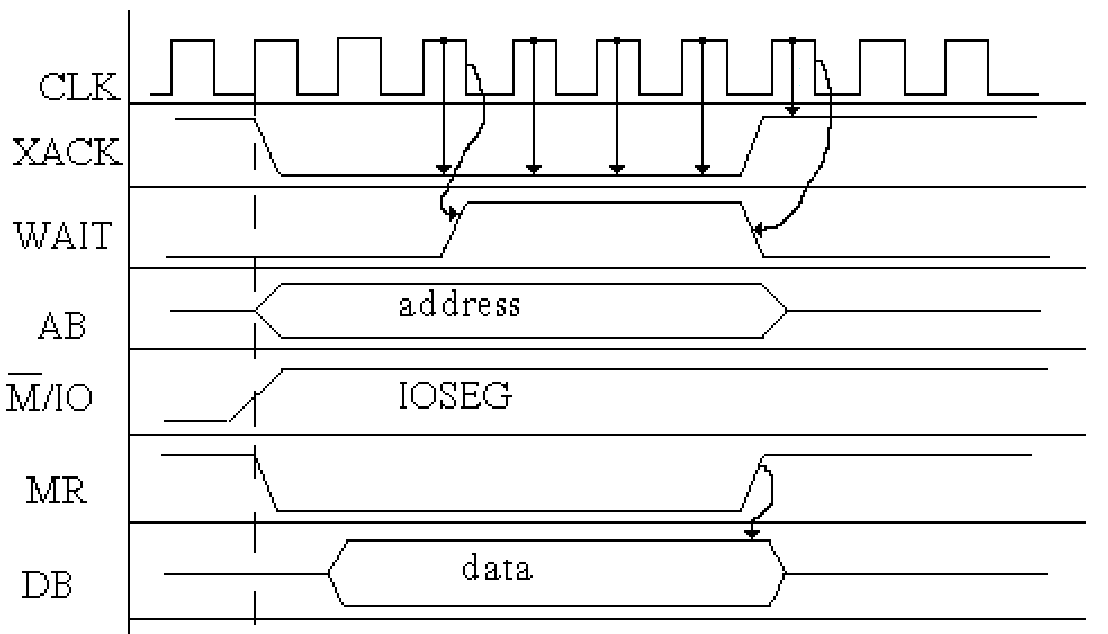

Для организации надежного обмена данными с медленными периферийными устройствами в состав шины управления вводят специальную линию "подтверждения обмена" ХАСК. При этом МП, в каждом цикле обмена перед снятием активных уровней сигналов RD или WR, проверяет линию ХАСК, контролируя установку внешним устройством Exchange Acknowledge сигнала подтверждения обмена. При наличии подтверждения обмена МП начинает выполнение другой команды, в противном случае он переходит в состояние ожидания, в котором периодически (с периодом следования импульсов СLК) тестирует линию ХАСК до момента появления на ней сигнала подтверждения обмена. Организованный таким образом обмен называется асинхронным режимом работы системной магистрали.

Диаграмма сигналов, соответствующая асинхронному режиму работы системной магистрали приведена на рис. 12.8.

12.3 Примеры архитектур системных магистралей современных мпс.

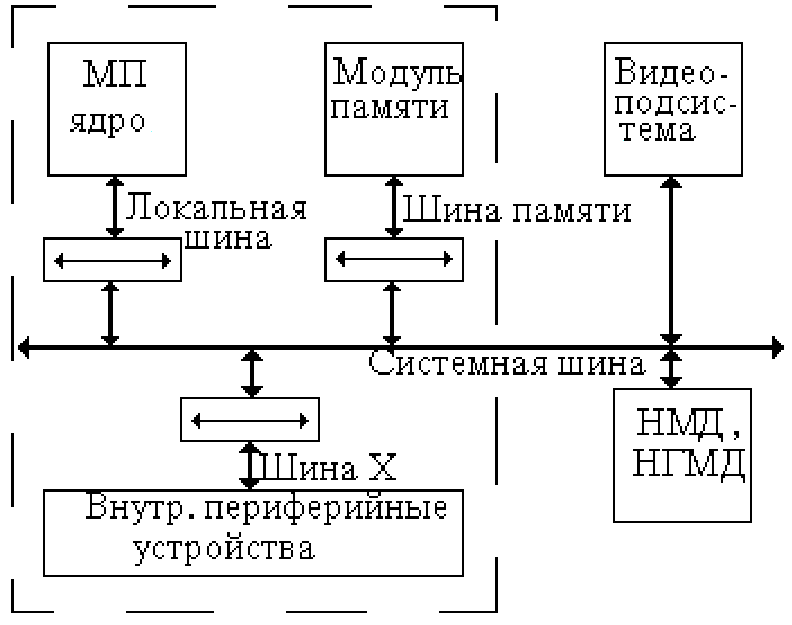

Рассмотренные архитектуры системных магистралей являются достаточно абстрактными. Архитектуры реальных систем включают, как правило, целый набор магистралей (шин). В качестве примера рассмотрим архитектуру ПК, которая включает:

- локальную шину (L), непосредственно связанную с микропро-цессором ;

- шину памяти (М), к которой подключаются микросхемы основной памяти;

- системную шину, к которой подключаются внешние периферийные устройства, такие как терминал, накопители НМД, НГМД;

Рис.12.8.

- шину внутренних программируемых устройств (Х), к которой подключаются внутренние программируемые микросхемы, такие как контроллер клавиатуры, таймеры и т. д.;

В этом случае архитектура МПС может быть представлена в виде, изображенному на рис.12.9.:

Рис.12.9.

Рассмотренная выше шинная организация МПС не является оптимальной с точки зрения обеспечения высокой производительности МПС. Дело в том, что с ростом тактовой частоты микропроцессора процедура обращения к памяти становится самым “узким” местом системы, сдерживающим рост ее производительности. Из рассмотренной структурной схемы МПС следует, что когда МП читает, например, из памяти, воздействие (адрес и команда) с локальной шины попадает на системную шину, и только затем на шину памяти. После этого данные из памяти опять-таки попадают на системную шину, а с нее - на локальную. Приведенная архитектура была характерна для ПК типа IBM PC/XT.

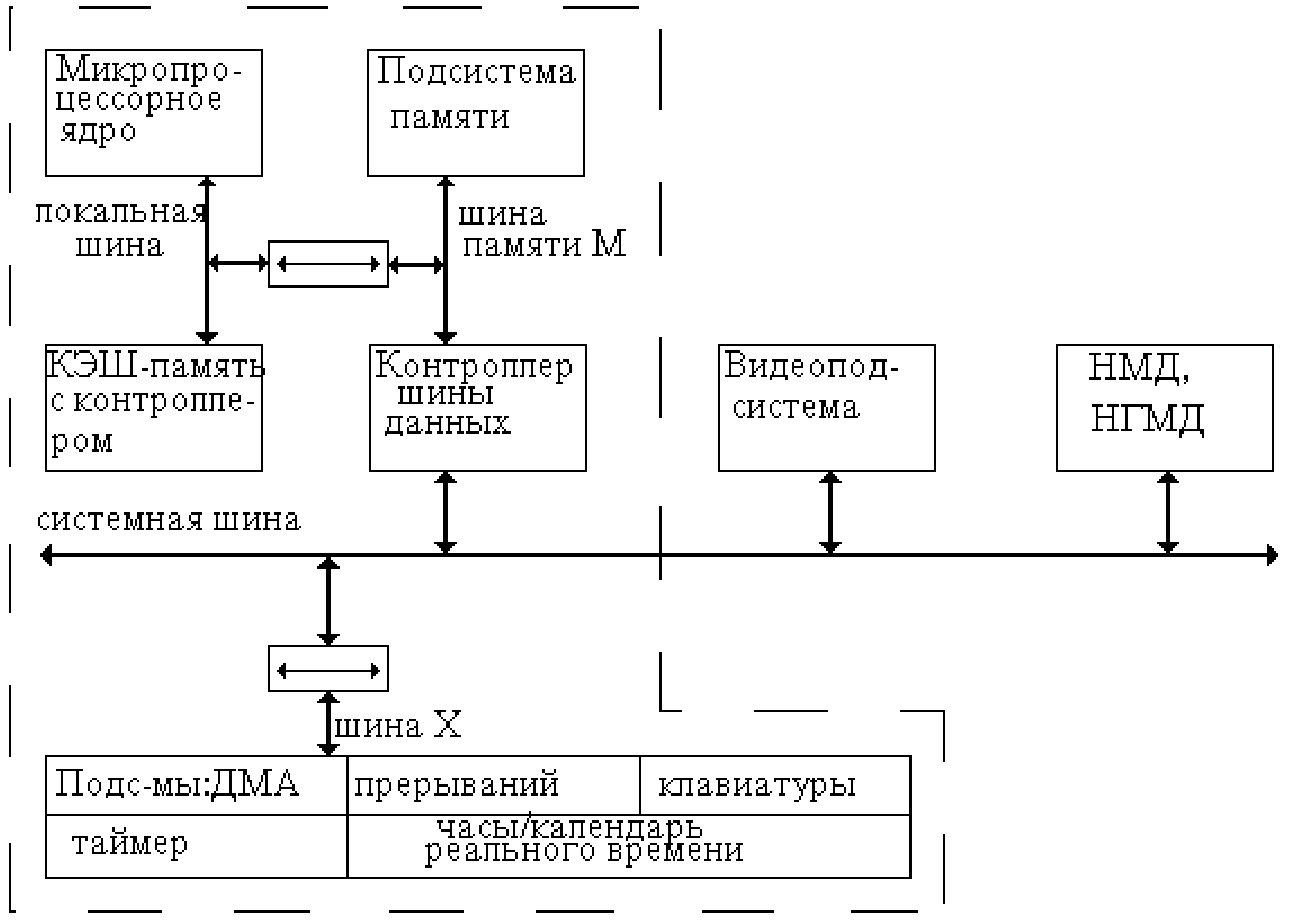

В следующем примере рассмотрена шинная организация реальной МПС ( ПК модели IBM PC/AT с КЭШ - памятью) свободная от указанных выше недостатков (рис.12.10).

Рис.12.10.

Основная оперативная память выделяется в особую подсистему и доступ к ней осуществляется не через системную шину, а параллельно с доступом системной шине при помощи обычного шинного формирователя. Шинный формирователь в данном случае обеспечивает двунаправленную передачу данных и осуществляет электрическое согласование локальной шины МП ядра и шины памяти.

Для дальнейшего ослабления требований по времени доступа к основной оперативной памяти в структурную схему IBM PC/AT введена КЭШ-память (статическая память с малым временем доступа). Объем ее от 8 до 128 кбайт. При объеме КЭШ-памяти в 64 кбайта вероятность того, что необходимая МП информация окажется в ней, составляет 95-98 %. Эффективность КЭШ-памяти становится значительной на частотах выше 20 МГц, т.к. в этом случае потери производительности из-за задержек доступа к ОП очень чувствительны.

При этом на локальной шине, кроме микропроцессора и сопроцессора, появляется контроллер управления КЭШ-памятью. Системные и локальные шины ПЭВМ типа IBM стандартизованы.

В компьютерах PC/AT на базе МП i80268, используется шина ISA (Industry Standart Architecture).

В ПЭВМ на базе i80386 и i486 используеся шина EISA (Extended Industry Standart Architecture).

Основные характеристики шины ISA:

- тактовая частота 8 Мгц;

- 16-разрядная шина данных;

- 24-разрядная шина адреса, обеспечивающая прямую адресацию 16 Мбайт системной памяти;

- 15 линий аппаратных прерываний;

- 7 каналов DMA (прямого доступа к памяти).

Основные характеристики шины EISA:

- 32 разряда передачи данных;

- 32 разряда шины адреса (прямая адресация Гигабайтного прост-ранства);

- 7 каналов DMA;

- тактируемая частота 8-10 МГц.

Локальные шины стандартизованы в меньшей степени. Однако в последнее время также появились две стандартные локальные шины: VL-us и PCI. Основным назначением локальной шины является увеличение быстродействия ПЭВМ, позволяя таким периферийным устройствам, как видеоадаптеры и контроллеры накопителей, работать с тактовой частотой до 33МГц и выше.