- •Эвм и вычислительные системы».

- •Часть I.

- •Лекция №1 общие сведения о микропроцессорах и микропроцессорных системах.

- •Предисловие

- •1.1 . Основные определения и классификация микропроцессорных систем.

- •1.2. Однокристальные мп.

- •1.2.1 Краткий исторический обзор развития.

- •Лекция №2 обзор микропроцессоров фирм клонмейкеров. Современный уровень развития однокристальных микропроцессоров.

- •2.1. Микропроцессоры-клоны.

- •2.2. Современные универсальные однокристальные микропроцессоры.

- •Процессоры Pentium II.

- •2.2.1. Процессоры фирмы amd

- •2.2.2.ПроцессорыфирмыCyrix.

- •2.2.3. Сравнительный анализ мп различных семейств.

- •2.2.4. Перспективы развития.

- •2.3. Программируемые микроконтроллеры.

- •Лекция №3 обзор микропроцессоров с микропрограммным управлением и микропроцессоров с сокращенным набором команд.

- •3.1. Мп с микропрограммным управлением.

- •3.2. Мп с сокращенным набором команд.

- •3.2.1. Risc-процессоры: предпосылки создания.

- •3.2.2. Принципы risc

- •3.2.3. Особенности risc-процессоров.

- •3.2.4. Представители группы risc-процессоров.

- •3.2.5. Цифровые процессоры обработки сигналов.

- •Лекция №4 представление информации в мпс.

- •4.1. Способы кодирования информации в мпс.

- •4.2 Двоичный формат.

- •4.3. Двоично-десятичная система кодирования.

- •4.4. Шестнадцатиричная система счисления.

- •4.4. Формат с плавающей точкой.

- •4.5. Кодирование команд.

- •Лекция №5 архитектура мп и мпс.

- •5.1. Понятие организации и архитектуры мп и мпс.

- •5.2 Обобщенная функциональная схема мп.

- •5.2.1 Устройство управления на основе аппаратной реализации.

- •5.2.2. Программируемая логическая матрица.

- •Лекция №6 архитектура мп и мпс.(продолжение)

- •6.1. Функциональная схема однокристального мп.

- •6.2 Структура адресного пространства мпс.

- •6.3 Взгляд программиста на адресное пространство.

- •6.4 Понятие стека.

- •Лекция №7 способы адресации

- •7.1 Основные определения.

- •7.2 Однокомпонентные способы адресации.

- •7.2.1 Прямой способ адресации.

- •7.2.3 Способы адресации с автомодификацией.

- •7.3 Многокомпонентные способы адресации.

- •Лекция №8 основы проограммирования на языке ассемблера для мп i8086.

- •8.1. Формат команд на языке встроенного ассемблера.

- •8.2. Архитектура мп i8086.

- •8.2.1 Сегментация памяти мп i8086.

- •8.2.2 Структура мп i8086.

- •8.2.3 Устройство шинного интерфейса.

- •8.2.4 Операционное устройство(оу).

- •8.3 Основные команды языка Ассемблер для мп i8086.

- •8.3.1 Команды пересылки данных.

- •Лекция №9 основы проограммирования на языке ассемблера для мп i8086. (продолжение).

- •9.1. Арифметические команды.

- •9.2. Логические команды.

- •9.3. Команды передачи управления.

- •9.4. Команды управления мп.

- •Лекция №10 запоминающие устройства.

- •10.1 Основные характеристики полупроводниковых запоминающих устройств.

- •10.2 Способы организации бис зу.

- •10.3 Классификация полупроводниковых зу.

- •10.3.1. Статические озу (Static Random Access Memory).

- •10.3.2. Озу динамического типа (Dynamic Random Access Memory dram).

- •10.3.4. Кмоп - озу.

- •Лекция №11 запоминающие устройства. (продолжение)

- •11.1. Постоянные зу. (Read Only Memory - rom).

- •11.2. Flash-память.

- •11.3. Корпуса модулей зу.

- •11.4. Наращивание объема и разрядности памяти, построенной на полупроводниковых зу.

- •Лекция № 12 организация магистралей мпс.

- •12.1 Типы магистралей мпс.

- •12.2 Циклы обращения к магистрали.

- •12.3 Примеры архитектур системных магистралей современных мпс.

- •Лекция №13 методы расширения адресного пространства мпс.

- •13.1 Предварительные замечания.

- •13.2 Метод окна.

- •13.3 Метод базовых регистров.

- •13.4 Метод банков.

- •13.5 Метод виртуальной памяти.

- •Лекция №14 система прерываний.

- •14.1 Понятие системы прерываний, классификация систем прерываний.

- •14.2. Организация радиальной системы прерываний.

- •14.3. Расширение радиальной системы прерываний методом поллинга.

- •14.4. Организация векторной системы прерываний.

- •Лекция №15 организация связи мпс с переферийными устройствами.

- •15.1. Классификация способов обмена информацией в мпс.

- •Прямой ввод/ вывод

- •15.3 Условный ввод-вывод.

- •15.4. Режим прямого доступа к памяти.

- •Лекция №16 интерфейсы мпс.

- •16.1. Принципы организации и классификация интерфейсов.

- •16.2. Элементная база интерфейсов.

- •16.3. Средства параллельного ввода/вывода.

- •Лекция №17 расширитель интерфейса для ibm-совместимых пк. Программируемый интервальный таймер.

- •17.1. Расширитель интерфейса рс на основе ппа кр580вв55.

- •17.2 Программируемый интервальный таймер.

- •17.3. Модуль преобразования цифрового кода в шим-сигнал на базе пит.

- •Лекция №18 интерфейсы последовательной связи.

- •18.1. Общая характеристика последовательной связи.

- •18.2. Асинхронные последовательные интерфейсы.

- •18.3. Бис для организации последовательного интерфейса.

- •18.4. Модем.

- •18.5. Стандарты физической связи. Стандарт rs -232- c.

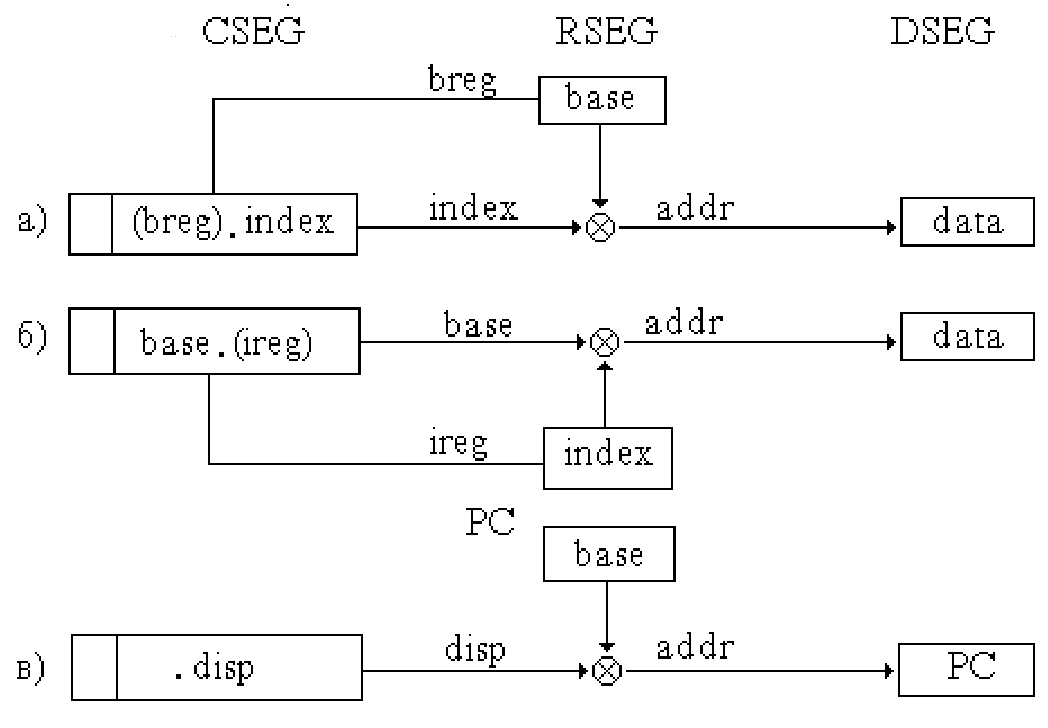

7.3 Многокомпонентные способы адресации.

При многокомпонентных способах адресации для построения исполнительного адреса используется несколько источников адресной информации, содержимое которых суммируется. Каждое слагаемое - это прямо или косвенно заданный адресный компонент (возможен вариант компонента с автомодификацией). В двухкомпонентном случае практический интерес представляют следующие комбинации способов адресации:

- прямая + косвенная регистровая;

- косвенная регистровая + косвенная регистровая.

Схемы двухкомпонентных способов адресации приведены на рис. 7.5.

В случае адресации по базе исполнительный адрес формируется по схеме, приведенной на рис.7.5.а,

![]()

Пример:

![]()

Адресация по базе необходима для организации доступа к конкретным полям блока данных, адреса которого могут быть неизвестены во время написания программы. Например, размещение блока данных определяется только в момент загрузки. В такой ситуации переменный адрес начала блока (базу) удобно располагать в регистре brеg (базовом), а известный относительный адрес элемента (индекс) хранить непосредственно в команде.

Схема вычисления исполниетльного адреса при индексной адресации показана на рис.7.5.б и похожа на схему вычисления по базе:

![]()

Пример:

![]()

Однако методика ее использования иная.

Рис.7.5.

Индексная адресация применяется при последовательном доступе к элементам структурированных данных (массив, таблица, очередь и т.д.), начальный адрес размещения которых (база) известен. При этом номер элемента структуры (индекс) является переменной, вычисляемой во время исполнения программы, поэтому индекс удобно хранить в регистре ireg (индексном), а базу - в объектном коде команды.

Отличие индексной адресации от адресации по базе состоит в том, что в объектном коде должен храниться полный адрес памяти base=еа.

Разновидностью адресации по базе является относительная адресация (рис.7.5.в).

В этом случае в качестве базового регистра breg используется РС, указываемый неявно. Данный способ адресации используется, например, в командах безусловного перехода:

![]()

В командах хранится смещение относительно текущего значения РС.

Относительная адресация применяется для создания позиционно-независимых программ, т.е. программ, работа которых не зависит от их размещения в памяти.

Двухкомпонентная косвенная регистровая адресация может быть получена, когда обе компоненты, и база, и индекс заданы косвенно (базо-индексная адресация). Способ симметричен по отношению к своим компонентам только при одинаковой размерности регистров (базового и индексного).

Лекция №8 основы проограммирования на языке ассемблера для мп i8086.

План лекции

1. Понятие встроенного ассемблера.

2. Формат команд на языке встроенного ассемблера.

3. Архитектура МП i8086.

4. Основные команды ассемблера.

5. Примеры простых программ.

8.1. Формат команд на языке встроенного ассемблера.

Для программирования задач реального времени (разработки управляющих программ), как правило, пользуются языком программирования низкого уровня - Ассемблер. Это вызвано рядом причин:

- во-первых, код, полученный после трансляции программы с языка Ассемблер, является оптимальным как по объему, так по времени исполнения;

- во-вторых, возможность управления всеми ресурсами вычислительной системы;

- в-третьих, зачастую микроконтроллеры не имеют трансляторов с языков программирования высокого уровня.

Однако, у языка Ассемблер есть и один существенный недостаток – это трудность организации удобного диалога с пользователем. В связи с этим, целесообразно для написания тестовых, учебных программ использовать два языка программирования:

- язык программирования высокого уровня для ввода исходных данных и вывода результата;

- язык программирования низкого уровня для реализации алгоритма управления в режиме реального времени.

В данном разделе рассмотрены основы построения программ с использованием языков Турбо Паскаль и Ассемблер для ПК типа IBM PC/AT. Начиная с версии 6.0, Турбо Паскаль имеет так называемый встроенный Ассемблер, позволяющий писать программы или их части на языке Ассемблера. Фрагменты, написанные на языке Ассемблера, могут произвольным образом чередоваться с частями, написанными на Турбо Паскале, однако программист должен строго соблюдать следующее условие: к моменту завершения ассемблерной части содержимое регистров BP, SP, SS, DS МП должно быть точно таким, каким оно было при входе в ассемблерную часть программы.

Ассемблерная часть начинается зарезервированным словом asm и заканчивается словом end; между этими словами могут размещаться одно или несколько предложений языка Ассемблера:

asm

< предложения языка Ассемблера>

end;

Каждое предложение размещается на отдельной строке. Допускается также размещать несколько предложений на отдельной строке, разделяя их символами “;” .

В общем случае, каждое предложение имеет следующую структуру:

<метка> <код инструкции> <операнды>.

Любая из этих частей может быть опущена .

Часть <метка> - именует команду программы и определяет локальную метку. Метки используются в качестве операндов в командах передачи управления. Локальные метки начинаются символом @, они легко распознаются Ассемблером и не нуждаются в предварительном описании. В конце локальной метки ставится символ “:”.

Часть <код инструкции> определяет код команды центрального процессора ПК и/или арифметического сопроцессора (Intel 8086, 8088, 80286, 80287 и т.д.).

Часть <операнды> содержит необходимые операнды данной команды процессора (сопроцессора).

В качестве операндов могут выступать непосредственно данные, переменные Турбо Паскаля, либо зарезервированные слова Ассемблера, такие как названия регистров МП, логических операций, типов данных и т.д.

Язык Ассемблера является машинноориентированным языком, это означает, что он определяется типом процессора. Вследствие этого, для того чтобы научиться писать программы на Ассемблере для МПС, необходимо прежде всего познакомиться с архитектурой МП.

МП Intel 8086 из всего семейства МП фирмы Intel 80x86 обладает наиболее простой архитектурой и кроме того, при его разработке были использованы основные принципы, которые в дальнейших версиях МП получили свое развитие.

Поэтому знакомство с Ассемблером для ПЭВМ фирмы Intel IBM PC/АТ мы начнем с рассмотрения архитектуры МП i8086 .