- •Эвм и вычислительные системы».

- •Часть I.

- •Лекция №1 общие сведения о микропроцессорах и микропроцессорных системах.

- •Предисловие

- •1.1 . Основные определения и классификация микропроцессорных систем.

- •1.2. Однокристальные мп.

- •1.2.1 Краткий исторический обзор развития.

- •Лекция №2 обзор микропроцессоров фирм клонмейкеров. Современный уровень развития однокристальных микропроцессоров.

- •2.1. Микропроцессоры-клоны.

- •2.2. Современные универсальные однокристальные микропроцессоры.

- •Процессоры Pentium II.

- •2.2.1. Процессоры фирмы amd

- •2.2.2.ПроцессорыфирмыCyrix.

- •2.2.3. Сравнительный анализ мп различных семейств.

- •2.2.4. Перспективы развития.

- •2.3. Программируемые микроконтроллеры.

- •Лекция №3 обзор микропроцессоров с микропрограммным управлением и микропроцессоров с сокращенным набором команд.

- •3.1. Мп с микропрограммным управлением.

- •3.2. Мп с сокращенным набором команд.

- •3.2.1. Risc-процессоры: предпосылки создания.

- •3.2.2. Принципы risc

- •3.2.3. Особенности risc-процессоров.

- •3.2.4. Представители группы risc-процессоров.

- •3.2.5. Цифровые процессоры обработки сигналов.

- •Лекция №4 представление информации в мпс.

- •4.1. Способы кодирования информации в мпс.

- •4.2 Двоичный формат.

- •4.3. Двоично-десятичная система кодирования.

- •4.4. Шестнадцатиричная система счисления.

- •4.4. Формат с плавающей точкой.

- •4.5. Кодирование команд.

- •Лекция №5 архитектура мп и мпс.

- •5.1. Понятие организации и архитектуры мп и мпс.

- •5.2 Обобщенная функциональная схема мп.

- •5.2.1 Устройство управления на основе аппаратной реализации.

- •5.2.2. Программируемая логическая матрица.

- •Лекция №6 архитектура мп и мпс.(продолжение)

- •6.1. Функциональная схема однокристального мп.

- •6.2 Структура адресного пространства мпс.

- •6.3 Взгляд программиста на адресное пространство.

- •6.4 Понятие стека.

- •Лекция №7 способы адресации

- •7.1 Основные определения.

- •7.2 Однокомпонентные способы адресации.

- •7.2.1 Прямой способ адресации.

- •7.2.3 Способы адресации с автомодификацией.

- •7.3 Многокомпонентные способы адресации.

- •Лекция №8 основы проограммирования на языке ассемблера для мп i8086.

- •8.1. Формат команд на языке встроенного ассемблера.

- •8.2. Архитектура мп i8086.

- •8.2.1 Сегментация памяти мп i8086.

- •8.2.2 Структура мп i8086.

- •8.2.3 Устройство шинного интерфейса.

- •8.2.4 Операционное устройство(оу).

- •8.3 Основные команды языка Ассемблер для мп i8086.

- •8.3.1 Команды пересылки данных.

- •Лекция №9 основы проограммирования на языке ассемблера для мп i8086. (продолжение).

- •9.1. Арифметические команды.

- •9.2. Логические команды.

- •9.3. Команды передачи управления.

- •9.4. Команды управления мп.

- •Лекция №10 запоминающие устройства.

- •10.1 Основные характеристики полупроводниковых запоминающих устройств.

- •10.2 Способы организации бис зу.

- •10.3 Классификация полупроводниковых зу.

- •10.3.1. Статические озу (Static Random Access Memory).

- •10.3.2. Озу динамического типа (Dynamic Random Access Memory dram).

- •10.3.4. Кмоп - озу.

- •Лекция №11 запоминающие устройства. (продолжение)

- •11.1. Постоянные зу. (Read Only Memory - rom).

- •11.2. Flash-память.

- •11.3. Корпуса модулей зу.

- •11.4. Наращивание объема и разрядности памяти, построенной на полупроводниковых зу.

- •Лекция № 12 организация магистралей мпс.

- •12.1 Типы магистралей мпс.

- •12.2 Циклы обращения к магистрали.

- •12.3 Примеры архитектур системных магистралей современных мпс.

- •Лекция №13 методы расширения адресного пространства мпс.

- •13.1 Предварительные замечания.

- •13.2 Метод окна.

- •13.3 Метод базовых регистров.

- •13.4 Метод банков.

- •13.5 Метод виртуальной памяти.

- •Лекция №14 система прерываний.

- •14.1 Понятие системы прерываний, классификация систем прерываний.

- •14.2. Организация радиальной системы прерываний.

- •14.3. Расширение радиальной системы прерываний методом поллинга.

- •14.4. Организация векторной системы прерываний.

- •Лекция №15 организация связи мпс с переферийными устройствами.

- •15.1. Классификация способов обмена информацией в мпс.

- •Прямой ввод/ вывод

- •15.3 Условный ввод-вывод.

- •15.4. Режим прямого доступа к памяти.

- •Лекция №16 интерфейсы мпс.

- •16.1. Принципы организации и классификация интерфейсов.

- •16.2. Элементная база интерфейсов.

- •16.3. Средства параллельного ввода/вывода.

- •Лекция №17 расширитель интерфейса для ibm-совместимых пк. Программируемый интервальный таймер.

- •17.1. Расширитель интерфейса рс на основе ппа кр580вв55.

- •17.2 Программируемый интервальный таймер.

- •17.3. Модуль преобразования цифрового кода в шим-сигнал на базе пит.

- •Лекция №18 интерфейсы последовательной связи.

- •18.1. Общая характеристика последовательной связи.

- •18.2. Асинхронные последовательные интерфейсы.

- •18.3. Бис для организации последовательного интерфейса.

- •18.4. Модем.

- •18.5. Стандарты физической связи. Стандарт rs -232- c.

6.4 Понятие стека.

В пространстве данных МПС DSEG , как правило, выделяют специально-организованную область памяти называемую системным стеком SSEG или стеком времени выполнения.

Системный стек предназначен для хранения адресов возврата и состояний МП при вызове подпрограмм и обслуживании прерываний. Стек может также использоваться для временного хранения переменных и передачи параметров при вызове подпрограмм.

Стек - это область памяти с доступом типа "последним пришел - первым вышел" или LIFО (Last Input - First Output). Стек обычно заполняется в сторону уменьшения адресов.

Для адресации стека используется специальный регистр МП, называемый указателем стека - SР (Stack Pointer). Указатель стека всегда показывает (содержит адрес) на последнюю заполненную ячейку стека – называемую вершиной стека ТОS - Top Of Stack.

Отличительной особенностью данного регистра (SР) является то, что он относится к регистрам с автомодификацией. Это означает, что он автоматически изменяет свое состояние на число записанных или считанных байт (уменьшает или увеличивает в зависимости от операции) после выполнения операции доступа.

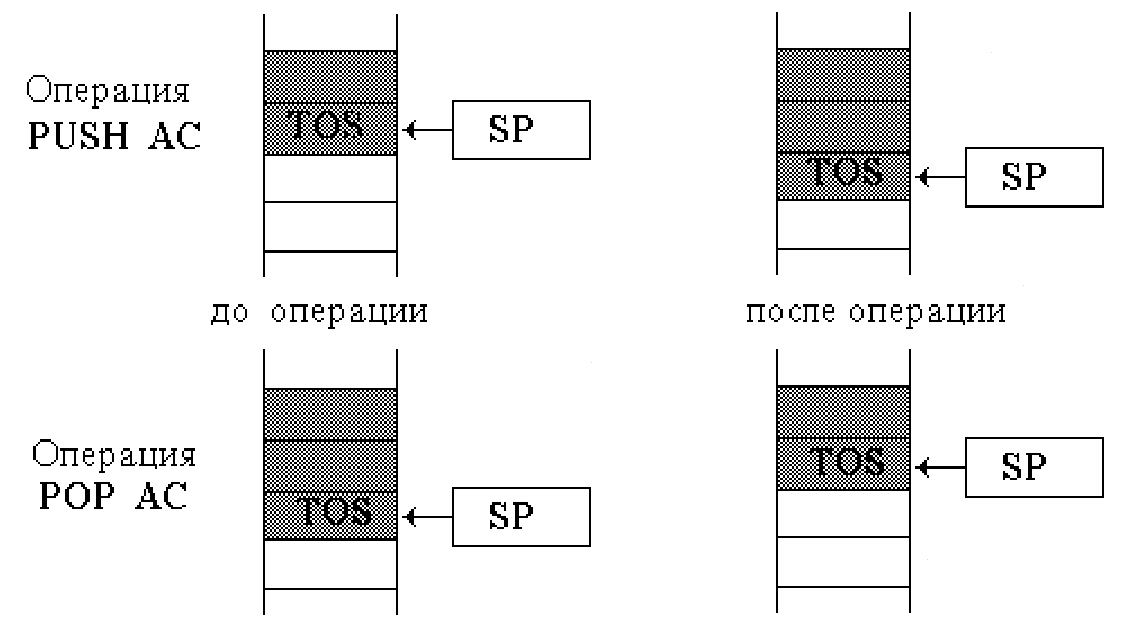

При записи в стек байта данных (операция PUSH) содержимое SР уменьшается на 1 и затем используется в качестве адреса новой вершины, в которую заносится элемент.

При считывании байта данных из стека (операция РОР) сначала считывается содержимое ТОS, а затем содержимое SР автоматически увеличивается на 1 для адресации новой вершины стека. Работа стека показана на рис.6.4.

Исключительные удобства, представляемые стеком при вызове подпрограмм (п/п), привели к тому, что практически все современные МП имеют средства для его построения в виде регистра SР.

Рис.6.4.

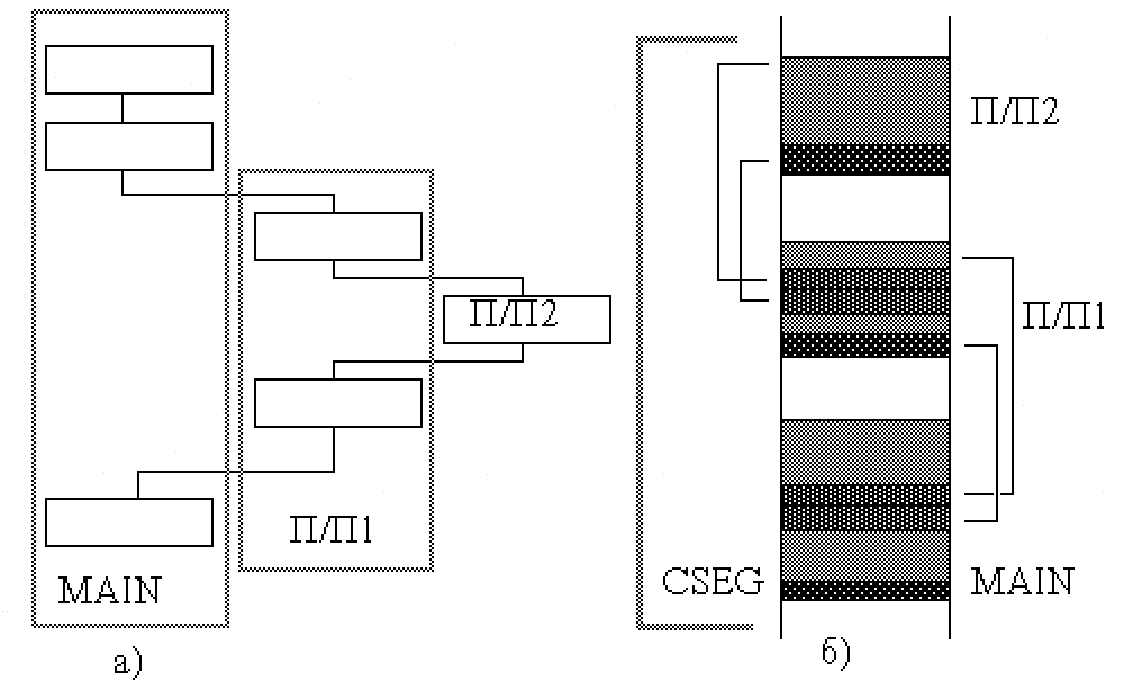

Рассмотрим процесс вызова п/п при помощи системного стека. Допустим, что наша программа включает в себя основной модуль (MAIN) и две п/п. Передача управления из вызывающей программы в п/п и обратно отражена на рис.6.5 при помощи стрелок.

Рис.6.5.

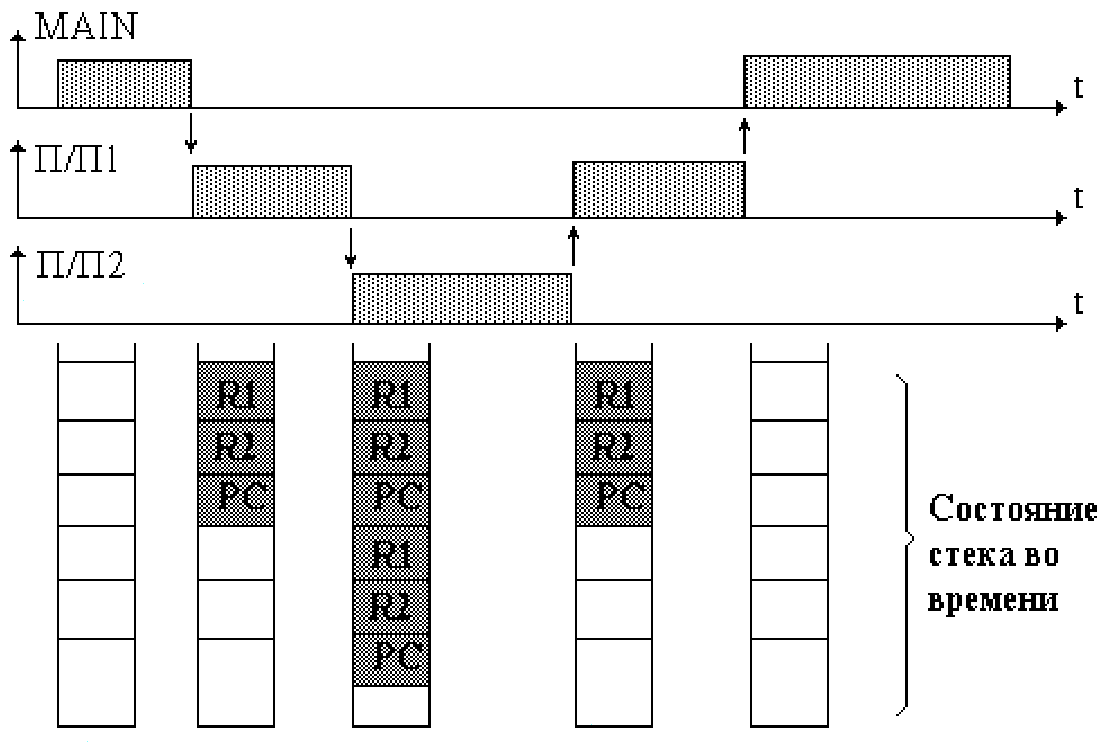

При организации вызова п/п, МП должен обеспечить возможность возврата из п/п, после ее завершения, к следующей команде вызывающей программы. С этой целью перед передачей управления п/п, т.е. изменение РС, МП сохраняет свое старое состояние (значение регистров РОН и РС) в стеке. При выходе из п/п МП, обращаясь к стеку, восстанавливает значение своих регистров. Процесс вызова п/п отражен диаграммой (рис.6.6).

Рис.6.6.

Лекция №7 способы адресации

План лекции

1. Основные определения.

2. Однокомпонентные способы адресации.

3. Прямой способ адресации.

4. Адресация с вычисляемым адресом.

5. Многокомпонентые способы адресации.

7.1 Основные определения.

Рассмотрим, каким образом МП распознает откуда ему необходимо извлечь данные для выполнения команды и куда переслать результат.

Ранее мы определили, что источниками и приемниками операндов в МПС могут служить регистровая память RSEG, память данных DSEG, а также порты ВВ IОSEG. В дальнейшем для обозначения элементов указанных областей будем использовать соответственно следующие символы: reg, addr, port.

Адрес операнда, считываемого или размещаемого в одном из пространств МПС, называется исполнительным.

Сведения об исполнительных адресах закодированы в командах и могут быть представлены в явной и неявной формах. В первом случае, последовательность бит, определяющая команду, включает в себя поле кода операции и адресные поля. Код операции непосредственно предписывает действия, которые необходимо выполнить МП (сложить, переслать и т.п.) и способ формирования исполнительного адреса, информация, необходимая для формирования которого содержится в адресных полях.

Неявная форма обеспечивает передачу адресной информации в поле кода операции, т.е. сама операция несет информацию о месте нахождения одного или всех операндов, используемых в ней.

Явная форма представления более гибкая, вследствие того, что одна и та же команда может использоваться для адресации различных объектов, но требует увеличения поля команды, что снижает эффективность объектного кода. Неявная форма, связывая часть адресной информации с операцией, сужает ее действие, но длина машинной команды при этом уменьшается, вследствие того, что отсутствует адресное поле.

В реальных командах, как правило, применяются обе формы представления адресной информации, т.е. часть информации о месте нахождения одного операнда передается в неявной форме (источником или приемником является регистр), остальная часть информации передается в явной форме в адресном поле.

Для обеспечения эффективного доступа к различным структурам данных (массивы, стеки, списки), а также перемещаемости программ и данных на этапах загрузки и выполнения, разработан целый ряд способов построения исполнительного адреса, называемых способом адресации (mоd) или просто адресацией.