- •Эвм и вычислительные системы».

- •Часть II.

- •Оглавление.

- •Лекция №19 конструкция персонального компьютера.

- •19.1. Основные конструктивные компоненты персонального компьютера.

- •19.2. Корпус пк.

- •19.3. Блок питания.

- •19.4. Системные платы.

- •19.5. Конструктивы и установка плат.

- •Лекция №20 ключевые микросхемы.

- •20.1. Стандартные микросхемы первых системных плат.

- •20.2. Набор микросхем или - chipset.

- •20.3. Микропроцессоры.

- •20.4. Организация доступа к памяти при использовании intel совместимых процессоров

- •Лекция №21 память компьютера

- •21.1. Иерархия подсистемы памяти пк.

- •21.2. Оперативная память.

- •21.3. Архитектура оперативной памяти.

- •21.4. Логическая организация памяти.

- •Лекция № 22 базовая система ввода/вывода.

- •22.1. Bios и cmos ram. Общие сведения.

- •22.2. Возможности bios. Конфигурирование системных ресурсов.

- •22.3. Тест начальной загрузки post.

- •Лекция № 23 кэш – память

- •23.1. Принципы построения кэш-памяти.

- •23.2. Типы кэшей

- •23.3. Целостность данных в кэш-памяти

- •23.4. Кэш-память и эффективность программ

- •Лекция №24 накопители на жестких дисках.

- •24.1. Типы накопителей.

- •24.2. Накопители на жестких дисках. (Винчестеры)

- •24.3. Параметры жестких дисков

- •24.4. Низкоуровневое форматирование

- •24.5. Логическая структура диска

- •24.6. Загрузочный сектор br (Boot Record).

- •24.7. Таблица размещения файлов fat (File Allocation Table).

- •24.8. Корневой каталог (root Directory).

- •24.9. Главный загрузочный сектор mbr (Master Boot Record).

- •24.10. Порядок установки винчестера.

- •24.11. Кэширование диска.

- •Лекция №25 интерфейсы винчестеров

- •25.1. Интерфейс st-506/412.

- •25.2. Интерфейс еsdi

- •25.3. Интерфейс scsi

- •25.4. Интерфейс ide (ata)

- •Лекция №26 шины персональных компьютеров.

- •26.1. Обзор шин пк.

- •26.2. Системные шины.

- •26.3. Локальные шины.

- •26.4. Шина pci (Peripheral Component Interconnect) (1992 год).

- •26.5. Магистральный интерфейс agp.

- •Лекция № 27 видеоподсистемы

- •27.1. Мониторы.

- •27.2. Основные стандарты мониторов (видеоадаптеров).

- •27.3. Проблемы цветопередачи.

- •27.4. Видеопамять.

- •27.5. Повышение скорости работы видеоадаптера.

- •Лекция № 28 современные видеоподсистемы персональных компьютеров.

- •28.1. Свойства современных видеоадаптеров

- •28.2. Современные видеоадаптеры

- •28.3. Архитектура персональных машин с объединенной памятью. Новая архитектура ibm-совместимых пк.

- •28.4. Варианты развития архитектуры uma

- •Лекция 29. Лекция №30 архитектура компьютера

- •30.1. Параллелизм, компьютерная архитектура и приложения пользователя

- •30.2. Однопроцессорные архитектуры

- •30.3. Многопроцессорные архитектуры

- •30.4. Выбор архитектуры

- •Лекция №31 архитектура современных программных средств План лекции

- •31.1. Программное обеспечение эвм

- •31.2. История развития программных средств эвм.

- •31.3. Структура программного обеспечения.

- •31.4. Проблемно-ориентированные пакеты прикладных программ.

- •Лекция №32 операционные системы эвм.

- •32.1. Системное программное обеспечение эвм

- •32.2. Операционные системы (ос) эвм

- •32.3. Организация операционных систем.

- •32.4. Концепция виртуальной операционной системы.

- •32.5. Типы операционных систем.

- •32.6. Операционная среда ms-dos.

- •32.7. Операционная система Unix.

- •Лекция № 33. Операционные системы эвм (продолжение).

- •33.1. Операционные оболочки эвм.

- •33.2. Многооконный графический интерфейс.

- •33.3. Инструментальное программное обеспечение (ипо) эвм.

- •33.4. Трансляторы с языка высокого уровня.

- •33.5. Двухуровневая организация схемы компилятора.

- •33.6. Естественные языки программирования.

- •Лекция № 34 прикладное программное обеспечение

- •34.1. Прикладное программное обеспечение эвм

- •34.3. Классы пакетов прикладных программ

- •34.4. Основные прикладные средства пк.

- •34.6. Качественные характеристики программного обеспечения

20.4. Организация доступа к памяти при использовании intel совместимых процессоров

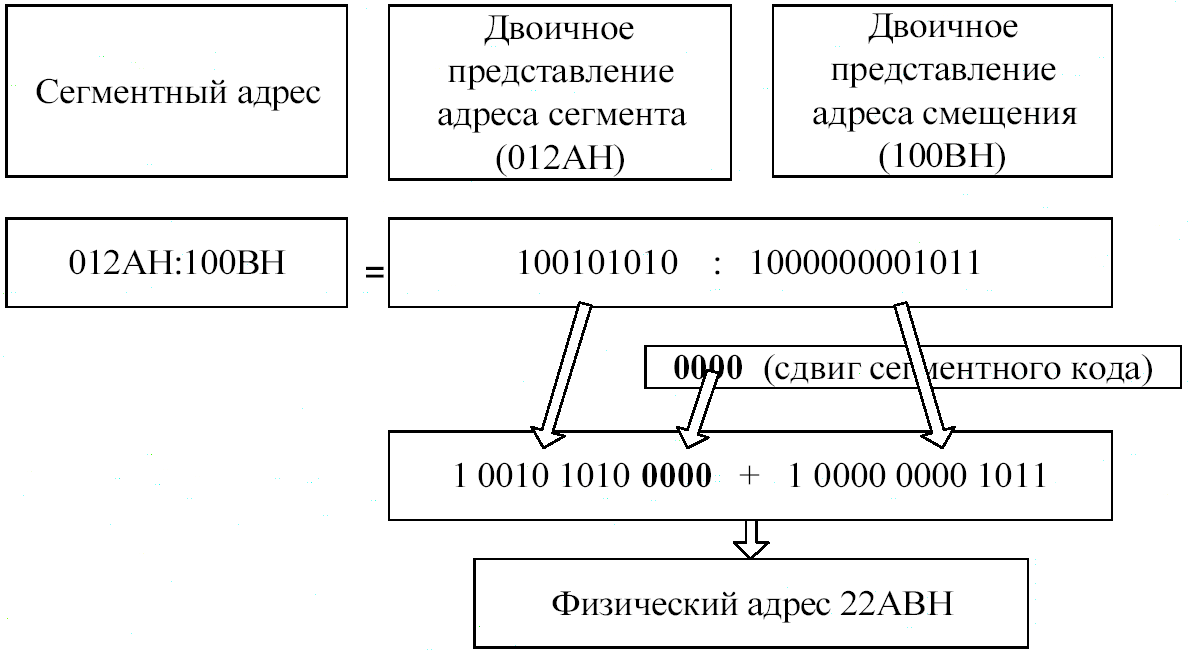

Рассмотрим адресное пространство в процессоре 8086. Он работает в так называемом реальном режиме и разбивает адресное пространство памяти на сегменты, каждый из которых содержит 64 Кбайт. Каждый сегмент начинается с адреса параграфа, т.е. байта, адрес которого кратен 16. При обращении к отдельным байтам используется смещение, которое задает точное положение байта внутри конкретного сегмента. Смещения всегда измеряются относительно начала сегмента и поэтому называются относительными адресами или относительными смещениями. Положение любого байта внутри адресного пространства i8086 определяется двумя величинами: адресами сегмента и смещения, формирующими сегментный адрес. Микропроцессор 8086 преобразует 32-битный сегментный адрес (16-битный адрес параграфа и 16-битный относительный адрес) в 20-битный физический адрес, используя для этого для этого значения адреса сегмента в качестве базового числа и добавляя к нему значение смещения внутри параграфа. Физический адрес получается следующим образом: над адресом сегмента выполняется операция арифметического сдвига на 4 бита, а затем к полученному числу прибавляется значение смещения (рис.__).

Сегментация памяти в процессоре обладает следующими особенностями, которые не позволяют работать с несколькими задачами:

- сегменты памяти имеют два атрибута: начальный адрес и максимальный размер 64 Кбайт, и никаких средств контроля правильности использования сегментов нет;

- размещение сегментов в памяти произвольно, т.е. они могут частично или полностью перекрываться, так как начальный адрес сегмента совпадает с адресом параграфа, кратного 16, или не иметь общих областей;

- не существует аппаратных систем контроля при обращении к физически отсутствующей памяти.

Микропроцессор 80286 может работать как в реальном режиме, т.е. режиме процессора 8086, так изащищенном. Указанные режимы введены с целью обеспечения преемственности ранее разработанного программного обеспечения. В первом случае адресация памяти совпадает с тем, который используется в процессоре 8086. Во втором режиме метод адресации памяти строится на других принципах (рис.20.2).

Рис.20.2.

Сегментные адреса декодируются с помощью таблицы, содержащей сегментные описатели (рис.20.3). При этом "сегментная" часть сегментного адреса является не значением параграфа, как в реальном режиме, а селектором, который представляет собой индекс для таблицы сегментных описателей. Каждый описатель в таблице содержит 24-битный базовый адрес, который указывает физическое начало сегмента в памяти, т.е. может быть адресовано 224байтов памяти. Таким образом, физические адреса имеют размер, равный 24 битам, т.е. позволяют адресовать 16 Мбайт памяти.

Рис.20.3.

Формирование адреса процессорами 80386/80486

В реальном режиме МП 80386/486 работают аналогично 8086. При работе 80386/486 в защищенном режиме возможно несколько моделей формирования адреса.

В модели плоской памяти нет сегментов (или есть один, только очень большой). Память считается единой и неразрывной. Для реализации этой модели 80386 нужно просто установить все сегментные регистры на нуль. Размер всех регистров для смещений (EIP, ESP и др.) равен 32 битам. Это допускает прямую адресацию 232байт или 4 Гбайт, что в 4000 раз больше, чем диапазон адресации 8086. Недостаток плоской модели - невозможность организовать многозадачность.

По желанию в защищенном режиме 80386 можно использовать и модель сегментированной памяти, как в 8086. Однако метод вычисления адреса в этом случае является другим.

Процессор 80386 одновременно может обращаться к шести сегментам, адресуемыми 16-битными регистрами CS, DS, СS и ES, FS, GS. Каждый из сегментов имеет дескриптор сегмента, содержащую информацию о его размере и защите. МП 80386 допускает использование сегментов до 4 Гбайт.

МП с сегментированной моделью памяти применяет 3-х ступенчатую схему формирования адреса.

Первая ступень – уровень логического адреса. Логический адрес состоит из селектора и 32-разрядного смещения (аналогично 80286).

Вторая ступень – получение из логического адреса 32-разрядного линейного адреса. Его вычисление напоминает способ вычисления 24-разрядного физического адреса в МП 80286. Однако линейный адрес не является физическим адресом.

Физическая длина сегментных регистров 64 бита, но программы "видят" только 16 бит (старшие). Указанный код используется для адресации элементов таблиц, хранящих полную информацию о сегменте – дескрипторы сегментов.

Дескриптор сегментов содержит фактическую базу сегмента до 32 бит, кроме того он определяет его размер, доступ, защищенный уровень привилегий, тип (исполняемый, читаемый, записываемый) и т.д.

Длина таблицы дескрипторов может достигать 8192 (213) дескрипторов.

Линейный адрес получают суммированием 32-битного базового адреса и 32-бтного смещения. Однако, линейный адрес не является физическим адресом.

Для получения физического адреса используются третья ступень, реализующая механизм страничной адресации. Страница памяти – это блок памяти разметом 4 Кбайта (страничные кадры). Адреса страничных кадров 0, 4К, 8К и т.д. Любой элемент данных, который начинается по любому из этих адресов, называется "выровненным по границе страницы". Т.е. в этом случае младшие 12 бит адреса – нули. Таким образом, линейный адрес разбивается на две части: 20-разрядный адрес страницы (адрес каталога – 10 бит и адрес страницы в каталоге – 10 бит) и 12-разрядного смещения.

Механизмы реализации защищенных режимов позволяют процессорам иметь гибкие средства контроля и защиты доступа к сегментам и страницам памяти.