- •186 Розділ 3. Однокристальні мікроконтролери з cisc архітектурою

- •3.1 Архітектура і функціональні можливості однокристальних мікроконтролерів

- •Таблиця 3.1 – Формат слова стану psw

- •Таблиця 3.3 – Альтернативні функції порту р3

- •Таблиця 3.4 – Призначення бітів регістра scon

- •Таблиця 3.10 – Позначення бітів регістра pcon

- •Контрольні запитання

- •3.2 Система команд

- •Контрольні запитання

- •3.3 Розширення можливостей однокристальних мікроконтролерів

- •Пам’яті даних з омк

- •Контрольні запитання

- •3.4 Застосування однокристального мікроконтролера 83c51fa для керування двигуном постійного струму

- •Таблиця 3.13 – Позначення бітів регістра режиму ccapMn

- •Контрольні запитання

- •3.5 Архітектура і функціональні можливості 16-розрядних однокристальних мікропроцесорів серії mcs 196/296

- •Контрольні запитання

186 Розділ 3. Однокристальні мікроконтролери з cisc архітектурою

Однокристальний мікроконтролерявляє собою пристрій, виконаний конструктивно в одному корпусі ВІС, що містить усі компоненти МПС: процесор, пам’ять даних, пам’ять програм, програмовні інтерфейси. Однокристальним мікроконтролерам притаманні такі особливості:

система команд орієнтована на виконання задач керування і регулювання;

алгоритми, що реалізуються на ОМК, мають багато розгалужень залежно від зовнішніх сигналів;

дані, з якими оперують ОМК, не повинні мати велику розрядність;

схемна реалізація систем керування на базі ОМК нескладна і має невисоку вартість;

універсальність і можливість розширення функцій керування значно нижче, ніж в системах з однокристальними МП.

Однокристальні мікроконтролери являють собою зручний інструмент для створення сучасних вбудованих пристроїв керування різноманітним обладнанням, як-то автомобільною електронікою, побутовою технікою, мобільними телефонами, тощо.

3.1 Архітектура і функціональні можливості однокристальних мікроконтролерів

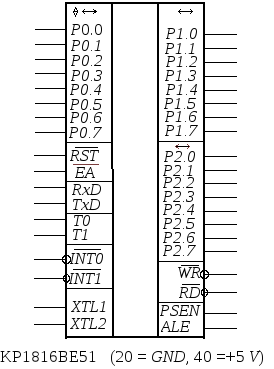

Структуру ОМК та функціонування основних блоків розглянемо на прикладі ВІС К1816ВЕ51 (i80x51) (рис. 3.1). Графічне позначення мікросхеми наведено на рис. 3.2.

Рис. 3.1 – Структурна схема ОМК К1816ВЕ51

Структурна схема ОМК містить:

блок 8-розрядного центрального процесора ЦП;

пам’ять програм ПЗП ємністю 4 Кбайт;

пам’ять даних ОЗП ємністю 128 байт;

чотири 8-розрядних програмовних порти введення-виведення Р0-Р3;

послідовний порт;

два 16-розрядних програмовних таймери/лічильники Т/С0,Т/С1;

систему переривань з п’ятьма векторами і двома рівнями пріоритетів;

блок керування БК.

Рис. 3.2 – Графічне позначення ОМК К1816ВЕ51

Блок ЦП містить 8-розрядний АЛП, два акумулятори А і В, регістр слова стану процесора PSW (Processor State Word) та програмно-недоступні буферні регістри ЧА і ЧР, що виконують функції розподілу вхідних та вихідних даних АЛП. Центральний процесор виконує операції додавання, віднімання, множення, ділення, логічні операції І, АБО, НЕ, ВИКЛЮЧАЛЬНЕ АБО, операції зсуву і скидання. Він оперує з такими типами змінних: булевими (1 біт), цифровими (4 біт), байтовими (8 біт) і адресними (16 біт). Характерною особливістю ОМК є великий набір операцій з бітами: окремі біти змінних можуть бути встановлені, скинуті, інвертовані, перевірені, передані. Це дозволяє легко реалізовувати алгоритми, що містять операції над булевими змінними типу “так-ні” (“true-false”).

Акумулятор Ає джерелом одного з операндів і місцем розміщення результату виконання багатьох команд. Ряд команд, наприклад, передача інформації в/із ОЗП, командиTEST,INC,DECможуть виконуватися без участі акумулятора. АкумуляторВвикористовується як акумулятор лише в командах множення і ділення, а в інших випадках – як РЗП

Регістр слова стану процесора PSWзберігає інформацію про стан АЛП у процесі виконання програми і має формат, наведений у табл. 3.1.

Таблиця 3.1 – Формат слова стану psw

|

Біт |

Позначення |

Призначення |

Доступ до біта |

|

7 |

C |

Прапорець перенесення |

А або П |

|

6 |

AC |

Прапорець додаткового перенесення |

А або П |

|

5 |

F0 |

Прапорець користувача |

П |

|

4 |

RS1 |

Вказівник банку робочих регістрів: 00 – банк 0; 10 – банк 2; 01 – банк 1; 11 – банк 3 |

П |

|

3 |

RS0 | ||

|

2 |

OV |

Прапорець переповнення |

П |

|

1 |

– |

Резервний |

П |

|

0 |

P |

Біт парності |

А або П |

Примітка. У таблиці 3.1 використано такі позначення: А – біт встановлюється апаратно, П – програмно.

Призначення прапорців C, AC аналогічне призначенню прапорців CF, AF у МП і8086. Прапорець OV встановлюється у командах додавання і віднімання, якщо результат перевищує ємність 7 біт і старший біт не може бути інтерпретований як знаковий; у командах ділення OV скидається, а при діленні на нуль – встановлюється. У командах множення OV набуває значення логічної одиниці, якщо результат перевищує 0FFH. Прапорець Р є доповненням вмісту акумулятора А до парності, тобто 9-розрядне слово, яке складається з 8 біт акумулятора А і біта Р, має завжди парну кількість одиниць.

Постійний запам’ятовувальний пристрій або резидентна пам’ять програм (РПП) має інформаційну ємність 4 Кбайт і виконаний у вигляді ПЗП, програмованого маскою. Інші ОМК, наприклад, К1816751, мають ПЗП EPROM (див. табл.3.1). ПЗП має 16-розрядну адресну шину, що дозволяє розширити пам’ять до 64 Кбайт через під’єднання зовнішніх ВІС ПЗП. Адреса визначається вмістом лічильника команд PC (Program Counter) або вмістом регістра-вказівника даних DPTR (Data Pointer Register). Регістр DPTR використовується при непрямих переходах у програмі або при адресації таблиць або як один 16-розрядний регістр, або як два незалежних 8-розрядних регістри DPH і DPL.

Розподіл адресного простору ПЗП показано на рис. 3.3. Молодші адреси ПЗП відводяться під обробку переривань і початок роботи ОМК після скидання.

|

Скидання |

|

|

Внутрішня пам’ять програм |

0000H |

|

|

|

|

0003H |

INT0 | ||

|

Вектори переривань |

|

000BH |

T/C0 | ||

|

|

0013H |

INT1 | |||

|

|

001BH |

T/C1 | |||

|

|

|

0023H |

TI+RI | ||

|

|

|

|

| ||

|

|

|

|

|

| |

|

|

|

|

0FFFH |

| |

|

|

|

|

Зовнішня пам’ять програм |

1000H |

|

|

|

|

|

|

| |

|

|

|

|

|

| |

|

|

|

|

FFFFH |

|

Рис. 3.3 – Розподіл адресного простору РПП

Оперативний запам’ятовувальний пристрій або резидентна пам’ять даних (РПД) (рис.3.4) складається з двох областей.

|

00H |

R0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

БАНК 0 |

|

|

|

Прямо адресовані біти | ||||||||

|

07H |

R7 |

|

|

|

|

|

|

|

|

|

|

|

| |

|

08H |

R0 |

|

|

|

|

D7 |

|

|

|

|

|

|

D0 | |

|

|

|

БАНК 1 |

|

|

20H |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 | |

|

0FH |

R7 |

|

|

|

21H |

0F |

0E |

0D |

0C |

0B |

0A |

09 |

08 | |

|

10H |

R0 |

|

|

Внутрішній ОЗП Пряма та непряма адресація |

22H |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 | |

|

|

|

БАНК 2 |

|

23H |

1F |

1E |

1D |

1C |

1B |

1A |

19 |

18 | ||

|

17H |

R7 |

|

|

24H |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 | ||

|

18H |

R0 |

|

|

25H |

2F |

2E |

2D |

2C |

2B |

2A |

29 |

28 | ||

|

|

|

БАНК 3 |

|

26H |

37 |

36 |

35 |

34 |

33 |

32 |

31 |

30 | ||

|

1FH |

R7 |

|

|

27H |

3F |

3E |

3D |

3C |

3B |

3A |

39 |

38 | ||

|

20H |

Прямо адресовані біти |

|

28H |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 | |||

|

|

|

29H |

4F |

4E |

4D |

4C |

4B |

4A |

49 |

48 | ||||

|

2FH |

|

2AH |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 | ||||

|

|

|

|

|

|

2BH |

5F |

5E |

5D |

5C |

5B |

5A |

59 |

58 | |

|

|

|

|

|

|

2CH |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 | |

|

7FH |

|

|

|

|

2DH |

6F |

6E |

6D |

6C |

6B |

6A |

69 |

68 | |

|

80H |

Регістри спеціальних функцій (лише пряма адресація) |

|

|

2EH |

77 |

76 |

75 |

74 |

73 |

72 |

71 |

70 | ||

|

|

|

|

2FH |

7F |

7E |

7D |

7C |

7B |

7A |

79 |

78 | |||

|

FFH |

|

|

|

|

|

|

|

|

|

|

| |||

Рис. 3.4 – Резидентна пам’ять даних

Перша область – ОЗП даних з інформаційною ємністю 128 х 8 біт з адресами 0-7FН. Друга область – регістри спеціальних функцій (SFR – Special Function Registers) з адресами 80Н-FFН. Перерахунок регістрів спеціальних функцій наведено в табл. 3.2.

Таблиця 3.2 – Регістри спеціальних функцій

|

Позначення |

Найменування, адреси бітів |

Адреса |

Значення після скидання | ||||||||||||||||

|

1 |

2 |

3 |

4 | ||||||||||||||||

|

АСС* |

Акумулятор А

|

0Е0Н |

00 | ||||||||||||||||

|

В* |

Акумулятор В

|

0F0H |

00 | ||||||||||||||||

|

PSW* |

Слово стану програми

|

0D0H |

00 | ||||||||||||||||

|

SP |

Регістр-вказівник стека |

81Н |

07 | ||||||||||||||||

|

DPTR |

Регістр-вказівник даних: DPH - старший байт DPL – молодший байт |

83Н 82H |

00 00 | ||||||||||||||||

|

P0* |

|

80Н |

0FFH | ||||||||||||||||

|

P1* |

Порт 1

|

90Н |

0FFH | ||||||||||||||||

|

P2* |

Порт 2

|

0А0Н |

0FFH | ||||||||||||||||

Продовження таблиці 3.2.

|

1 |

2 |

3 |

4 | |||||||||||||||||

|

P3* |

Порт 3

|

0В0Н |

0FFH | |||||||||||||||||

|

IP* |

Регістр пріоритетів

|

0В8Н |

xx000000B | |||||||||||||||||

|

IE* |

Регістр маски переривань

|

0А8Н |

0x000000B | |||||||||||||||||

|

TMOD |

Регістр режиму таймера/лічильника

|

89Н |

00 | |||||||||||||||||

|

TCON* |

Регістр керування/статусу таймерів

|

88Н |

00 | |||||||||||||||||

|

TH0 |

Таймер 0 (старший байт) |

8СН |

00 | |||||||||||||||||

|

TL0 |

Таймер 0 (молодший байт) |

8АН |

00 | |||||||||||||||||

|

TH1 |

Таймер 1 (старший байт) |

8DН |

00 | |||||||||||||||||

|

TL1 |

Таймер 1 (молодший байт) |

8BН |

00 | |||||||||||||||||

|

SCON* |

Регістр керування приймачем-передавачем

|

98Н |

00 | |||||||||||||||||

|

SBUF |

Буфер приймачів-передавачів |

99Н |

хx | |||||||||||||||||

|

PCON |

Регістр керування потужністю

|

87Н |

0xxxxxxx | |||||||||||||||||

*Примітка. Позначені регістри припускають адресацію окремих бітів

Резидентна пам’ять даних адресується 8-розрядними регістром адреси (РА) або вказівником стека (SP), (рис.3.1). Регістр адреси є програмно-недоступним регістром, в який завантажується адреса комірки ОЗП під час виконання команд. Регістр SP призначений для адресації стека, який є частиною РПД. Вміст SP інкрементується перед запам’ятовуванням даних у стеку за командами PUSH і CALL і декрементується за командами POP і RET. Подібний спосіб адресації елементів стека називають передінкрементним/постдекрементним. У процесі ініціалізації ОМК після надходження сигналу RESET у SP автоматично завантажується код 07Н. Це означає, що, якщо програма не перевизначає стек, то перший байт даних у стеку буде розташований у комірці РПД з адресою 08Н.

Резидентна пам’ять данних, так само як і РПП, може бути розширена до 64 Кбайт під’єднанням зовнішніх ВІС.

Блок керування складається з генератора (Г) тактових сигналів, програмно-недоступного регістра команд (РК) та схеми керування і синхронізації (СК і С). Структурну схему блока керування показано на рис. 3.5.

Рис. 3.5 – Структурна схема блока керування

Код команди, зчитаної з РПП, запам’ятовується у 8-розрядному РК і надходить на дешифратор команд (ДШК), який входить до складу СК і С. Дешифратор команд формує 24-розрядний код, що надходить на програмовну логічну матрицю (ПЛМ), а після цього – на блок логіки керування.

Блок логіки керування

на підставі декодованого коду команди,

зовнішніх керуючих сигналів

![]() (сигналу

загального скидання),

(сигналу

загального скидання),![]() (сигналу блокування роботи з РПП), та

сигналів від внутрішнього формувача

імпульсів синхронізації виробляє

внутрішні сигнали керування.

(сигналу блокування роботи з РПП), та

сигналів від внутрішнього формувача

імпульсів синхронізації виробляє

внутрішні сигнали керування.

Внутрішній формувач імпульсів синхронізації формує: 1) внутрішні сигнали синхронізації машинних циклів; 2) вихідний сигнал дозволу фіксації адреси ALE; 3) сигнал дозволу програмної пам’яті PME (формується тільки при роботі із зовнішньою пам’яттю). Машинний цикл (рис. 3.6) має фіксовану тривалість і містить шість станів – S1-S6, кожний з яких за тривалістю відповідає одному такту.

Рис. 3.6 – Діаграма формування машинних циклів ОМК

Кожний стан або такт складається з двох фаз – Р1 і Р2. Тривалість фази дорівнює періоду сигналу Q, який формується або вбудованим (внутрішнім) тактовим генератором (рис. 3.7) при під’єднанні до виводів 18 (Х2) та 19 (Х1) ОМК кварцового резонатора (рис. 3.8,а) або LC-ланцюга (рис. 3.8,б), або зовнішнім джерелом тактових сигналів (рис. 3.9).

|

а |

б |

Рис. 3.7 – Принципові схеми внутрішніх тактових генераторів:

а – n-MДH технологія; б – КМДН-технологія

|

С1,

С2

30 |

|

|

а |

б |

Рис. 3.8 – Зовнішні ланцюги внутрішнього тактового генератора:

а – під’єднання кварцового резонатора; б – під’єднання LC-ланцюга

Рис. 3.9 – Під’єднання зовнішнього джерела тактових сигналів: а – для n-МДН; б – для КМДН

Частота імпульсів генератора для схеми на рис. 3.8, а визначається як

де ![]()

СРР![]() 10

пФ – ємність виводу.

10

пФ – ємність виводу.

Під’єднання зовнішнього джерела тактових сигналів до ОМК, виконаних за n-МДН (див. рис.3.9, а) та КМДН (див. рис.3.9, б) технологіями, відрізняється тим, що у першому випадку зовнішні імпульси синхронізації надходять на виводи 18(XTL2) та 19(ХTL1). У другому випадку зовнішні синхроімпульси надходять на виводи 19(ХTL1) та 20(спільний), а вивід 18(ХTL2) залишається непід’єднаним.

П ри

частоті кварцового резонатора або

тактовій частоті зовнішніх імпульсів

синхронізації частоті 12 МГц тривалість

машинного циклу дорівнює 1 мкс.

ри

частоті кварцового резонатора або

тактовій частоті зовнішніх імпульсів

синхронізації частоті 12 МГц тривалість

машинного циклу дорівнює 1 мкс.

Параметри

зовнішніх імпульсів синхронізації

![]() мГц

для частоти показано на рис. 3.10.

мГц

для частоти показано на рис. 3.10.

Рис. 3.10 – Параметри зовнішніх імпульсів синхронізації

У блок керування входить також регістр керування споживанням PCON (Power CONtrol).

Порти введення-виведення Р0-Р3 (див. рис.3.1) призначені для забезпечення побайтного обміну інформацією ОМК із зовнішніми пристроями по 32 лініях введення-виведення. Принципові схеми ліній портів Р0-Р3 показано на рис. 3.11,а-г відповідно. Кожна лінія порту містить керований регістр-фіксатор, два буфери і вихідний транзисторний каскад. Рівні вхідних і вихідних сигналів портів відповідають стандарту ТТЛ-логіки. Будь-яку лінію портів можна використовувати для введення або виведення інформації незалежно від інших ліній.

Для того, щоб лінія порту використовувалася для введення, у відповідний D-тригер регістра-фіксатора має бути записана логічна одиниця, що закриває МДН-транзистор вихідного каскаду.

Фізичні адреси портів:

Р0 – 80Н, при бітовій адресації 80Н-87Н;

Р1 – 90Н, при бітовій адресації 90Н-97Н; Р2 – А0Н, при бітовій адресації А0Н-А7Н;

Р3 – В0Н, при бітовій адресації В0Н-В7Н.

Порт Р0 є двонапрямленим, оскільки через нього можна в будь-який момент вводити та виводити інформацію. Виводи порта Р0 мають три стани. Через порт Р0:

виводиться молодший байт адреси А7-А0 при роботі із зовнішнім ПЗП і зовнішнім ОЗП;

видається з ОМК та приймається у ОМК байт даних при роботі із зовнішньою пам’яттю, при цьому обмін байтом даних та виведення молодшого байта адреси зовнішньої пам’яті мультиплексовано у часі;

задаються дані при програмуванні внутрішнього ПЗП EPROM.

Порти Р1-Р3 є квазідвонапрямленими, оскільки в будь-який момент через порти можна тільки виводити інформацію. Для введення інформації необхідно записати у всі розряди регістра-фіксатора логічні одиниці. Після цього можна виконувати введення.

Через порт Р1:

задається молодший байт адреси при програмуванні внутрішнього ПЗП EPROM та при читанні внутрішнього ПЗП.

Через порт Р2:

виводиться старший байт адреси А15-А8 при роботі із зовнішнім ПЗП і зовнішнім ОЗП у тих випадках, коли адреса є 16-розрядною;

задається старший байт А15-А8 адреси при програмуванні внутрішнього ПЗП EPROM та при читанні внутрішнього ПЗП.

Порт Р3 може використовуватись як для введення-виведення інформації, так і для реалізації альтернативних функцій обміну інформацією (див. рис.3.11). Альтернативні функції наведені в табл. 3.3. Кожну з восьми ліній порту Р3 користувач може запрограмувати на виконання альтернативних функцій записом одиниці у відповідні біти регістра-замка (Р3.0-Р3.7) порта Р3.